本文主要是Lattice公司市场总监Shakeel Peera给大家谈面对竞争激烈的FPGA市场,Lattice公司将持续优化FPGA成本和功耗。

2012-08-14 14:12:55 783

783

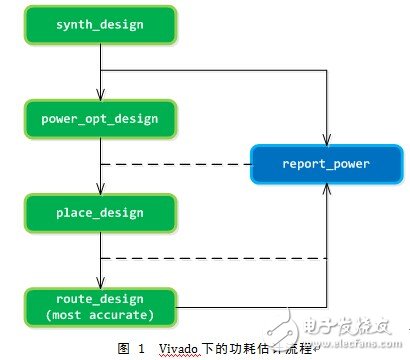

的技巧。本文提出的方法用于架构设计和前段设计的初期,如功耗估计、低功耗架构优化和时钟门控等。##功耗的估算##功耗的优化##架构考虑及RAM的功耗优化##时钟树单元/连线##时序分析##测试结果

2014-03-25 09:58:50 14624

14624 根据BPSK调制信号调制机理和平方倍频法原理,在FPGA平台上设计实现了BPSK调制信号载波频率估计单元。

2014-09-01 11:26:40 2585

2585 以下是笔者一些关于FPGA功耗估计和如何进行低功耗设计的知识。##关于FPGA低功耗设计,可从两方面着手:1)算法优化;2)FPGA资源使用效率优化。

2014-12-17 09:27:28 9177

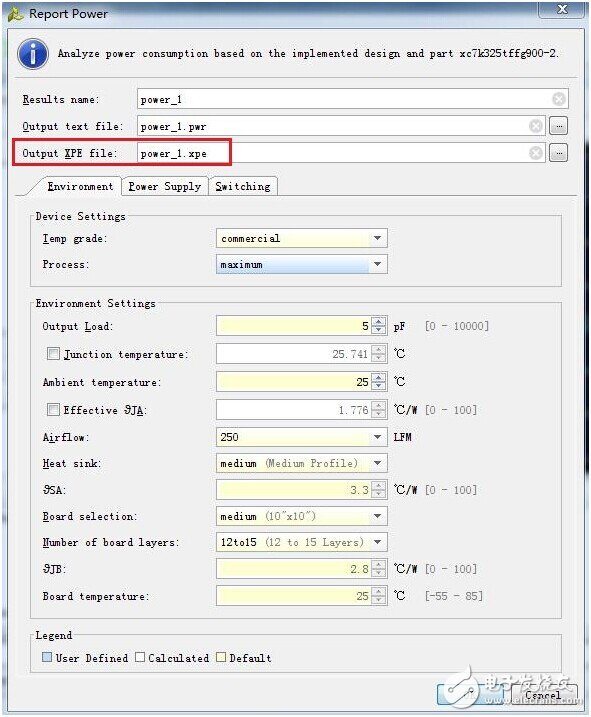

9177 在项目设计初期,基于硬件电源模块的设计考虑,对FPGA设计中的功耗估计是必不可少的。笔者经历过一个项目,整个系统的功耗达到了100w,而单片FPGA的功耗估计得到为20w左右,有点过高了,功耗过高

2017-12-19 09:29:14 6278

6278

基于FPGA vivado 17.2 的数字钟设计

2018-06-08 09:41:47 10186

10186

仿真功能概述 仿真FPGA开发中常用的功能,通过给设计注入激励和观察输出结果,验证设计的功能性。Vivado设计套件支持如下仿真工具:Vivado Simulator、Questa、ModelSim

2020-12-31 11:44:00 4723

4723

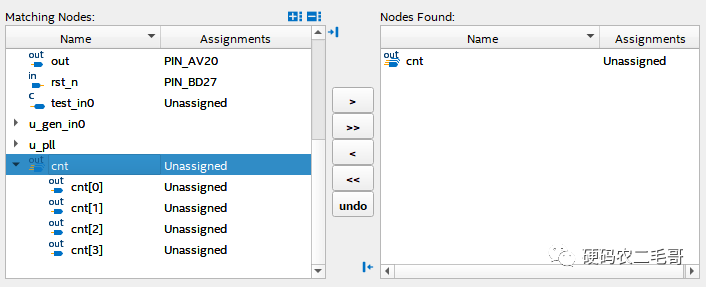

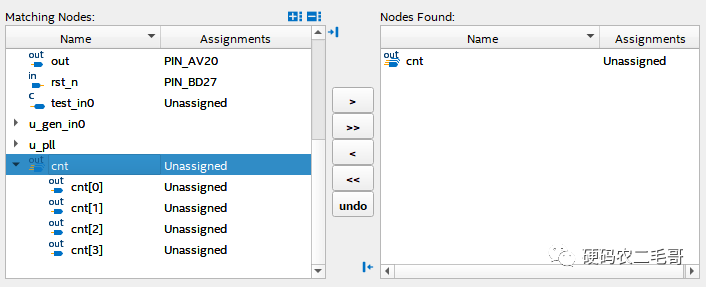

本文分别对quartus和vivado防止信号被优化的方法进行介绍。

2023-05-25 11:25:46 1887

1887

双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 403

403

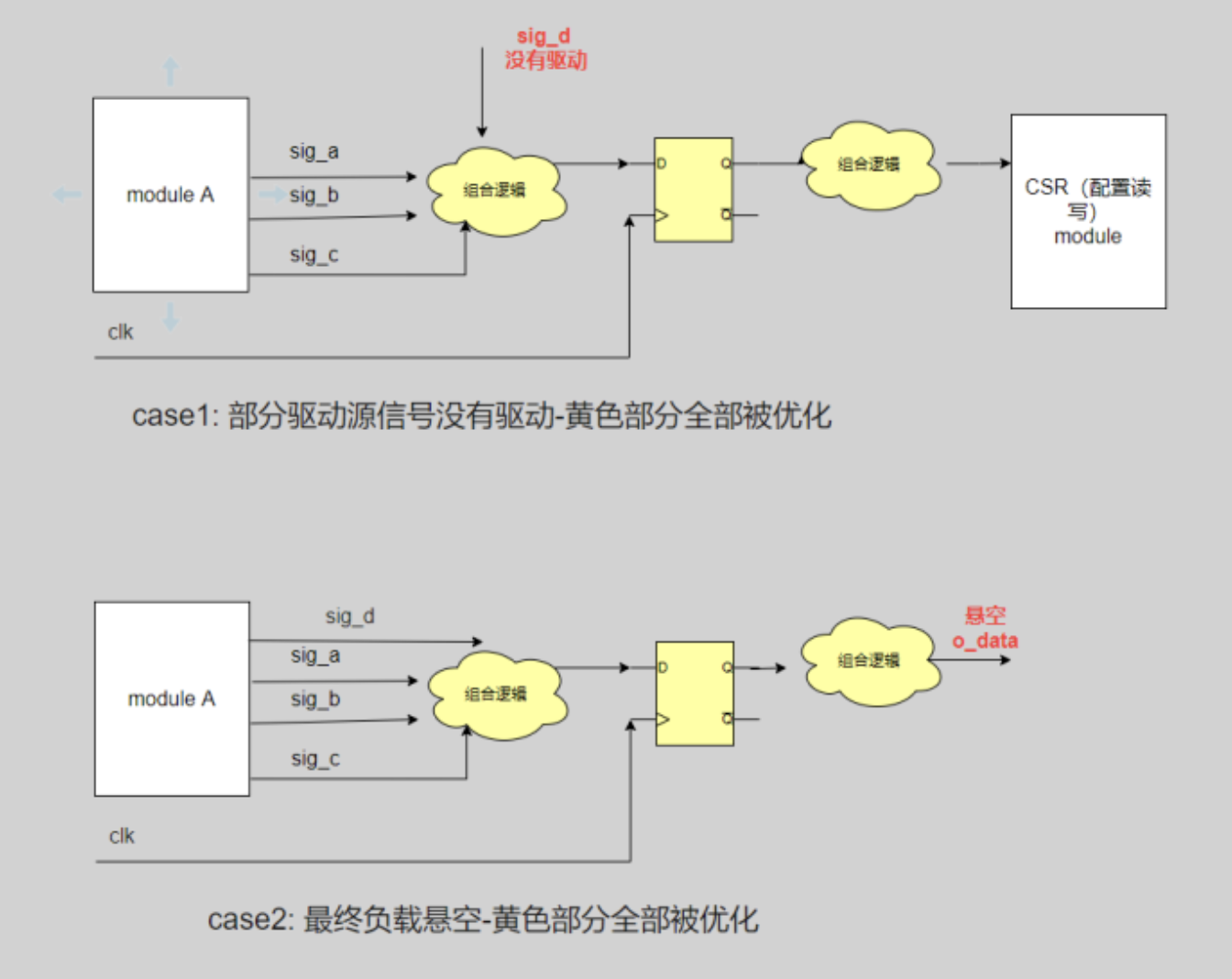

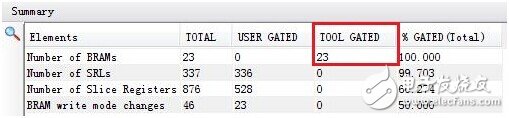

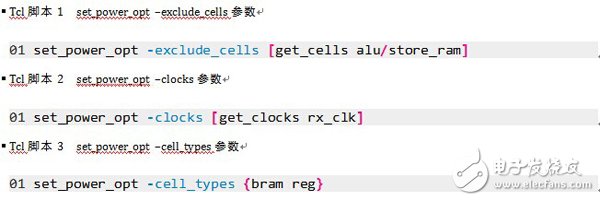

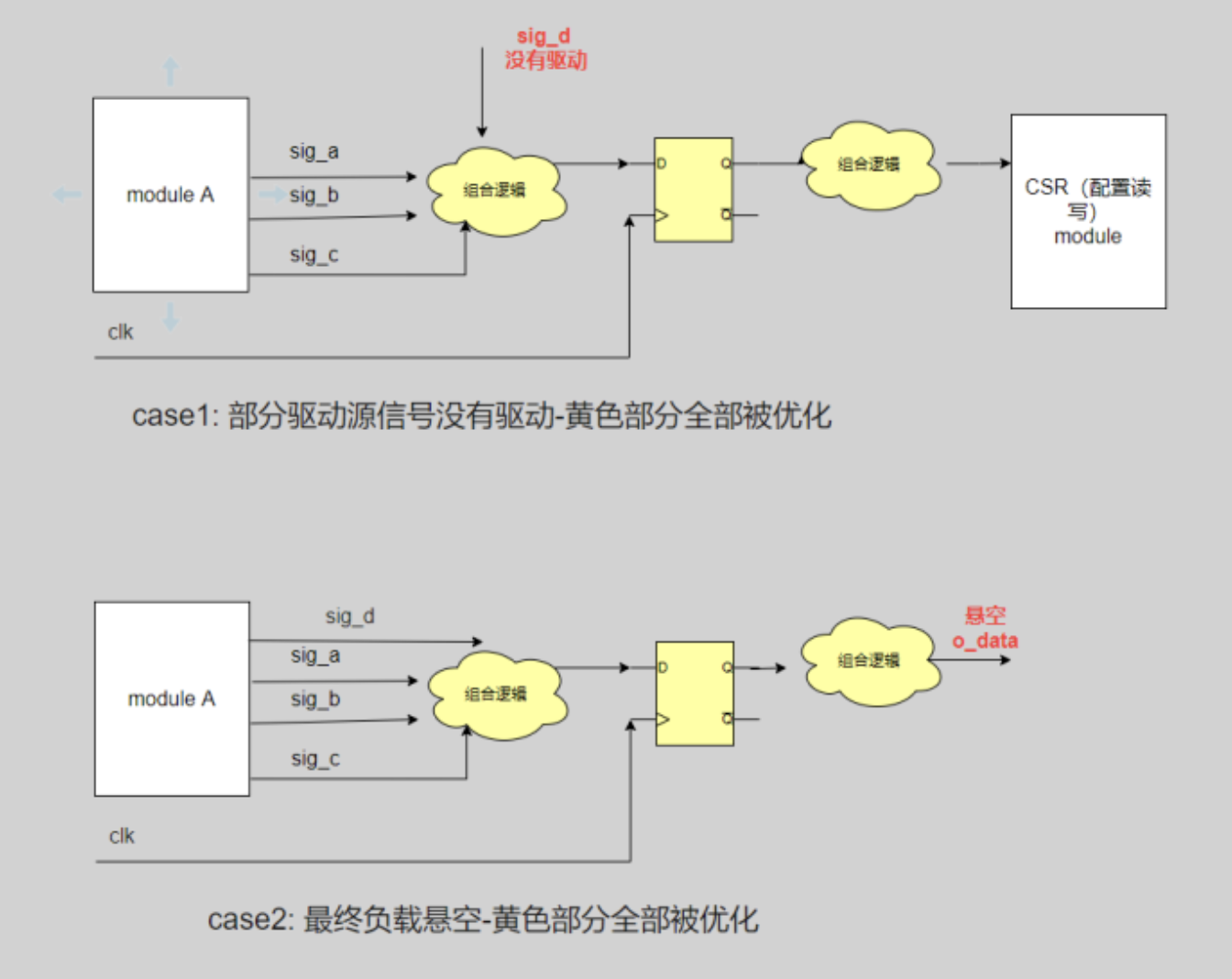

在项目初期,在使用FPGA工具quartus或者vivado生成版本烧入开发板进行调试时(DC开启优化选项后同样会优化掉寄存器),我们有时会发现部分寄存器被优化掉了,今天简单聊聊被优化的几种情况。

2023-09-08 15:09:59 1221

1221

FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能够做到如此低的功耗是因为什么?

2021-04-30 06:08:49

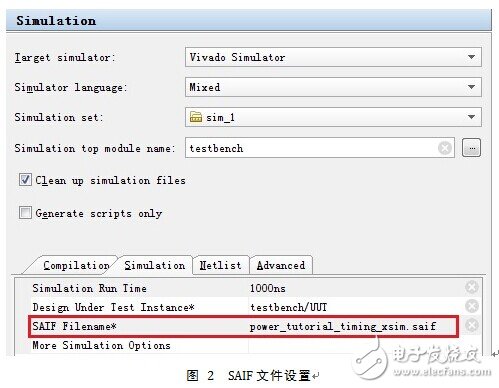

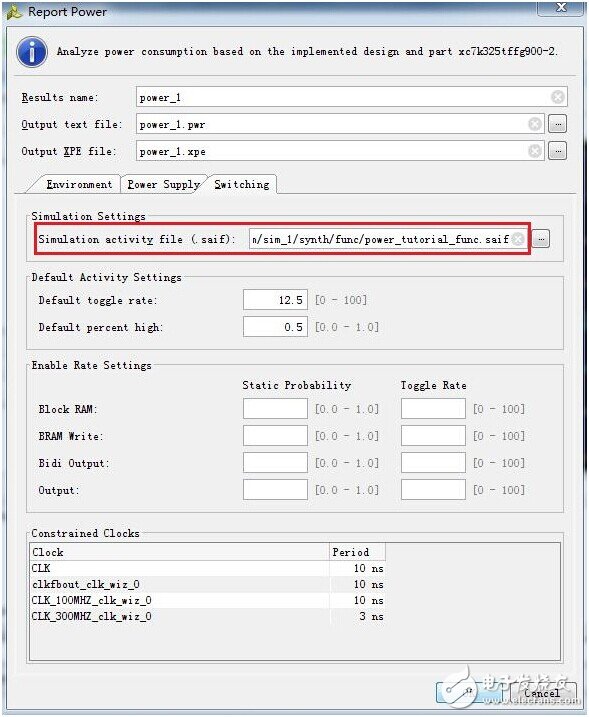

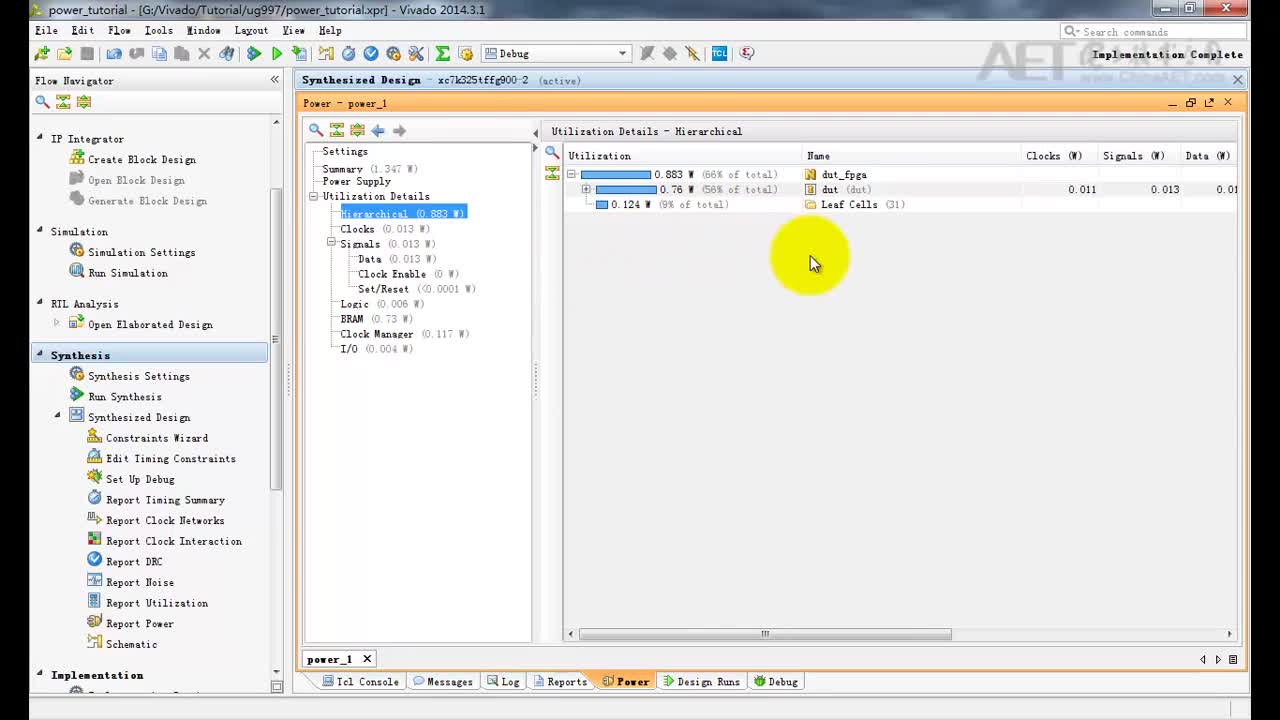

,IP,BUFG的Estimated Utilization,请问表示什么内容?③查到在Vivado下进行功耗估计有两种方法,一种是向量模式,需要提供SAIF(Switching Activity

2018-02-25 16:03:46

Utilization的图表,内有LUT,FF,IP,BUFG的Estimated Utilization,请问表示什么内容?③查到在Vivado下进行功耗估计有两种方法,一种是向量模式,需要提供SAIF

2018-02-25 21:12:01

是90nm的1.2 V器件,与先前产品相比可降低静态和动态功耗,且FPGA制造商采用不同的设计技术进一步降低了功耗,平衡了成本和性能。这些90nm器件都改变了门和扩散长度,优化了所需晶体管的开关速率

2015-02-09 14:58:01

和多种高速SERDES信道,不仅静态和动态功耗也随之增加,对FPGA设计的电源要求也非常复杂,这对系统功耗要求提出更多挑战,尽可能地估算和优化FPGA的功耗成为应对挑战的关键。 FPGA的主要功耗

2018-10-23 16:33:09

EDA技术具有什么特征?FPGA是什么原理?FPGA设计应用及优化策略基于VHDL的FPGA系统行为级设计

2021-04-15 06:33:58

学习。个人学习的时候可以根据实际情况选择最高至Vivado2019.1。(从Vivado2019.2开始,PS开发使用Vitis,没有SDK了)第1章 FPGA技术分析 / 11.1 FPGA内部结构

2020-10-21 18:24:48

嗨,在网络实施期间,当我将用户ILA端口从3个端口扩展到11个端口时,会生成以下消息:[Vivado_Tcl 4-131] Power Optimization遇到异常:ERROR:[Common

2018-11-08 11:29:12

如上图所示用的是Vivado2014.4,最后生成完bit文件后,显示了这个。结温过高?仔细看report里面电流竟然30+A。。。我想问一下大概是什么原因导致了这种状况的出现呢,然后解决这个问题那些地方的代码可以优化呢?刚学FPGA不久,望各位大虾指教

2015-03-23 17:01:15

转自:VIVADO时序分析练习时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习VIVADO软件时序分析的笔记,小编这里

2018-08-22 11:45:54

大家好。我设计并模拟了简单的RTL with Block RAMin Kintex 7。在合成和实现之后,vivado用于功率估计。当我使用分布式RAM时,会正确报告每个RAM的功耗。但是

2019-03-13 14:21:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

无论从微观到宏观、从延长电池寿命到减少全球变暖的温室效应等等,各种不同因素都在迅速推动系统设计人员关注节能问题。一项有关设计优先考虑事项的最新调查指出,大部分工程师已把功耗排在首位,或者是将其紧跟在性能、密度和成本之后。在功耗方面,FPGA带来了独特的挑战。为什么要设计优化FPGA功耗?

2019-08-08 07:39:45

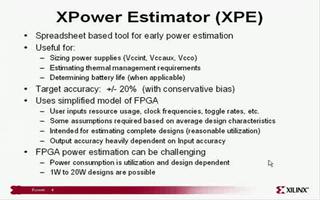

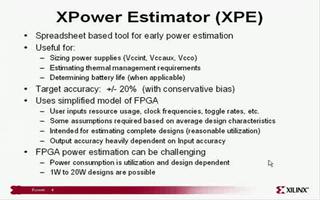

是在映射或布局和布线后设计的基础上对器件功耗进行估计的。 对于成熟的投产的 FPGA 和 CPLD,XPower 计算出的功耗估计的平均设计批量误差 (suite error) 小于 10%。它将

2012-01-11 11:59:44

嗨,来自Altera Quartus背景后,我是Vivado工具流程的新手。我正在使用Vivado 2017.2。我试图弄清楚为什么地点和路线(实施)阶段已经优化了在合成阶段之后仍然存在的一堆逻辑

2018-11-07 11:35:44

【流水灯样例】基于 FPGA Vivado 的数字钟设计前言模拟前言Vivado 设计流程指导手册——2013.4密码:5txi模拟

2022-02-07 08:02:04

基于FPGA vivado 17.2 的数字钟设计目的:熟悉vivado 的开发流程以及设计方法附件:

2017-12-13 10:16:06

芯片设计解决方案供应公司微捷码(Magma)设计自动化有限公司近日宣布,已和专为消费性应用提供超低功耗65纳米FPGA(现场可编程门阵列)技术的先驱者SiliconBlue科技公司正式签定技术合作

2019-07-26 07:29:40

如何使用优化的数据包软件降低网络功耗?

2021-05-25 06:45:33

你好ISE的合成与实现,最终资源利用分析报告正常。现在在Vivado中,在实现逻辑优化(opt_design)的第一步(实现)中投入了大量资源来优化模块(建议逻辑单元不加载),但是当ISE实现没有被

2018-10-24 15:23:00

怎么实现基于LFSR优化的BIST低功耗设计?

2021-05-13 06:21:01

大家好我是刚刚来这的实习生(拱手)。最近在看 基于FPGA的H264运动估计算法优化与实现 方面的东西,他提出了一个概念:运动矢量。这是如何得到的?如何理解?有什么用?附录原文中的一些东西:基于块

2015-04-28 11:51:04

的:1)降低θJA:热阻抗取决于芯片与环境的热传导效率,可通过加散热片或者风扇减小热阻抗图12)减小PD:通过优化FPGA设计,降低总功耗,这也是本文重点讲解的部分。2.功耗估计在讲解低功耗设计之前,介绍

2014-08-21 15:31:23

您好Xilinx的用户和员工,我们正在考虑购买Zynq 7000用于机器视觉任务。我们没有编程FPGA的经验,并希望使用Vivado HLS来指导和加速我们的工作。关于这种方法的一些问题:您对

2020-03-25 09:04:39

`Hi,我来自一个叫Plunify的工程师团队,一直致力于使用机器学习来优化时序。把云计算应用到 FPGA 的概念最近刚兴起,亚马逊云的F1实例也受到越来越多的关注。趁着赛灵思和亚马逊开始合作推出

2017-11-22 10:51:18

给设计F2812电源电路,不知道F2812的功耗如何估计?我知道FPGA芯片厂商有对应的EXCEL表可以估计芯片的功耗,不知道DSP有没有这样的工具?大家平时是如何估计DSP的功耗的?

2018-11-22 10:07:12

嗨,我发现Vivado webpack版本v2014.4不支持安装在NetFPGA SUME板上的eh Virtex-7 690 FPGA。我想知道购买NetFPGA SUME板的任何许可证捆绑

2018-12-18 10:36:47

FPGA怎么选择?针对功耗和I/O而优化的FPGA介绍

2021-05-06 09:20:34

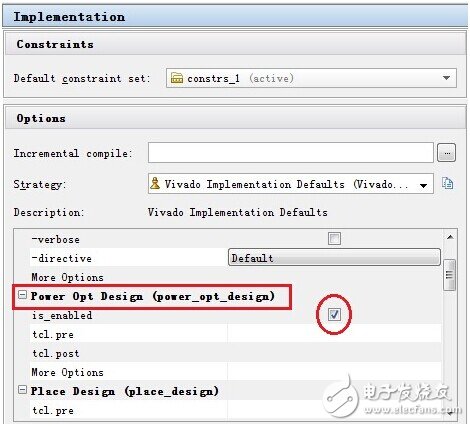

(1)门级电路的功耗优化综述 门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化以满足功耗的约束,同时

2021-11-12 06:14:26

主要讲解了fpga设计、方法和实现。这本书略去了不太必要的理论、推测未来的技术、过时工艺的细节,用简明、扼要的方式描述fpga中的关键技术。主要内容包括:设计速度高、体积小、功耗低的体系结构方法

2012-03-01 14:59:23

针对色噪声背景下MIMO块平坦衰落信道进行了估计和优化,并以信道估计的优化结果为基础,分析了估计信道的互信息量下限和系统的容量下限,提出了利用注水算法来优化发射端

2009-05-10 11:46:36 17

17 本文将介绍FPGA的功耗、流行的低功耗功能件以及影响功耗的用户选择方案,并探讨近期的低功耗研究,以洞察高功率效率FPGA的未来趋势。

功耗的组成部分

2010-08-27 10:57:21 1637

1637

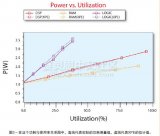

自从Xilinx推出FPGA二十多年来,研发工作大大提高了FPGA的速度和面积效率,缩小了FPGA与ASIC之间的差距,使FPGA成为实现数字电路的优选平台。今天,功耗日益成为FPGA供应商及其客户关注的问题。降低FPGA功耗是缩减封装和散热成本、提高器件可靠性以及打开移

2011-03-15 14:58:34 31

31 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 改进粒子群优化在压缩感知DOA估计中的应用_赵宏伟

2017-01-07 18:39:17 0

0 一种优化高斯粒子滤波的载波频偏估计算法_焦玲

2017-01-07 18:56:13 1

1 参加 FPGA 功率优化班,将帮助您创建更高电源效率的 FPGA 设计。通过本课程的学习,将有助于您的设计满足更小型化的 FPGA 器件,降低 FPGA 功耗,或在更低的温度下运行

2017-02-09 06:24:11 167

167 随着xilinx公司进入20nm工艺,以堆叠的方式在可编程领域一路高歌猛进,与其配套的EDA工具——新一代高端FPGA设计软件VIVADO也备受关注和饱受争议。

2017-02-11 19:08:00 4986

4986 有关FPGA——VIVADO15.4开发中IP 的建立

2017-02-28 21:04:35 15

15 有一种新方法可用于测量真实FPGA器件的功耗估计值 现代的FPGA 芯片能够开发高性能应用,但在这些设计中电源管理通常是一大限制因素。FPGA 器件的资源使用最能决定设计的容量和处理速度,但是增加

2017-11-18 01:14:02 5406

5406

Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握

2017-11-18 03:52:01 4675

4675

为设计寻找“完美”FPGA 的重要性日渐升级,其中功耗已成为主要考虑因素。功耗管理在大部分应用中都非常关键。某些标准已为单卡或者单个系统设定了功耗上限。鉴于此,设计人员必须在设计过程中更早地对功耗

2017-11-22 15:03:01 2573

2573 FPGA与众多其它类型组件的不同之处在于,其核心电压、辅助电压和I/O电压电源需求取决于设计实现。因此,确定应用中FPGA的功耗比数据手册描述的情况更复杂一点,要实现正确的电源架构因此也具有一定

2018-07-19 18:01:00 1645

1645

设计者通过优化自己的设计和注意某些具体情况,可以在FPGA设计中实现低功耗。通过一款具体的FPGA产品了解其低功耗的解决方式,为设计提供了指导。FPGA均可在相应的操作环境下进行仿真,从而了解功耗

2017-11-23 10:37:23 1248

1248 本文首先与实测系统功耗进行对比,验证了Xilinx公司ISE软件包中FPGA功耗估算工具XPower的准确性。然后对FPGA设计中影响系统功耗的几个相互关联的参数进行取样,通过软件估算不同样点下的系统功耗,找到功耗最低的取样点,得到最佳设计参数,从而达到优化系统设计的目的。

2017-11-25 09:26:44 1551

1551 本视频演示了 Xilinx 功耗估计器电子数据表工具

2018-06-05 13:45:00 7081

7081

本演示中,我们将介绍利用 XPower 估计器(XPE)工具精确估计 Virtex®-5 器件的功耗所需的步骤。我们还通过在 ML550 开发板 - 进行详细的功耗测量的首选平台 - 上进行测量演示了 Virtex®-5 器件的低功耗特性。

2018-06-06 02:45:00 2951

2951

估计得到为20w左右,有点过高了,功耗过高则会造成发热量增大,温度高最常见的问题就是系统重启,另外对FPGA内部的时序也不利,导致可靠性下降。其它硬件电路的功耗是固定的,只有FPGA的功耗有优化的余地,因此硬件团队则极力要求笔者所在的FPGA团队尽量多做些低功

2018-09-07 14:58:01 381

381 Vivado不仅是xlinx公司的FPGA设计工具,用它还可以学习Verilog描述,你造吗?

2018-09-20 09:29:22 9427

9427 我们以8-bit 的LFSR(线性反馈移位寄存器)做一个流水灯为例,介绍Vivado的基本使用。

2018-09-25 16:16:36 14476

14476

单片机是基于FLASH结构的,所以单片机上电直接从本地FLASH中运行。但SRAM 架构的FPGA是基于SRAM结构的,掉电数据就没了,所以需要借助外部电路来配置运行的数据,其实我们可以借助Vivado来学习FPGA的各种配置模式。

2018-11-05 15:12:57 7298

7298 物理优化是Vivado实现流程中更快时序收敛的重要组成部分。

了解如何在Vivado中应用此功能以交换运行时以获得更好的设计性能。

2018-11-23 06:06:00 3728

3728 本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:06:00 2166

2166

Tcl介绍 Vivado是Xilinx最新的FPGA设计工具,支持7系列以后的FPGA及Zynq 7000的开发。与之前的ISE设计套件相比,Vivado可以说是全新设计的。无论从界面、设置、算法

2020-11-17 17:32:26 2112

2112 Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP

2020-12-29 15:59:39 9496

9496 功耗是各大设计不可绕过的话题,在各大设计中,我们应当追求低功耗。为增进大家对低功耗的认识,本文将对FPGA低功耗设计予以介绍。如果你对FPGA低功耗相关内容具有兴趣,不妨继续往下阅读哦。 FPGA

2020-10-28 15:02:13 2498

2498 EE-308:估计和优化Blackfin®处理器的引导时间

2021-04-13 13:56:59 0

0 基于粒子群优化的电力系统状态向量估计

2021-06-19 14:35:00 8

8 赛灵思近日宣布推出 Vivado ML 版,这是业内首个基于机器学习(ML )优化算法以及先进的面向团队协作的设计流程打造的 FPGA EDA 工具套件,可以显著节省设计时间与成本,与目前

2021-07-02 16:40:13 2403

2403

(1)门级电路的功耗优化综述 门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化以满足功耗的约束,同时

2021-11-07 11:05:59 19

19 【流水灯样例】基于 FPGA Vivado 的数字钟设计前言模拟前言Vivado 设计流程指导手册——2013.4密码:5txi模拟

2021-12-04 13:21:08 26

26 笔者经历过一个项目,整个系统的功耗达到了100w,而单片FPGA的功耗估计得到为20w左右,有点过高了,功耗过高则会造成发热量增大,温度高最常见的问题就是系统重启,另外对FPGA内部的时序也不利,导致可靠性下降。

2022-09-19 16:13:21 1465

1465 Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。

2022-09-19 16:20:51 1309

1309 XKF3 - 使用惯性和磁感应的 3D 方向的低功耗优化估计

2022-11-14 21:08:29 0

0 对于FPGA来说,设计人员可以充分利用其可编程能力以及相关的工具来准确估算功耗,然后再通过优化技术来使FPGA和相应的硬件设计满足其功耗方面的要求。

2022-12-29 14:46:14 928

928 与现有的中端FPGA相比,得益于专为低功耗设计的可编程结构、功耗优化的嵌入式存储器和DSP、低功耗高性能SERDES与I/O设计、内置协议逻辑等全方位优化措施,Avant系列产品的功耗比同类竞品器件低2.5倍。

2023-01-04 11:32:11 342

342 有一天使用Vivado调用questasim(modelsim估计也一样),仿真报错

2023-05-08 17:12:56 1759

1759 本文主要介绍Vivado布线参数设置,基本设置方式和vivado综合参数设置基本一致,将详细说明如何设置布线参数以优化FPGA设计的性能,以及如何设置Vivado压缩BIT文件。

2023-05-16 16:40:45 2957

2957

点击上方 蓝字 关注我们 FPGA 高级设计之实现功耗优化 与ASICs(Application Specific Integrated Circuits)比较,相似的逻辑功能,用FPGA来实现

2023-05-19 13:50:02 815

815 电子发烧友网站提供《在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑.zip》资料免费下载

2023-06-15 09:14:49 0

0 FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-26 15:29:05 531

531

电子发烧友网站提供《Vivado设计套件用户指南之功耗分析和优化.pdf》资料免费下载

2023-09-14 10:25:07 0

0 电子发烧友网站提供《Vivado ML版中基于ML的路由拥塞和延迟估计.pdf》资料免费下载

2023-09-14 11:41:08 0

0 在项目初期,在使用FPGA工具quartus或者vivado生成版本烧入开发板进行调试时(DC开启优化选项后同样会优化掉寄存器),我们有时会发现部分寄存器被优化掉了,今天简单聊聊被优化的几种情况。

2023-09-26 09:47:49 455

455

电子发烧友网站提供《使用Vivado高层次综合(HLS)进行FPGA设计的简介.pdf》资料免费下载

2023-11-16 09:33:36 0

0 Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317

正在加载...

电子发烧友App

电子发烧友App

评论