电池鉴别

此为基本的大多数该品牌的鉴别方法,如遇到新出厂批次的电池在鉴别手段上会有所不同。

1. 诺基亚电池

方法一:真电池正面用手指摸没有

2010-11-30 11:21:13 1043

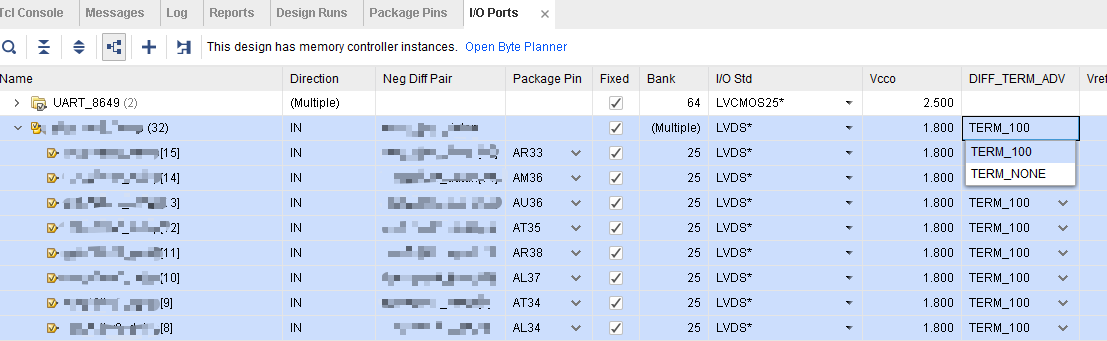

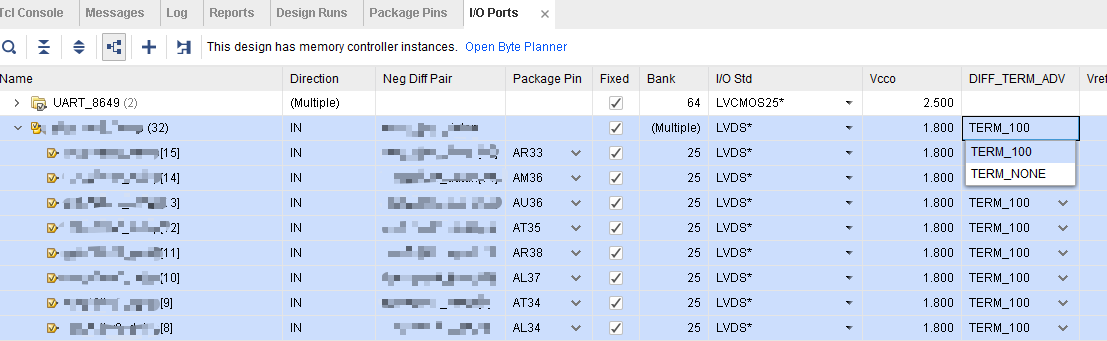

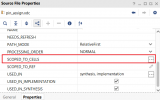

1043 ,后者指定了管脚对应的电平标准。 在vivado中,使用如下方式在xdc中对管脚进行约束。 set_property -dict {PACKAGE_PIN AJ16 IOSTANDARD

2020-10-30 16:08:13 13112

13112

对话框的约束部分下,选择默认约束设置作为活动约束设置;包含在Xilinx设计约束(XDC)文件中捕获的设计约束的一组文件,可以将其应用于设计中。两种类型的设计约束是: 1) 物理约束:这些约束定义引脚

2020-11-23 14:16:36 4238

4238

时序不满足约束,会导致以下问题: 编译时间长的令人绝望 运行结果靠运气时对时错 导致时序问题的成因及其发生的概率如下表: 由上表可见,造成时序问题的主要原因除了约束不完整,就是路径问题,本文就时序

2020-11-29 10:34:00 7410

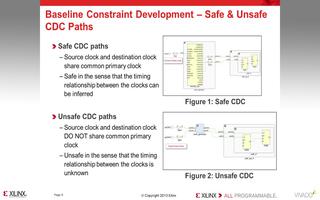

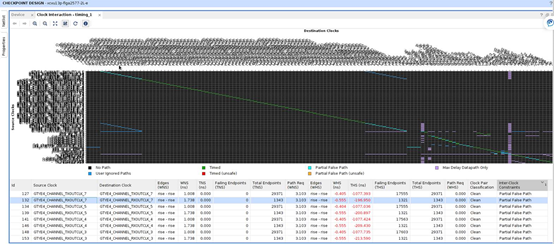

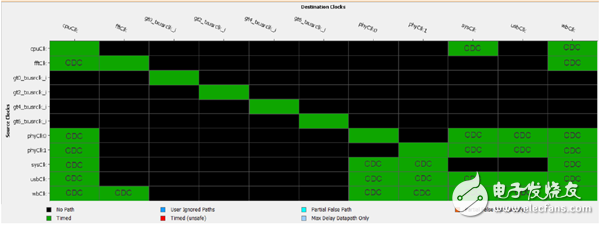

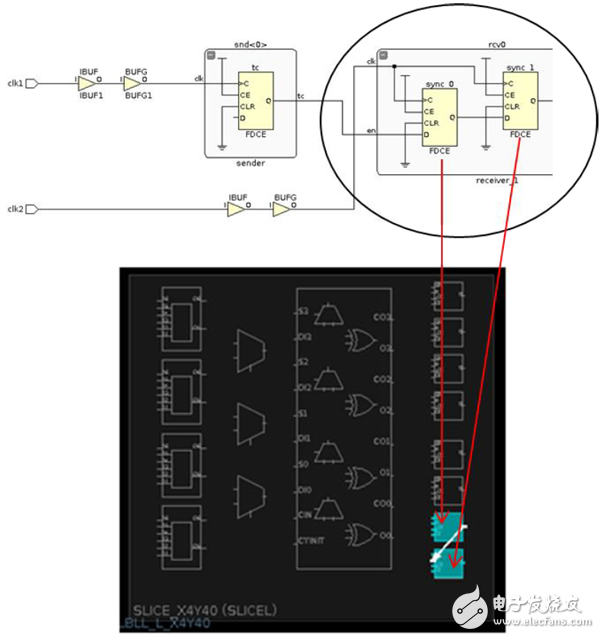

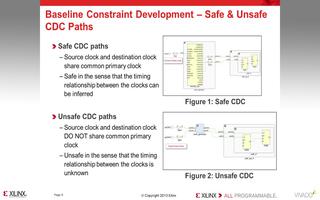

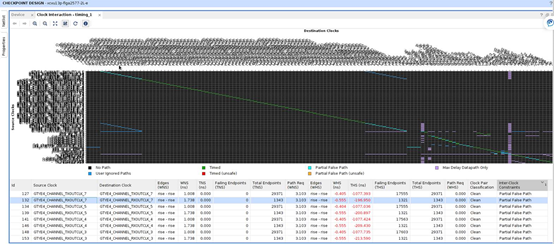

7410 跨时钟域路径分析报告分析从一个时钟域(源时钟)跨越到另一个时钟域(目标时钟)的时序路径。

2020-11-27 11:11:39 5449

5449

时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39:10 8731

8731 前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 868

868 时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50:02 452

452

systemverilog constraint中的foreach可以对数组进行遍历和约束,常用于普通数组,队列或者动态数组。

2023-08-21 09:31:07 809

809

使用这种约束。如何设计我的XDC文件?以上来自于谷歌翻译以下为原文Both the IDDR and the IOB FF are driven only by the IBUF in the same

2018-11-13 14:28:50

FPGA时序分析与约束(1)本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:Inter1、什么是时序分析?在FPGA中,数据和时钟传输路径是由相应的EDA软件通过针对特定器件的布局布线

2021-07-26 06:56:44

模块的每一个寄存器都得到了具体的布局位置约束。该模块的时序收敛也就相应地在每一次重新编译的过程中得到了保证。经过分析,这一子模块的设计和约束最初是在原理图中进行的,在达到时序收敛目标后该设计被转换为HDL语言

2017-12-27 09:15:17

,这一子模块的设计和约束最初是在原理图中进行的,在达到时序收敛目标后该设计被转换为HDL语言描述,相应的约束也保存到了配置文件中。 6. 核心频率约束+时序例外约束+I/O约束+特定路径延时约束 好

2016-06-02 15:54:04

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

一组合电路,从Trig_sig输入一个上升沿触发信号,这个信号分别通过两条路径:路径1(path_1[0]到path_1[64])和路径2(path_2[0]到path_2[64])。希望约束路径1和路径2的延时差绝对值尽量小(即约束路径1和路径2的延时相等),如何做? 谢谢!

2013-12-30 15:12:19

TS_FastPath = FROM clk_a TO clk_b 20 ns;而我们的违规路径多是从某个模块下的寄存器到另一个模块下的寄存器,时序分析报告中会给出具体的路径。在QII中可以针对这条路径进行多周期约束

2015-04-30 09:52:05

文件(XDC文件),它包含用于时序分析的“create_clock”和“set_input_jitter”约束。在ISE 14.7和Spartan-3 FPGA中,我可以使用称为“时钟向导”的IP来

2019-08-02 09:54:40

正确处理这些约束的方法。 例如,我的一个严重警告如下所示。消息显示'get_property'至少需要一个有效端点。set_max_delay -from [get_cells

2018-11-02 11:30:10

的设定。这两个约束比较简单,容易设定,但是非常关键。如果设定的不好,系统性能会大打折扣。false path 是指在时序分析中不考虑其延迟计算的路径。例如有些跨越时钟域的电路等。设定的方法

2012-03-05 15:02:22

#################### ################################################## ################################文件名:example_top.xdc ##详细信息:约束文件## FPGA系列:VIRTEX7 ## FPGA部件:XC7VX485T-FFG1761

2019-09-18 06:50:14

大部分的时序分析和约束都写在这里了。 一、基本时序路径1、clock-to-setup周期约束跨时钟域约束: (1)当源触发器和目标触发器的驱动时钟不同,且时钟的占空比不是50

2017-03-09 14:43:24

这样的设计:一个子模块的每一个寄存器都得到了具体的布局位置约束。该模块的时序收敛也就相应地在每一次重新编译的过程中得到了保证。经过分析,这一子模块的设计和约束最初是在原理图中进行的,在达到时序收敛目标后

2017-10-20 13:26:35

什么是时序路径和关键路径?常见的时序路径约束有哪些?

2021-09-28 08:13:15

时可以引用这个标识符,大大方便了派生时钟的定义。 一种特殊情况的周期约束是相关时钟。前面提到周期约束不会覆盖异步路径,如图1所示的D路径。但是如果两个时钟是“相关”的,则实现工具和时序分析工具会考

2015-02-03 14:13:04

在使用Vivado GUI实现和分配引脚信息后,我没有在xdc约束文件中看到结果。例如,引脚和iostandard。他们在哪里攒钱?以上来自于谷歌翻译以下为原文After

2018-11-07 11:24:10

我有一个问题让我的约束正常工作。我打开一个路由设计并转到我的计时错误。我突出显示我想设置为错误路径的一个错误,并从弹出菜单转到错误路径部分。我将假路径声明复制到TCL命令行框中,一切正常。我将

2020-08-14 09:47:34

当我们通过IP目录在Vivado中创建一些IP内核时,将使用xdc文件生成一些内核。在这个xdc文件中,它包括时序或物理约束。以DDR3控制器为例,用核心生成xdc文件。它包括时序约束和物理约束

2019-03-26 12:29:31

你好我目前正在使用外部多路复用器在Vivado 2017上开展一个项目。关于约束文件(.xdc),我有一个更普遍的问题。如何创建自己的xdc文件?通常,您是从完整的zedboard约束文件开始并自己

2020-05-22 10:27:47

的目标:多路复用输入到FIFO并使其正常工作。 (多路复用使用固定输入,但不使用不同的输入)。2.或者是否知道如何正确约束数据路径的延迟?我使用set_max_delay -from [FIR

2020-07-27 09:55:39

本文转载IC_learner - 博客园数字IC之路-SDC篇(一):基本的时序路径约束_u012675910的博客-CSDN博客_sdc约束 RTL代码描述了电路的时序逻辑和组合逻辑,即RTL代码

2022-03-01 06:48:09

变化,输出频率在输出时为浆果高(> 1MHz)我看到一个等于我的时钟幅度的恒定电压。下面是我的verilog代码和约束文件,可以;有人帮助我理解可能出错的地方模块main1(TX1,TX40

2019-08-01 09:38:02

XDC文件中设置maxdelay约束。 (摘自ug911:MAXDELAY:Vivado Design Suite在XDC中不支持此约束。)是否有解决方案在Vivado中替换此约束?感谢您的帮助或建议

2018-10-25 15:17:18

当逻辑行为以默认的方式不能正确的定时逻辑行为,想以不同的方式处理时序时,必须使用时序例外命令。1. 多周期路径约束指明将数据从路径开始传播到路径结束时,所需要的时钟周期

2018-09-21 12:55:34

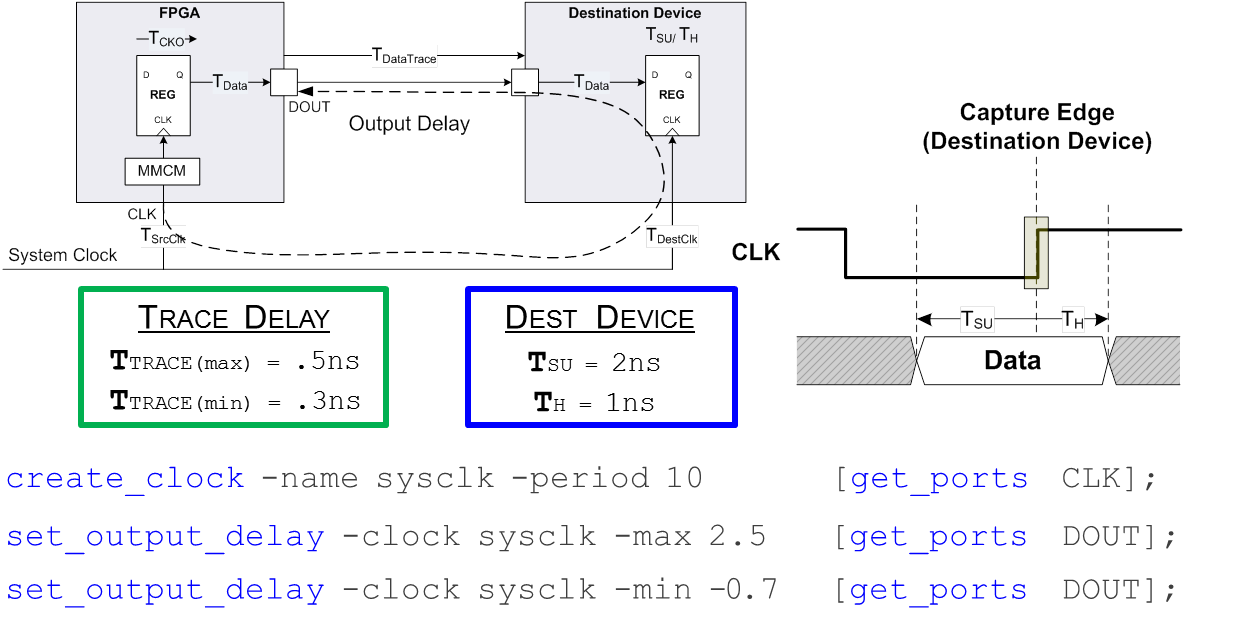

时序约束可以很复杂,这里我们先介绍基本的时序路径约束,复杂的时序约束我们将在后面进行介绍。在本节的主要内容如下所示:·时序路径和关键路径的介绍 ·建立时间、保持时间简述 ·时钟的约束(寄存器-寄存器之间的路径约束) ·输入延时的约束 ·输出延...

2021-07-26 08:11:30

求16.5安装方法和约束设置

2012-05-24 22:32:46

喜我对我的设计中的关键路径以及如何约束它们有疑问。我正在使用ISE 14.1进行实施。我有一个设计,其中关键路径(从源FD到目的地FD)给出-3.3ns的松弛(周期约束为10ns)。现在有没有其他方法

2019-04-08 08:58:57

能力的对比是可以区分出电化学电容器和 蓄电池的。双电层超级电容器与电化学超级电容器的鉴别 由于电化学超级电容器的特性与蓄电池非常相像,区鉴别双电层超级电容器和电化学超 级电容器的方法与双电层超级电容器

2011-10-13 10:29:13

该文基于谱图理论和流形学习提出了局部边界鉴别分析(LMDA)的降维方法。在近邻保持投影的基础上,LMDA 方法减少了同类数据间由于线性投影而带来的重构误差,同时保留了类内相似

2009-11-21 11:25:38 9

9 鉴别投影嵌入及其在人脸识别中的应用

该文提出了一种新的监督线性降维方法,称为鉴别投影嵌入(Discriminant Projection Embedding, DPE)。和常用的线性鉴别分析相比

2010-02-26 17:24:40 8

8 时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 如何鉴别可控硅的三个极

鉴别可控硅三个极的方法很简单,根据P-N结的原理,只要用万

2009-07-25 11:20:36 648

648

鉴别可控硅三个极的方法

鉴别可控硅三个极的方法很简单,根据P-N结的原理,只要用万用表测量一下三个极之间的电

2010-01-14 16:20:52 1038

1038 针对目前导航系统中重要的多约束条件下路径规划功能,结合A*算法和蚁群算法提出一种新的不确定算法,该算法首先将多约束条件进行融合使其适合蚁群转移,并在基本蚁群算法基础

2012-06-07 08:56:53 0

0 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 作者: 圆宵 FPGA那点事儿 在ISE时代,使用的是UCF约束文件。从Vivado开始,XDC成了唯一支持的约束标准。XDC除了遵循工业界的通行标准SDC(Synopsys Design

2017-02-08 02:10:50 4616

4616 最近有些朋友在ISE中做的V7项目需要切换到vivado来,但导入代码后,导入约束时,发现vivado不再支持UCF文件,如果手抄UCF约束到 VIVADO 的 XDC 约束,不仅浪费时间,而且容易出错,这里介绍一种方法可以实现两种约束的切换。

2017-03-24 13:54:36 8529

8529

的关系。工程师利用这类约束确定是否有必要对路径进行分析,或者在时钟路径之间不存在有效的时序关系时忽视路径。

2017-11-17 05:23:01 2417

2417

《XDC约束技巧》系列中讨论了XDC约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入Vivado中的XDC实际上就是用户设定的目标 ,Vivado对FPGA设计的实现

2017-11-17 18:03:55 34003

34003

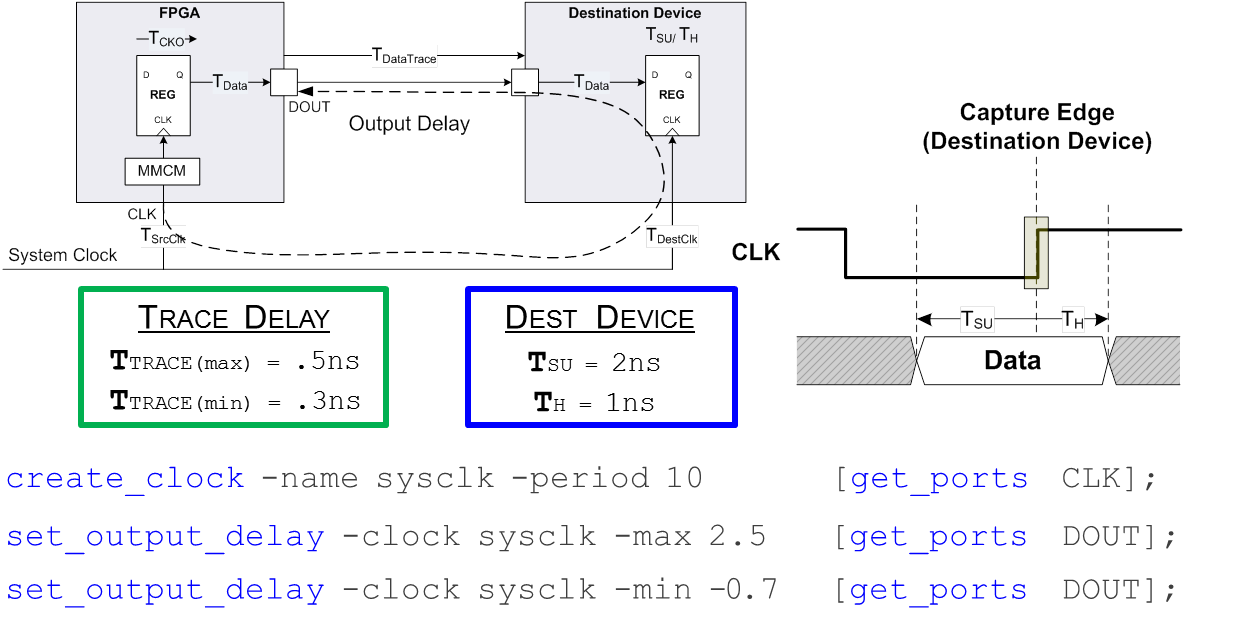

从UCF到XDC的转换过程中,最具挑战的可以说便是本文将要讨论的I/O约束了。 I/O 约束的语法 XDC 中可以用于 I/O 约束的命令包括 set_input_delay / set_output_delay 和set_max_delay / set_min_delay 。

2017-11-17 18:54:01 11853

11853

XDC中的I/O约束虽然形式简单,但整体思路和约束方法却与UCF大相径庭。加之FPGA的应用特性决定了其在接口上有多种构建和实现方式,所以从UCF到XDC的转换过程中,最具挑战的可以说便是本文将要

2017-11-17 19:01:00 6665

6665

XDC和UCF约束的区别主要包括:XDC是顺序语言,它是一个带有明确优先级的规则。一般来说,UCF应用于网络,而XDC可以应用到引脚、端口和单元对象(Cell Object)。UCF的PERIOD约束和XDC的create_clock命令并不等效,这将导致不同的时序结果。

2017-11-18 03:01:03 11231

11231 Xilinx©的新一代设计套件 Vivado 中引入了全新的约束文件 XDC,在很多规则和技巧上都跟上一代产品 ISE 中支持的 UCF 大不相同,给使用者带来许多额外挑战。Xilinx 工具专家

2017-11-18 03:59:01 3164

3164 为解决拖挂式移动机器人系统路径规划算法精准性低、稳定性差和无法考虑系统间安全性等的问题,提出一种基于路径跟踪方法的路径规划算法。该算法融合快速拓展随机树( RRT)基本算法和路径跟踪控制方程,通过

2017-12-04 14:18:30 6

6 的双端和K端网络可靠性研究基础上,提出了基于截断的路径约束方法;并根据该方法构造二元决策图BDD模型进行带约束的是端网络可靠性分析。该算法针对k端点对点信息流在一定时间延迟下完成传输问题,具有较强的实际意义。实例分析结果

2017-12-06 14:03:03 0

0 针对程序中因存在路径条数过多或复杂循环路径而导致路径验证时的路径搜索空间过大,直接影响验证的效率和准确率的问题,提出一种基于可满足性模理论(SMT)求解器的程序路径验证方法。首先利用决策树的方法

2017-12-11 13:49:41 1

1 针对多视图相关性算法未有效利用视图中相关信息且忽视了潜在的鉴别信息的问题,提出基于同一视图内和不同视图间的双重鉴别相关性分析( DVDCA)算法。首先,设计有监督的类内和类间相关性变量,通过最大化

2017-12-22 09:51:00 0

0 针对协同设计冲突无法准确全面检测的问题,提出了一种基于约束的冲突检测模型。在分析了协同设计中约束分层和约束满足问题的基础上,该检测模型将约束划分为已知约束关系集合和未知约束关系集合两部分,分别

2018-01-05 11:30:08 1

1 超字并行(SLP)是一种针对基本块的向量并行发掘方法,结合循环展开可以发掘更多的并行性,但同时也会产生过多的发掘路径。针对上述问题,提出了一种分段约束的SLP发掘路径优化算法;采用分段的冗余删除方法

2018-01-12 15:11:08 0

0 ,支持由非确定性的基本事件概率范围约束求解系统的最优化失效率。通过对实际系统的分析、求解及与现有工具的对比,说明分析方法的有效性,并通过对实际系统的分析给出了基本事件概率约束和延时门参数对系统整体失效率的

2018-01-14 10:56:32 0

0 目前对泊车方法的相关研究仅适用于平行泊车和垂直泊车中的一种泊车场景。为此,提出通用性的自主泊车路径规划方法。该方法融合车辆运动学约束和路径约束,以泊车时间为性能指标,建立泊车路径规划最优控制

2018-02-24 10:36:25 16

16 Express DSP组件(XDC,发音为EXE DEE)是一个提供优化的可重用软件组件的标准实时嵌入式系统。 本文档是基于XDC的软件包的用户指南,包括XDC本身。

2018-04-25 09:09:08 4

4 通过信号量和锁提供形式排除的方法。

您选择的机制取决于需要同步的线程类型。该应用程序说明描述了各种DSP/BIOS线程同步原语以及相关的问题和约束。

2018-05-03 09:24:55 4

4 设计能否满足时序。主要涉及到xilinx vivado xdc约束语法,给出对应的ISE ucf 语法。另外quatus的语法和xdc几乎兼容,原理都一样。

2018-06-25 09:14:00 6374

6374 在做模块级综合的时候,对于IO路径一般会使用60%的端口时钟进行约束,如果这样的路径涉及到feedthrough path,也就是INPUT->REG的路径同时有分支到INPUT->OUTPUT

2018-08-21 17:37:39 9141

9141

本培训中概述的方法将使您能够实现时序收敛的“签核”质量XDC约束。

无论复杂程度如何,这种方法还可以使您更快地实现时序收敛......

2018-11-29 06:53:00 3143

3143

观看视频,了解和学习有关XDC约束,包括时序,以及物理约束相关知识。

2019-01-07 07:10:00 5510

5510

了解如何将Altera的SDC约束转换为Xilinx XDC约束,以及需要更改或修改哪些约束以使Altera的约束适用于Vivado设计软件。

2018-11-27 07:17:00 4611

4611 通过详细了解错误路径,最小/最大延迟和案例分析约束,了解不同类型的异常约束。

2018-11-30 06:39:00 4474

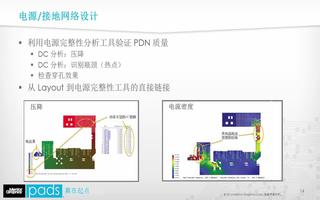

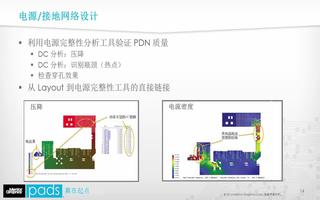

4474 目前,PCB 电气和制造约束的数量和复杂性不断激增。参加这次研讨会可了解如何轻松管理您的设计规则和约束。我们将详细介绍如何为网络、网络类和间距组合创建约束,如何建立规则层级构等。

2019-05-16 06:05:00 3136

3136

DDR接口的约束稍许复杂,需要将上升沿和下降沿分别考虑和约束,以下以源同步接口为例,分别就Setup/Hold Based 方法和Skew Based方法举例。

2019-07-25 11:01:38 2457

2457

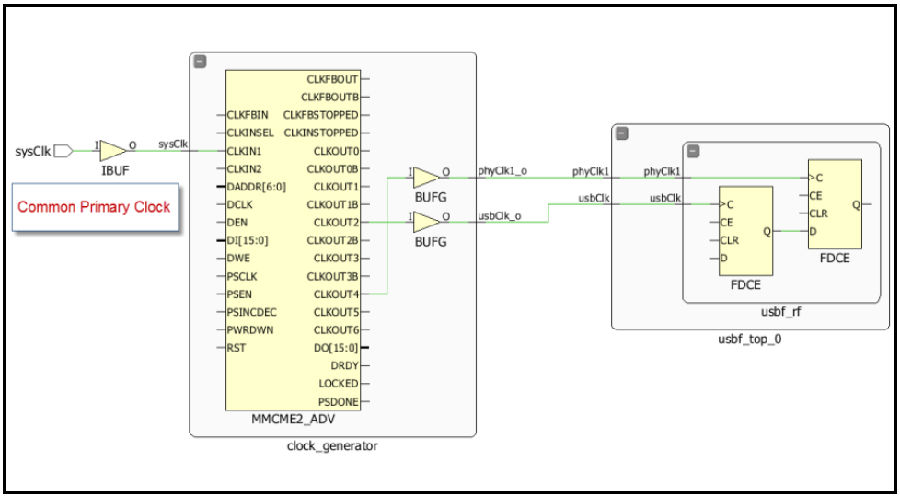

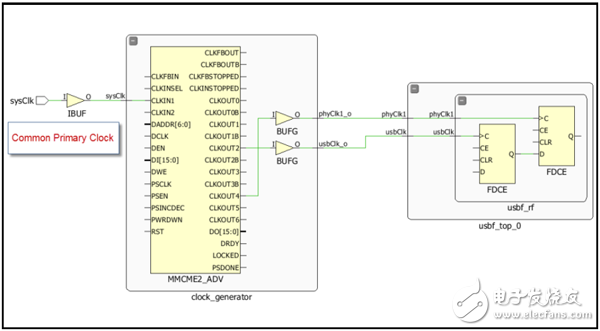

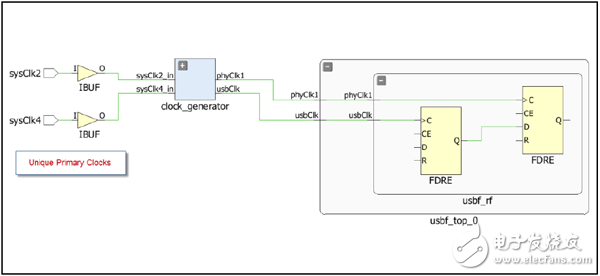

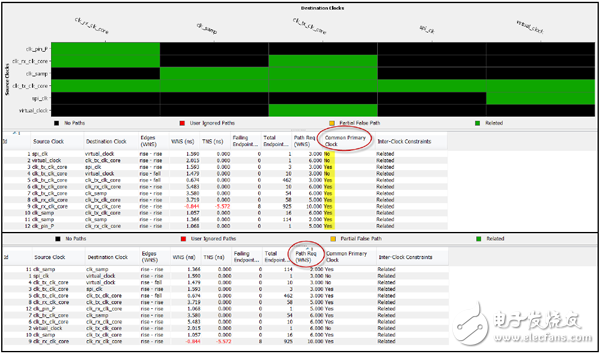

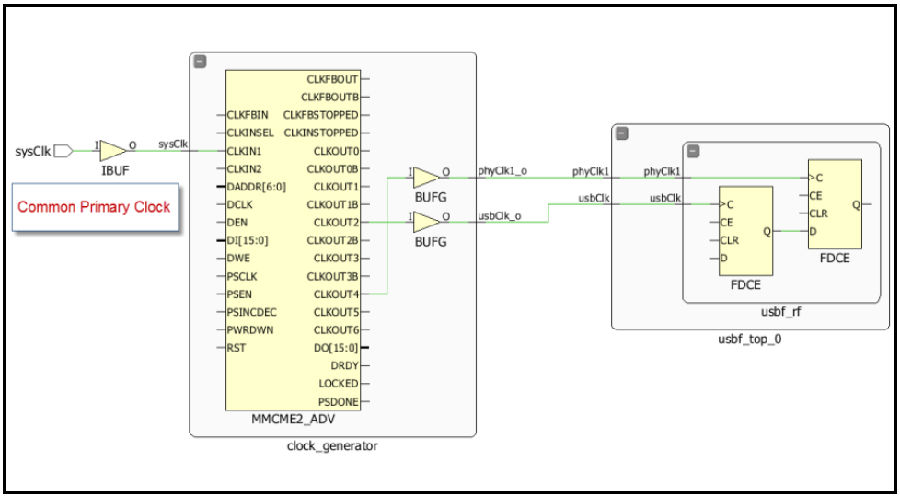

建议的做法是:首先,对“Common Primary Clock”排序(显示为Yes 或No),这么做可以快速鉴别出那些安全和不安全的CDC路径,接着观察对应的“Inter-Clock Constraints”栏内的内容,判断已读入的XDC中是否对这类路径进行了合理的约束。

2019-07-24 17:19:59 4977

4977

参加这次研讨会,学习如何轻松地管理您的设计规则和约束。我们将研究如何创建约束网、网类、和间隙集,如何建立规则的层次结构,等等。

2019-10-12 07:10:00 2344

2344 XDC 是 Xilinx Design Constraints 的简写,但其基础语法来源于业界统一的约束规范SDC。XDC 在本质上就是 Tcl 语言,但其仅支持基本的 Tcl 语法如变量、列表

2020-01-30 17:29:00 8814

8814 Vivado IDE约束管理器将任何已编辑的约束保存回XDC文件中的原始位置,但不会保存在Tcl脚本中。 任何新约束都保存在标记为目标的XDC文件的末尾。

2020-11-13 10:53:38 3491

3491

伪路径约束 在本章节的2 约束主时钟一节中,我们看到在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径

2020-11-14 11:28:10 2636

2636

xdc约束优先级 在xdc文件中,按约束的先后顺序依次被执行,因此,针对同一个时钟的不同约束,只有最后一条约束生效。 虽然执行顺序是从前到后,但优先级却不同;就像四则运算一样,+-x都是按照从左到右

2020-11-16 17:37:30 1558

1558 PCB设计取决于一套规则和约束条件,这些规则和约束条件决定了电路板的布局方式。这些规则涵盖了各个方面,从组件之间的紧密程度到特定网络的布线厚度。但是,成功的唯一方法是为每个作业专门设计规则。以前可行

2021-01-13 13:32:17 3649

3649 时,参考时钟选择相移的那个,发现不起作用,没有路径。 如果选择系统时钟,分析后是系统时钟的最大最小延时,没有相位移动后的信息,这是什么问题? 伴随时钟创建的Create_generated_clock中的Set_output_delay如下: Txc1 是锁相环移动相位后直接送到输出管脚,Rxc1是驱动数据的。 数据输出路径以

2021-06-09 17:28:01 3888

3888

使得问题更加复杂,比如一个设计使用了不同的IP核或者由不同团队开发的模块。不管设计者在设计中,使用了一个还是多个XDC文件,Xilinx推荐设计者使用下面的顺序来组织约束。XDC文件的约束顺序如下

2021-10-13 16:56:54 6309

6309 XDC约束可以用一个或多个XDC文件,也可以用Tcl脚本实现;XDC文件或Tcl脚本都要加入到工程的某个约束集(set)中;虽然一个约束集可以同时添加两种类型约束,但是Tcl脚本不受Vivado工具管理,因此无法修改其中的约束;

2022-06-30 11:27:23 2848

2848 要从时序分析删除一组路径,如果您确定这些路径不会影响时序性能(False 路径),可用FROM-TO 约束以及时序忽略 (TIG) 关键字。

2022-08-02 08:57:26 517

517 ,为什么有些路径在分析时忽略了?我怎么去定位这些约束是哪里设定的?本文结合一个具体案例,阐述了如何追溯同一时钟域内partial false path的来源,希望为开发者的设计调试提供一些技巧和窍门。

2022-08-02 08:03:36 1014

1014

约束文件是FPGA设计中不可或缺的源文件。那么如何管理好约束文件呢? 到底设置几个约束文件? 通常情况下,设计中的约束包括时序约束和物理约束。前者包括时钟周期约束、输入/输出延迟约束、多周期路径约束

2022-12-08 13:48:39 879

879 一、什么是多周期路径约束? 不管是quartus中还是在Vivado中,默认的建立时间和保持时间的检查都是单周期的,如图1所示,也就是说如果A时刻发送,B时刻捕获,这两者之间相差一个时钟周期,也就

2022-12-10 12:05:02 779

779 Xilinx的新一代设计套件Vivado中引入了全新的约束文件 XDC,在很多规则和技巧上都跟上一代产品 ISE 中支持的 UCF 大不相同,给使用者带来许多额外挑战。Xilinx 工具专家告诉你,其实用好 XDC 很容易,只需掌握几点核心技巧,并且时刻牢记:XDC 的语法其实就是 Tcl 语言。

2023-03-28 09:51:10 1802

1802 上一篇《XDC 约束技巧之时钟篇》介绍了 XDC 的优势以及基本语法,详细说明了如何根据时钟结构和设计要求来创建合适的时钟约束。我们知道 XDC 与 UCF 的根本区别之一就是对跨时钟域路径(CDC

2023-04-03 11:41:42 1135

1135 《XDC 约束技巧之时钟篇》中曾对 I/O 约束做过简要概括,相比较而言,XDC 中的 I/O 约束虽然形式简单,但整体思路和约束方法却与 UCF 大相径庭。加之 FPGA 的应用特性决定了其在接口

2023-04-06 09:53:30 729

729 继《XDC 约束技巧之 I/O 篇(上)》详细描述了如何设置 Input 接口 约束后,我们接着来聊聊怎样设置 Output 接口约束,并分析 UCF 与 XDC 在接口约束上的区别。

2023-04-10 11:00:42 624

624 《XDC 约束技巧》系列中讨论了XDC 约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入 Vivado中 的 XDC 实际上就是用户设定的目标,Vivado

2023-05-04 11:20:31 2368

2368

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

在常规非DFX(DynamicFunction eXchange)的Vivado设计中,我们可能会碰到给某一个指定的模块添加特定的约束。这时一个简单的方法就是将这些约束单独写在一个.xdc或.tcl

2023-08-17 09:23:39 302

302

正在加载...

电子发烧友App

电子发烧友App

评论