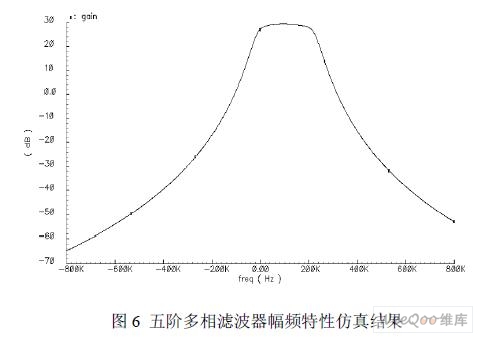

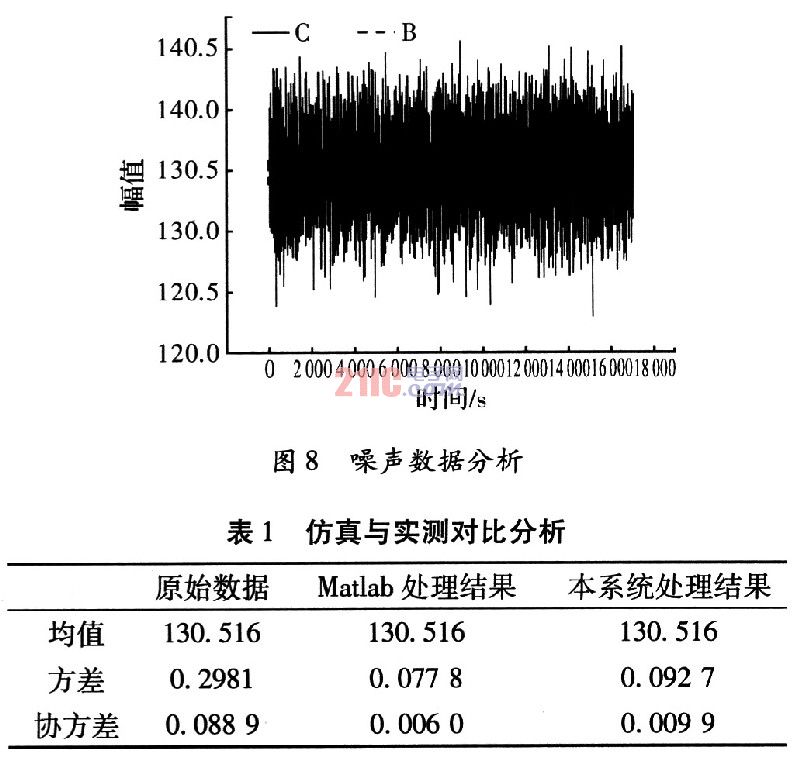

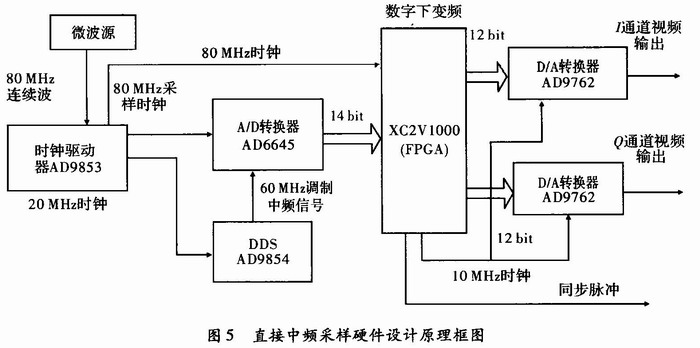

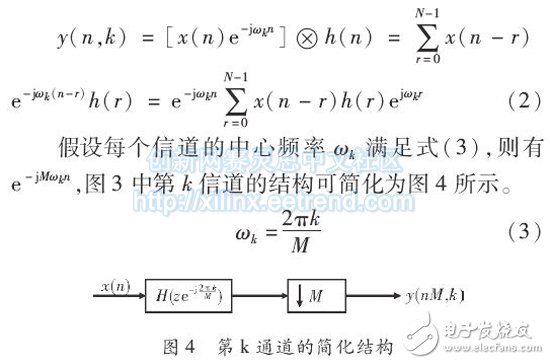

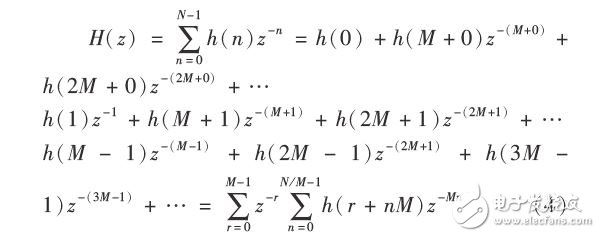

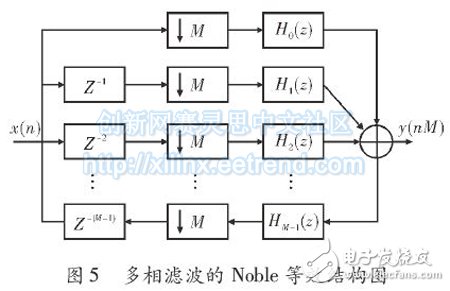

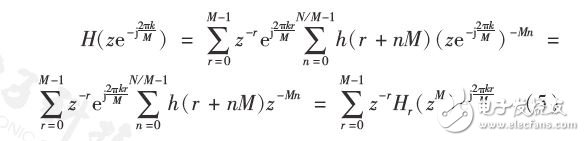

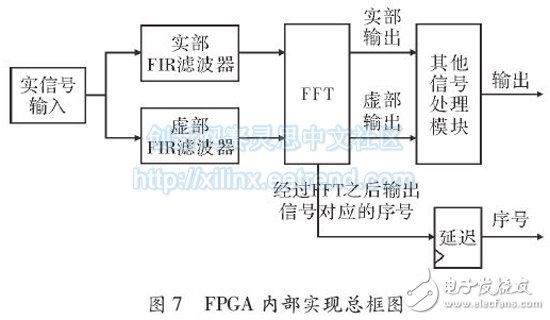

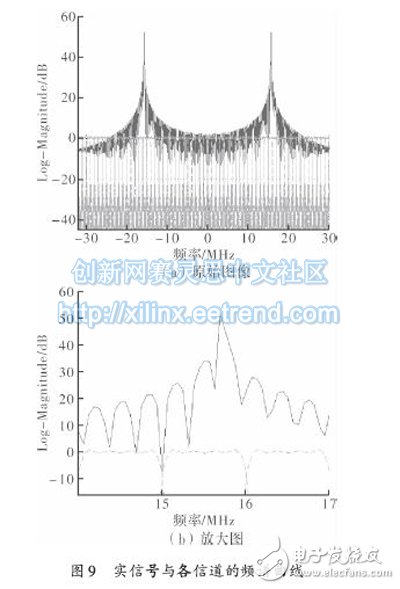

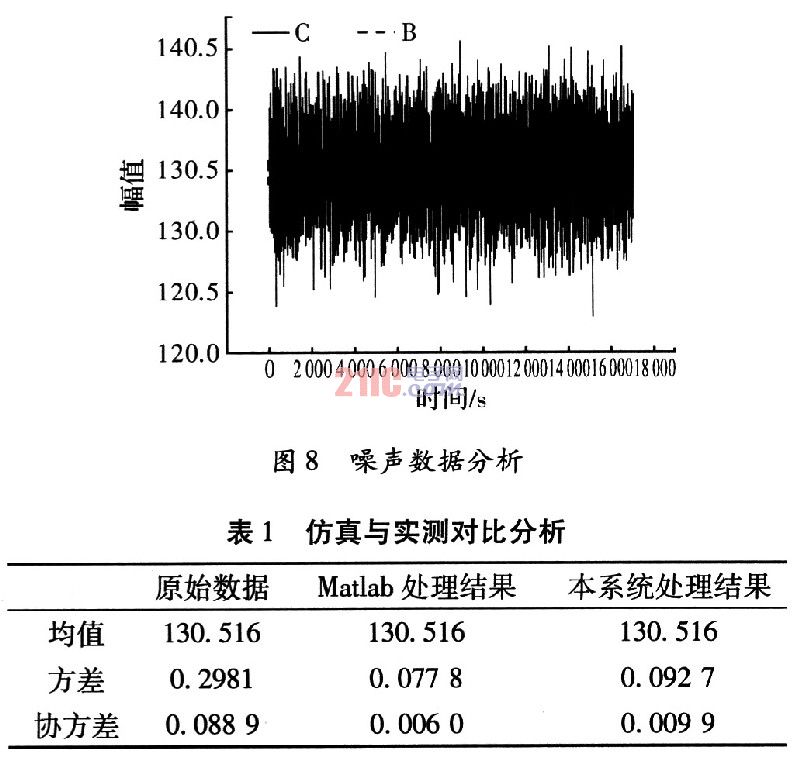

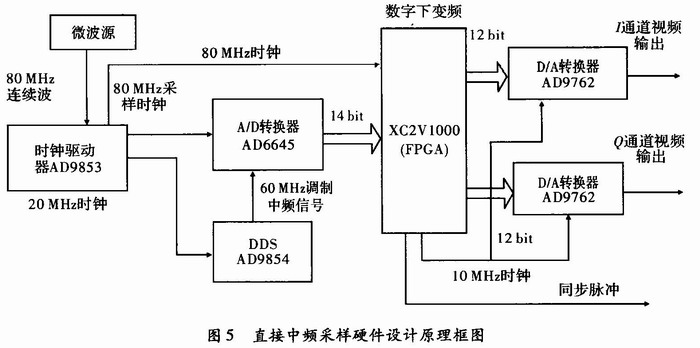

本文介绍了基于FPGA、以并行多相滤波结构为算法基础的超宽带数字下变频技术。设计过程包括高速AD信号降速预处理,应用SysGen开发环境完成的数字混频、多相滤波和数据抽取,并通过仿真验证了算法

2014-02-22 10:23:41 3144

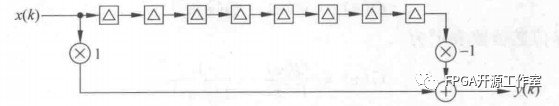

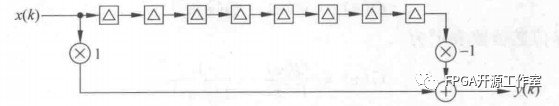

3144 sample rate convert 和 down sample rate convert 的FPGA实现打下基础。 1 梳状滤波器 图1 梳状滤波器结构 梳状滤波器的两端为1和-1的权值,具有简单

2020-11-21 09:57:00 5220

5220

本帖最后由 eehome 于 2013-1-5 10:03 编辑

fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点

2012-08-11 18:27:41

fpga实现滤波器fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点。本文研究了一种16阶FIR滤波器的FPGA设计方法

2012-08-12 11:50:16

进行的配置:1、当用命令滤波来使芯片进入TX状态时,进入是否成功取决于CCA MODE的配置,CCAMODE指示了那种情况可认为是信道空闲:CCAMODE 信道空闲的标准00 总是空闲的01 接受

2016-04-12 14:21:38

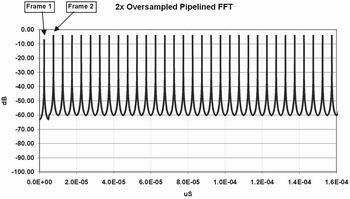

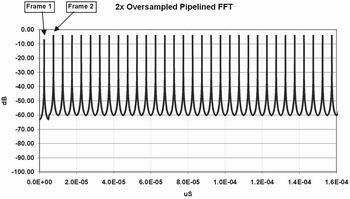

本文将对FFT和多相位DFT滤波器组进行比较,包括稳定状态和瞬时条件的情况。同时也简要地分析了过抽样和所谓的“最小相位”滤波器的内容。

2021-04-12 07:01:58

实现各种数字信号处理算法的工程方法。本书将理论与实践相结合,给出了相应算法的硬件结构,并配有时序图,以帮助读者深入理解设计思路。第1章 现场可编程逻辑门阵列(FPGA)技术现状1.1 FPGA已进入

2012-04-24 09:33:23

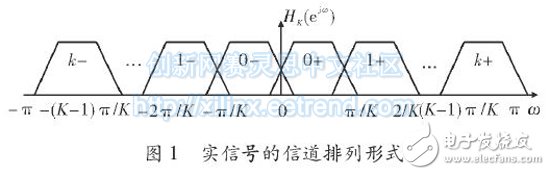

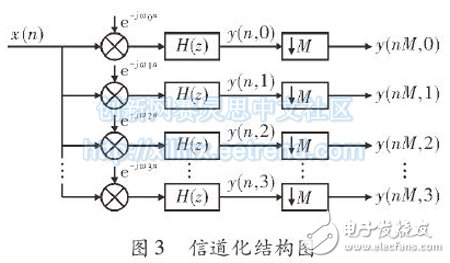

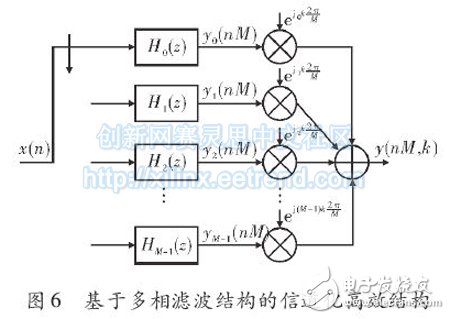

的信号全概率接收的接收机,而基于多相结构的信道化接收机相对于传统意义上的信道化接收机对同一频段信号而言所需硬件资源更少,且更易于实现。其相对传统的信道化接收机凭借其高效的多相结构,使其在多信道处理方面得到了广泛应用,是接收机的发展趋势。

2019-09-30 08:05:43

)、离散余弦变换(DCT)、小波变换、数字滤波器(有限脉冲响应(FIR)、无限脉冲响应(IIR)和自适应滤波器)以及数字上下变频器。这些算法中,每一种都有一些结构性的元件可以用并行方法实现。而FPGA

2021-12-15 06:30:00

基于多相滤波结构的雷达信号检测技术

2012-08-20 13:00:33

【作者】:袁江南;汤碧玉;陈辉煌;【来源】:《厦门大学学报(自然科学版)》2010年02期【摘要】:给出了一种自适应滤波器的设计和FPGA的实现方法.简要分析了最小均方误差(LMS)、归一化最小均方

2010-04-24 09:01:12

CIC(Cascade IntegratorComb)滤波器最早由Hogenauer提出,后来出现了很多改进的结构形式。随着芯片技术的快速发展、多相滤波技术的广泛应用以及无线通信市场的迅速

2019-09-23 07:22:30

器的响应越好。然而这里有折衷的情况,由于大量的抽头增加了对逻辑的需求、增加了计算的复杂性,增加了功耗,以及可能引起饱和/溢出。多相技术可以用于实现滤波器,拥有与传统FIR滤波器可比的结果,而且使用了较少

2019-07-08 08:01:03

处理器(FPGA,DSP)是一个“瓶颈”;基于多相滤波的信道化接收机抽取在滤波之前,运算量小,且输出速率低,便于FPGA实现,这使得在一片FPGA中实现数字信道化成为可能。

2019-08-22 08:01:34

使用了较少的逻辑、需要较少的计算资源、更低的功耗,并减少了可能的饱和/溢出。可怎么办,才能用中档FPGA实现多相滤波器?

2019-08-06 07:12:39

如何用中档FPGA实现多相滤波器?

2021-04-29 06:30:57

本文首先介绍了FIR滤波器和脉动阵列的原理,然后设计了脉动阵列结构的FIR滤波器,画出电路的结构框图,并进行了时序分析,最后在FPGA上进行验证。结果表明,脉动阵列的模块化和高度流水线的结构使FIR

2021-04-20 07:23:59

),滤波器的响应越好。然而这里有折衷的情况,由于大量的抽头增加了对逻辑的需求、增加了计算的复杂性,增加了功耗,以及可能引起饱和/溢出。多相技术可以用于实现滤波器,拥有与传统FIR滤波器可比的结果,而且

2019-10-22 06:55:44

倍数关系。那我们该如何设计宽带数字接收机的信道化?如何解决延迟与抽取的问题?并完成整个复多相滤波器的FPGA设计呢?

2019-08-07 08:01:57

,有可能丢失信号。而改进后的无盲区多相滤波器的信道数与抽取倍数不再相等。一般的旋转开关方法实现延迟和抽取只适用于信道数与抽取倍数相等的情况,而无法适应改进后的算法。但是,信道数和抽取因子之间往往存在倍数关系。那么我们该如何设计宽带数字接收机的信道化?完成整个复多相滤波器的FPGA设计呢?

2019-08-06 06:26:05

本文介绍了一种采用级联结构在FPGA上实现IIR数字滤波器的方法。

2021-04-15 06:16:32

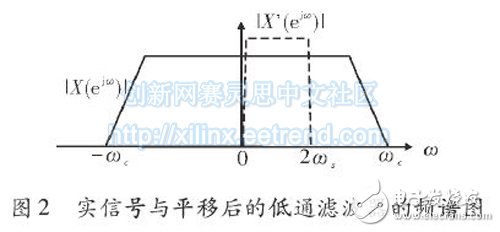

( DDC) 技术。所以数字下变频技术在宽带短波信道模拟器的数字化和软件化过程中起到了重要的作用。FPGA 具有较高的处理速度和很强的稳定性,而且设计灵活、易于修改和维护,同时可以根据不同的系统要求,采用不同的结构来完成相应的功能,大大提高系统的适用性及可扩展性。因此,FPGA 逐渐成为实现DDC 的首选。

2019-07-22 06:27:47

并行流水结构FIR的原理是什么基于并行流水线结构的可重配FIR滤波器的FPGA实现

2021-04-29 06:30:54

怎么实现基于FPGA的无线信道模拟器的设计?

2021-05-25 06:09:47

本文提出的一种数字信道化IFM接收机方案结合了数字信道化接收机高效结构和相位差分瞬时测频方法,从而降低了系统复杂度,提高了实时处理能力,仿真结果表明该方案具有较好的信号检测能力。用现代技术来实现宽带

2021-02-23 07:05:58

老板出了个这样的题,但是单速率数字信道化,没找到什么相关的资料,于是就求到论坛了,请各位大神指点明路,谢谢大家了哇~

2014-03-04 20:33:48

, 这就要求信道选择滤波器能够克服临道比本道高40 dB的干扰, 于是在设计的时候要求信道选择滤波器在两倍频处有大于45 dB的抑制。 根据UHF RFID接收机结构的特点, 在多读写器环境中, 接收机将

2019-05-29 07:46:53

AD9361支持的信道带宽是是200KHZ-56MHZ,但是对于有些应用,信道间距可能只有20-50KHZ,对于这样的信号这种滤波器无法实现对一个信道内信号进行滤波了。那这个芯片是不是支持这样信道

2018-10-09 17:39:16

数字信道化原理是什么?怎样去设计一种宽带信道化接收机?如何对宽带信道化接收机进行仿真?

2021-05-31 06:50:55

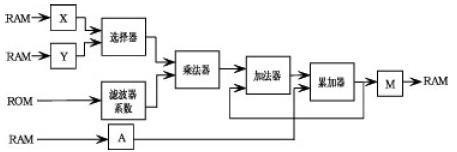

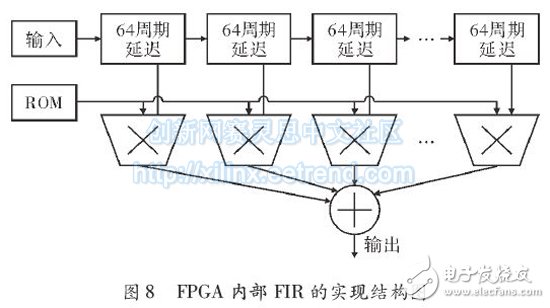

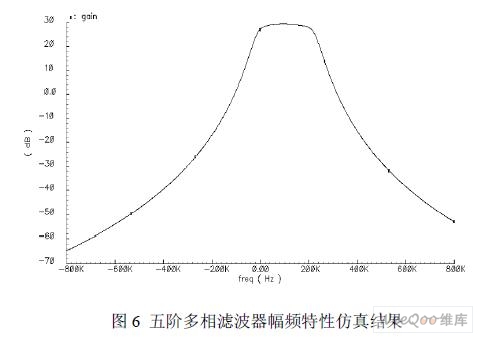

,得到相应阶数的滤波器系数,量化并进行16进制转换供FPGA使用。 前面说了,多相结构的FIR滤波器是在算法上下功夫,所以本身滤波器的设计过程就是普通滤波器的设计过程,并没有什么不同,下面再来看多相

2015-08-29 15:37:11

手机电视/移动多媒体广播 广播信道帧结构、信道编码和调制、无线射频特性

本标准是手机电视/移动多媒体广播系列标准之一,该系列标准的名称及结构如下:1) 手

2008-07-22 14:48:36 29

29 移动多媒体广播 第1 部分:广播信道帧结构、信道编码和调制Mobile Multimedia Broadcasting Part 1: Framing Structure, Channel

2008-10-21 15:59:48 7

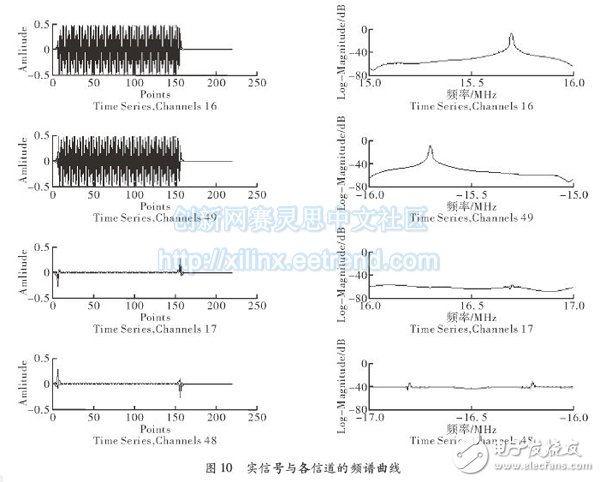

7 提出了一种多相滤波的宽带数字化接收机的设计技术;讨论了多相滤波的基本原理、设计及现场可编程门阵列实现,给出了多相滤波的中频数字化接收机的实现方案。计算机仿真

2009-02-21 11:46:21 22

22 本文以cdma的两个主要技术——码分技术和多址技术为基础,图文并茂的介绍了cdma(IS95和20001x)技术体制的信道编码和信道结构。信道编码技术包括沃尔什码(WalshCode)、长短PN码(伪

2009-06-10 15:30:48 40

40 本文以cdma的两个主要技术——码分技术和多址技术为基础,图文并茂的介绍了cdma(IS95和20001x)技术体制的信道编码和信道结构。信道编码技术包括沃尔什码(WalshCode)、长短PN码(伪

2009-06-17 18:10:22 20

20 基于FPGA对称型FIR滤波器的设计与实现:在基于FPGA的对称型FIR数字滤波器设计中,为了提高速度和运行效率,提出了使用线性I相位结构和加法树乘法器的方法,并利用Altera公I司的FPG

2009-09-25 15:38:38 30

30 基于渐消Ka lman滤波的M IMO2OFDM信道估计:针对快时变信道明显的频率选择性,提出了采用Kalman渐消记忆滤波的估计方法.信道采用AR模型建模,并利用LS算法估计时变信道的衰减因子. 仿真

2009-10-25 12:14:32 7

7 在OFDM 系统中,信道的快速时变性破坏了子载波间的正交性,从而导致子载波间干扰(ICI),降低了系统性能。该文针对双选择信道的时变特性,提出了一种新的Kalman 滤波信道估计算法

2009-11-17 14:11:41 8

8 多相滤波器组信道化接收机的FPGA 仿真实现赵伟 王静 李伟伟(大连海事大学 信息工程学院 辽宁 大连 116026)摘要:软件无线电理论中的信道化接收机理论在多信号同时提取

2009-12-15 15:04:51 33

33 本文详细讨论了利用新版本FPGA 辅助设计软件QuartusII6.0 中提供的浮点运算功能模块实现IIR 滤波器的方法,与采用FPGA 的乘法模块的同类设计相比,此滤波器设计结构简单,容易扩

2009-12-19 15:44:27 38

38 基于多相滤波结构的分级滤波处理软件无线电下变频能够解决以前存在的瓶颈问题,进行实时有效处理,算法的改进能更快速的执行二次采样过程并进一步减少硬件资源的损耗,滤

2010-01-20 14:31:19 22

22 用于标清视频信道的有源滤波器设计技巧关键词:滤波器 模拟 数字信号摘要:当今的高速运算放大器使得在视频应用中,采用有源滤波器来设计比采用无源电感电容(LC)滤

2010-02-06 10:34:07 16

16 如何设计用于标清视频信道的有源滤波器作者:Steven O Smith关键词:运算放大器,滤波器,PCB摘要:本文中的设计采用飞兆半导体的高速双运算放大器(FHP3230),来构造一个可

2010-02-06 10:43:30 22

22 针对传统数字正交变换存在A/D采样速率要求比较高导致后续的数字低通滤波成为瓶颈、运算数据量大、需要正交本振等方面的不足,提出了一种基于软件无线电多相滤波的数字正交

2010-07-10 15:55:28 12

12 设计一个由现场可编程门阵列(FPGA)控制的滤波器。该滤波器主要由3个模块组成:前置放大、滤波电路、FPGA显示与控制电路等利用FPGA作为放大器及程控滤波器电路中继电器组的控制模

2010-07-17 18:00:09 45

45 针对宽带阵列侦收系统,设计一种基于FPGA的信道化接收机实现方案,并对各模块具体的实现进行了分析、设计,特别是基于FPGA的信道化模块。整个系统具有子信道频带窄、利于对信

2010-07-21 15:59:59 18

18 为了解决电子侦察接收机中同时到达信号的接收问题,从传统的低通滤波器结构出发,给出了一种无盲区高效数字信道化接收模型。信道化之后进行瞬时幅度和相位差提取。通过系

2010-11-17 11:43:44 25

25 摘要:本文简要地论述了FFT和多相位DFT滤波器组在响应方面的差异。一般而言,多相位DFT(甚至包括任何滤波器组,比如PFT)在稳态条件下有着很好的相邻信道抑制性能,而瞬态响应却很糟糕。这符合了滤波器冲激响应结论。

2006-03-11 13:17:03 2056

2056

IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器

摘 要:本文介绍了一种采用级联结构在FPGA上实现任意阶IIR数字滤波器的方法。此

2008-01-16 09:45:39 2276

2276

基于FPGA的二次群分接器的结构分析及实现

1.引言

为了提高传输速率,扩大通信容量,减少信道数量,通常把多路信号复用成一路信号进行传输。在多种复

2009-12-08 09:54:42 653

653 基于GSM 接收机的集成多相滤波器设计

摘要:本文介绍了用于GSM接收机的低中频多相滤波器的设计,采用有源RC电路架构且单片全集成。设计采用TSMC 0.18um CMOS工艺,

2010-01-08 11:08:24 1945

1945

基于FPGA的星地信道模拟系统的研究与设计

1 引 言

卫星移动通信系统所能提供的业务的可行性与质量在很大程度上受到卫星与移动终端

2010-03-10 11:49:28 546

546

FPGA的Kalman滤波器的设计

摘要:针对电路设计中经常碰到数据的噪声干扰现象,提出了一种Kalman滤波的FPGA实现方法。该方法采用了TI公司的高精度模数转换

2010-04-13 13:32:46 2566

2566

DNLMS滤波器的FPGA设计方案

自适应滤波算法的研究始于20世纪50年代末,Widrow和Hoff等人最早提出最小均方算法(LMS)。算法由于结构简单,计算量小,易于实

2010-05-10 10:06:23 622

622

介绍一种利用带通采样定理及多相滤波的方式实现数字相干检波的方法,由于采用数字信号处理的方式获取I、Q基带信号

2010-11-09 09:53:22 1301

1301

本文设计的信道选择滤波器用于UHF RFID阅读器接收机模拟基带部分, 接收机采用I/Q 两支路正交的零中频结构, 图1是接收机模拟基带结构图。

2011-02-23 09:47:16 1880

1880

本文介绍了一种有理数采样率变换器的高效多相结构,并结合FPGA芯片的结构进行了实现与优化。文中的一些方法也适用于其他多采速率系统的设计。

2011-03-02 10:04:34 2161

2161

为解决现代电子战对接收机处理带宽宽、灵敏度高及实时性处理的要求,提出一种数字信道化接收机的设计方法。在推导高效信道化接收机模型的基础上,采用多相滤波器结构实现的数字信道化接收机。该接收机利用超高速A/D对数据进行高速采样,然后由高性能FPGA进行

2011-03-07 15:28:33 61

61 本文介绍用RC多相滤波器实现镜像抑制的原理,推导出电阻电容误差对镜像抑制影响的数学表达式,通过仿真验证表明,计算值与仿真值较为接近,并应用RC 多相滤波器来实现高镜像抑

2011-08-23 14:51:14 46

46 基于多速率信号处理原理,设计了用于下变频的CIC抽取滤波器,由于CIC滤波器结构只用到加法器和延迟器,没有乘法器,很适合用FPGA来实现,所以本文分析了CIC滤波器的原理,性能及影

2011-08-26 15:12:11 160

160 无线信道仿真和均衡器的FPGA设计与实现

2011-10-09 18:11:37 40

40 针对轨道电路信号(FSK信号)的检测提出了基于多相滤波器组的频谱细化(ZFFT)分析方法,该方法利用多相滤波器组将待分析的移频信号按照不同载频分解成多个子带,经过子带选择,再进

2011-10-10 15:09:01 37

37 多相DFT滤波器组是实现信道化接收机的一种高效结构,但是该结构要求信道数目与抽取倍数必须相等,限制了接收机参数设计的灵活性。该文将WOLA滤波器组引入信道化接收机,以信号的

2011-11-08 18:00:39 27

27 基于多相滤波的信道化接收机抽取在滤波之前,运算量小,且输出速率低,便于FPGA实现,这使得在 一片FPGA中实现数字信道化成为可能。本文利用信道频率重叠的方法连续覆盖整个瞬时

2012-05-23 10:43:04 3538

3538 信道化接收技术是解决宽带信号检测等问题的一种有效方式。信道化接收机因其具备较大的瞬时带宽、能够检测和处理同时到达的信号、具有准确的参数测量能力和一定的信号识别能力

2012-08-18 11:35:49 2186

2186

描述了基于FPGA的FIR滤波器设计。根据FIR的原理及严格线性相位滤波器具有偶对称的性质给出了FIR滤波器的4种结构,即直接乘加结构、乘法器复用结构、乘累加结构、DA算法。在本文中给

2012-11-09 17:32:37 121

121 研究了一种采用FPGA实现32阶FIR滤波器硬件电路方案;讨论了窗函数的选择、滤波器的结构以及系数量化问题;研究了FIR滤波器的FPGA实现,各模块的设计以及如何优化硬件资源,提高运行

2017-11-10 16:41:57 15

15 为了减少信道化接收机的资源消耗,对低通滤波器组实现信道化接收机的结构进行了研究。在前人将HB滤波器和FIR滤波器设计为多通道并采用时分复用方法的基础上,将NCO和CIC滤波器也做了同样处理,并在

2017-11-17 05:38:02 3382

3382

,其频率截获概率与分辨力的矛盾难以解决,无法实现全概率信号截获。而多信道化的频率检测技术属于瞬时测频,其架构是采用多个频率窗口(多个信道彼此衔接相邻)来覆盖接收机的整个频段.

2017-11-18 10:51:17 5139

5139

对一种单图像向导滤波器的高性能FPGA设计结构进行了分析,发现其中的均值滤波器存在设计缺陷,据此提出了一种向导滤波器的整数FPGA设计结构。通过改变均值滤波器的数据累加顺序,减少了存储资源

2017-11-22 15:43:12 12

12 ,有可能丢失信号,而改进后的无盲区多相滤波器的信道数与抽取倍数不再相等,信道数和抽取因子之间往往存在倍数关系。

2017-12-09 17:29:40 4221

4221

用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2018-04-28 11:50:00 1073

1073

的自适应调整是通过控制算法对信道中的信号进行快速检测,然后将结果和滤波器的输出结果进行差值计算进行反馈调节。利用Quartus II和DSP Builder设计基于FPGA的16阶系数可调FIR滤波

2018-07-23 17:21:00 2372

2372

用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2020-09-25 10:44:00 3

3 针对Σ△ADC输出端存在的高频噪声问题,设计了一种 Sinc数字抽取滤波器,实现了Σ-△调制器输出信号的高频滤波。分析了Sinc滤波器的结构原理,基于 Spartan6FPGA进行滤波器的设计与实现

2020-08-26 17:12:00 14

14 WCDMA中规定了小区搜索的时隙同步过程采用匹配滤波器的方法实现,本论文主要研究匹配滤波器原理及FPGA实现结构。

2021-01-26 16:22:43 12

12 提出了一种基于多相滤波器的并行有限脉冲响应(finite impulse response,FIR)滤波器结构,可以有效提高滤波器运算的吞吐率,与传统的串行滤波器结构比,并行滤波器运算速度可以提高

2021-01-28 17:22:00 15

15 提出了一种基于多相滤波器的并行有限脉冲响应(finite impulse response,FIR)滤波器结构,可以有效提高滤波器运算的吞吐率,与传统的串行滤波器结构比,并行滤波器运算速度可以提高

2021-01-28 17:22:00 7

7 针对电子战中的宽带侦察数字信道化接收机,提出了基于短时傅里叶变换的宽带数字信道化接收机的改进方法,给出了该方法的FPGA实现。该方法采用多相滤波结构,通过先对时域抽取信号进行傅里叶变换,再对变换结果

2021-02-05 17:35:51 27

27 针对高速率QPSK数据传输链系统,比较分析了数字中频接收与零中频接收的优、缺点,并提出了一种基于多相滤波的宽带中频正交采样数字零中频接收方案。基于FPGA对此数字零中频正交变换方案进行了实现和验证,同时,对一种全数字零中频QPSK信号的高速解调算法及其FPGA硬件实现进行了介绍。

2021-03-19 17:43:12 11

11 提出一种新的高阶FIR滤波器的FPGA实现方法。该方法运用多相分解结构对高阶FIR滤波器进行降阶处理,采用改进的分布式算法来实现降阶后的FIR滤波器。设计了一系列阶数从8到1 024的FIR滤波

2021-03-23 15:44:54 30

30 :针对高速率 QPSK 数据传输链系统,比较分析了数字中频接收与零中频接收的优、缺点,并提出了一种基

于多相滤波的宽带中频正交采样数字零中频接收方案。基于 FPGA 对此数字零中频正交变换方案

2022-12-12 15:44:36 3

3

正在加载...

电子发烧友App

电子发烧友App

评论