给中断控制器; 5. 拥有8个DMA触发事件并且可以编码控制; 6. 128个(64bit)的MFIFO,在传输的时候读写端可写入到此FIFO; 7. 支持任意内存到内存的传输; 整个系统中的DMA

2020-12-05 10:17:17 3606

3606 1、中断方式是在数据缓冲寄存区满后,发中断请求,CPU进行中断处理。

2022-06-10 11:44:44 16620

16620

DMA配置成DMA_Mode_Normal模式,开启传输完成中断,在中断函数中再次开启DMA怎么配置?直接调用"DMA_Cmd(DMA1_Channel4, ENABLE)"函数就可以了吗?

2015-07-21 21:43:12

[STM32H743] DMA中断服务函数判断条件1:首先->配置中断/* 开启DMA1 Stream0的中断 */ HAL_NVIC_SetPriority

2021-08-13 07:00:39

;独立的控制和状态流通道,提供相关的包信息;DMA的中断与系统中断控制器相连。 (2) AXI Centralized DMA 图4‑41 AXI CDMA 在此系统中,AXI CDMA与处理器

2020-12-23 17:48:04

,DMA会发挥重要作用,主程序更着眼于进行资源分配和流程控制。SPI初始化DMA和中断使用SPI的DMA功能,需要首先对相关寄存器初始化SPI3使用DMA2的Channel1接收数据,Channel2发送

2020-06-18 04:35:15

SRAM 在读写上有严格的时序要求,用 WEOECE 控制完成写数据,具体时序如图 7-17所示。图 7-17 SRAM 的写时序系统中两块 SRAM 分别由 DSP 和 FPGA 控制。当 DSP

2018-12-11 10:14:14

CPU控制完成,如CPU程序查询或中断方式。利用中断进行数据传送,可以大大提高CPU的利用率。 2:中断传送是由CPU通过中断服务程序来传送,每次要保护断点,保护现场需要多条指令,每条指...

2022-02-22 08:07:17

一、中断与DMA通信原理1.中断1.1.什么是中断中断是由内核外部产生的,一般由硬件引起,比如外设中断和外部中断等。通常在CPU 执行程序时,由于发生了某种随机的事件(外部或内部),引起CPU暂时中断

2022-02-10 06:09:23

中的TEIFx位硬件置位。读写一个保留的地址区域,将会产生DMA传输错误。同时模块硬件会自动清0发生错误的通道所对应的DMA_CCRx寄存器的EN位,该通道被关闭。如果在DMA_CCRx寄存器中置位了TEIE,则将产生中断。

2023-05-15 16:41:07

使用了HAL库的函数来进行数据的读写:HAL_StatusTypeDef HAL_SPI_TransmitReceive_DMA(SPI_HandleTypeDef *hspi, uint8_t

2021-04-01 11:47:59

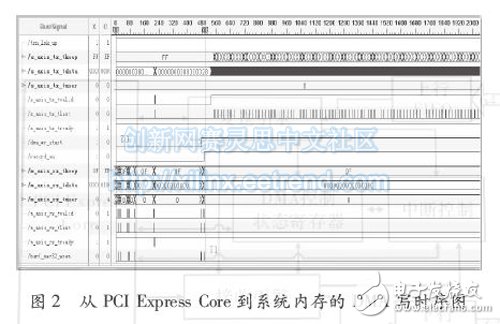

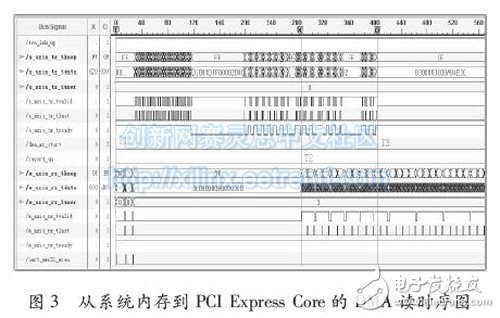

DMA Read(内存-->FPGA)的速度可达3380MB/s.7. FPGA内部的Master DMA也包含与DMA传输相关的控制状态寄存器和中断寄存器.8. PCI Express驱动采用

2014-08-23 13:15:30

)的速度可达6110MB/s.9. FPGA内部的Master DMA也包含与DMA传输相关的控制状态寄存器和中断寄存器.10. PCI Express驱动采用WinDriver,采用Legacy PCI

2015-06-21 13:38:12

与DMA传输相关的控制状态寄存器和中断寄存器.8. PCI Express驱动采用WinDriver,采用Legacy PCI或MSI中断方式,用户应用软件通过WinDriver的API函数访问PCI

2015-01-10 20:36:09

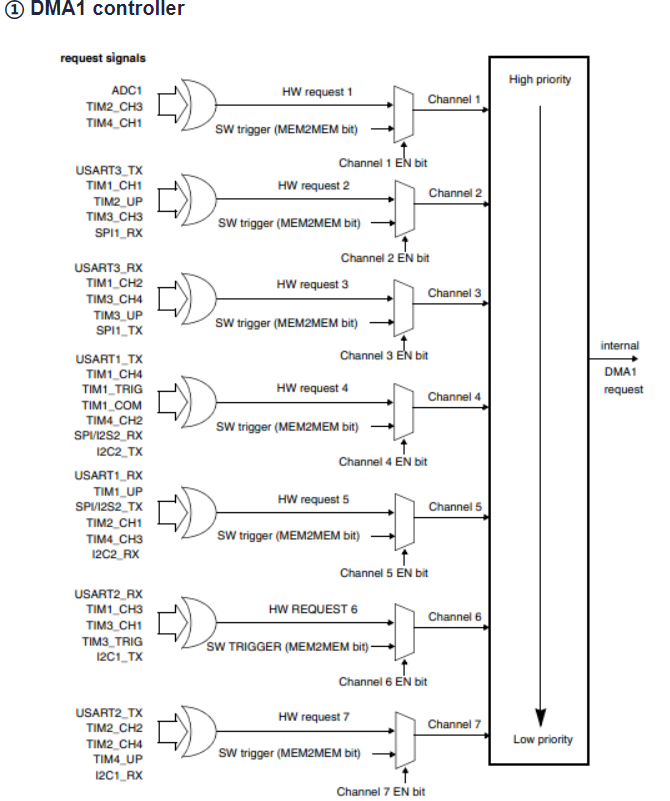

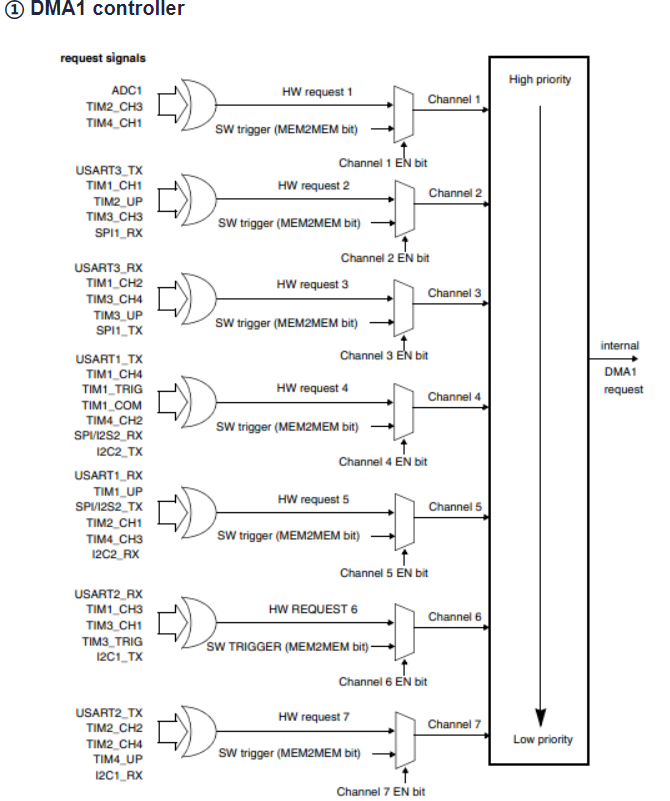

、传输完成)通过“线或”方式连接至NVIC,需要在中断例程中进行判断。进行DMA配置前,不要忘了在RCC设置中使能DMA时钟。STM32的DMA控制器挂在AHB总线上。DMA总共有7个通道,各个通道

2015-01-13 14:02:03

1、DMA的中断标志需要软件手动清除,即使你启用了中断,也不会硬件清除的,可以:DMA_ClearITPendingBit(DMA_IT_HT);//清楚传输过半中断标志

2014-12-31 10:55:53

与DMA传输相关的控制状态寄存器和中断寄存器.Serial RapidIO接口特性如下:1. 支持1.25Gbps, 2.5Gbps, 3.125Gbps, 5Gbps, 6.25Gbps线速率2.

2014-08-23 13:27:47

也包含与DMA传输相关的控制状态寄存器和中断寄存器.8. PCI Express驱动采用WinDriver,采用Legacy PCI或MSI中断方式,用户应用软件通过WinDriver的API函数访问

2014-03-01 18:11:32

DDR_FIFO中的数据达到半满状态时,HF标志位有效,通过FPGA向 PEX8311发出DMA中断请求。PC机响应中断后,设置DMA传输模式,传输字节数及地址信号等。PEX8311通过LHOLD申请控制本地

2015-01-29 14:09:17

为CplD),Byte Count为0x004,TAG为0x00,其他信息对座入号就行了。具体的含义可查询PCIE协议规范。

1.2 DMA读写操作TLP解析

DMA直接内存访问,内存访问的发起者是FPGA

2023-11-17 15:08:37

的PICE驱动是最佳选择。

官方也提供了一个在Windows的驱动例程,该例程能够完成PCIE的DMA读写操作和PIO内存读写操作,但是该驱动并未完全适配IP生成的官方例程,官方提供另一份的FPGA的工程与之

2023-11-17 14:55:24

MANAGEMENT command(Trim),DMA控制器8. 实现SATA设备带电热插拔9. 利用多个SATA Host Controller,可以组成RAID阵列控制器基于FPGA的SATA

2015-11-11 15:06:39

的控制和状态流通道,提供相关的包信息;DMA的中断与系统中断控制器相连。(2) AXI Centralized DMA图4‑41 AXI CDMA在此系统中,AXI CDMA与处理器等设备通过AXI

2022-10-14 15:23:41

将emif_fpga_dma移植到sy***ios下,参照的sy***ios下的EDMA3,就是读写有问题没有从emif中读取到数据

2020-05-12 07:56:46

想在ucos下实现DMA中断里发送数据。由于DMA是不受cpu干扰的,当发完一组数据触发DMA发送完成中断时(中断里Post一个信号量告知发送完成),DMA中断也和其他普通中断一样需要进入和退出临界区吗?因为总感觉DMA中断处理时任务是可以调度的(因为调度是由cpu发起)。

2019-09-18 23:43:14

串口接收(或者发送)的数据比较大,如果用中断逐字节从FIFO读数据太耗时了,光盘里的找不到有关DMA读写串口的demo

2024-01-17 07:35:26

串口接收(或者发送)的数据比较大,如果用中断逐字节从FIFO读数据太耗时了,光盘里的找不到有关DMA读写串口的demo

哪有朋友有相关的资料,能让我参考参考,感谢

2023-08-29 08:32:14

嗨,我正在使用超大规模的FPGA板。我可以通过DMA子系统IP和DDR控制器IP将数据从PC传输到DDR。我打算在FPGA中进行一些处理,然后更新数据,以便PC可以读取。如何通过PCIe指示PC处理

2020-05-08 09:40:04

需求:两块fpga互联,两块fpga分别模拟成特定的pcie设备,两个设备通过serdes总线互联通信,fpga仅仅只要模拟特定的设备就可以,不需要负载的逻辑,提供简单的读写,dma,中断等功能。高价寻高手,请各位多帮忙啊。

2019-02-11 15:31:02

STM32Cube FW_F4 V1.24.0,其中与FATFS文件系统相关的底层读写函数SD_read和SD_write在文件sd_diskio.c中,都是用DMA模式编写的,以读函数为例,核心代码为

2019-08-09 18:29:52

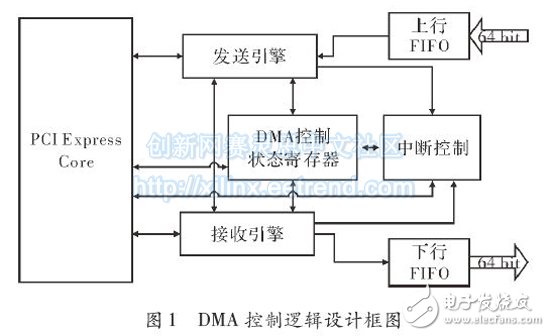

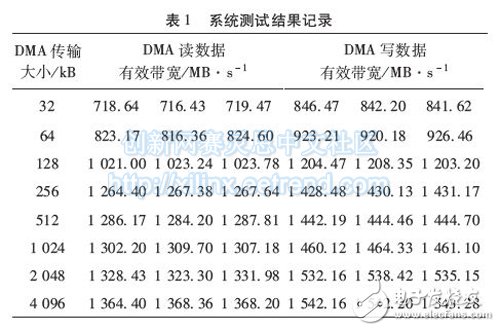

数据流从FPGA传给CPU成为系统设计的一个关键。如果每传递一个字节的数据都需要CPU的介入,那么不论是采用中断驱动还是采用程序查询的方式,数据传输速率都会很低,无法满足系统需求。DMA(直接存储器

2019-05-22 05:00:53

USB对DMA读写怎么实现

2019-06-18 06:19:23

USB对DMA读写怎么实现

2020-04-07 15:27:34

数据流从FPGA到SDRAM的传输方式。 2 DMA传输方案设计 FPGA和MPC8260间的数据传输接口设计如图3所示。图中左侧FPGA,通过16位数据线、10位地址线、2根中断请求线和一些读写控制

2019-04-18 07:00:08

DMA(Direct Memory Access)的概念DMA方式不用处理器干预完成M与I/O间数据传送。DMA期间系统总线由其它主模块控

2008-12-09 11:03:56 50

50 采用MPC8260和FPGA的DMA接口设计

以MPC8260通信处理器为硬件平台,结合中断处理和IDMA传输机制设计一种最高传输速率可达500 Mbps的数据传输接口。本文详

2009-03-29 15:13:20 893

893

基于MPC8260处理器和FPGA的DMA接口设计

以MPC8260通信处理器为硬件平台,结合中断处理和IDMA传输机制设计一种最高传输速率可达500 Mbps的数据传输接口。

&n

2010-02-08 10:17:52 1050

1050

学习 STM32 的ADC转换,在开发板上写程序调试。 四个任务: 1.AD以中断方式(单次)采集一路 2.AD以中断方式连续采集四路 3.AD以DMA方式采集一路,DMA深度为一级 4.AD以DMA方式采集四路,每路

2012-03-23 10:54:11 4547

4547 本章主要介绍在 Nios II 实现 DMA 传输,通过本章,你能学到

(1)DMA 控制模块的生成和使用。

(2)用 DMA 传输方式读写 SDRAM。

2015-12-14 15:40:05 2

2 DMA_读取GPIO电平到内存(中断恢复目的地址)

2016-01-12 18:20:04 4

4 华清远见FPGA代码-SDRAM读写控制的实现与Modelsim仿真

2016-10-27 18:07:54 26

26 读写操作。DDR3用户接口仲裁控制模块将中断请求分成多个子请求,实现视频中断和图形中断的并行处理。帧地址控制模块确保当前输出帧输出的是最新写满的帧。

2017-11-18 18:51:25 6412

6412

设置命令缓冲区的方式,使得DMA控制器可以缓存PC端的数据传输请求,FPGA根据自身需求动态地访问PC端存储空间,增强了传输灵活性;同时,提出一种动态拼接的DMA调度方法,通过合并相邻存储区访问请求的方式,进一步减少主机与硬件的交互次数和中断产

2017-12-05 19:00:45 2

2 DMA既可以指内存和外设直接存取数据这种内存访问的计算机技术,又可以指实现该技术的硬件模块(对于通用计算机PC而言,DMA控制逻辑由CPU和DMA控制接口逻辑芯片共同组成,嵌入式系统的DMA控制器内建在处理器芯片内部,一般称为DMA控制器,DMAC)。

2017-12-07 10:23:24 15812

15812

一般而言,DMA控制器的功能与结构是由本单位特定的系统结构决定的。但是作为IP而言,DMA控制器又要有其一般性。DMA是指外部设备直接对计算机存储器进行读写操作的I/O方式。这种方式下数据的读写无需

2017-12-07 15:48:19 5886

5886

DMA既可以指内存和外设直接存取数据这种内存访问的计算机技术,又可以指实现该技术的硬件模块(对于通用计算机PC而言,DMA控制逻辑由CPU和DMA控制接口逻辑芯片共同组成,嵌入式系统的DMA控制器内建在处理器芯片内部,一般称为DMA控制器,DMAC)。

2017-12-07 16:08:38 5155

5155

来持续地读写外设的内存单元(8位、16位或32位),直到整个数据传输过程完成。 (2)DMA,即由DMA控制器(DMA Controller,简称DMAC)来完成整个数据传输过程。在此期间,CPU可以并发

2017-12-07 19:13:28 268

268 本文实现的基于FPGA的PCIe总线接口的DMA控制器是在Altera PHY IP和Synopsys Core IP的基础上实现的,利用Synopsys VIP验证环境进行了功能仿真验证

2018-01-11 10:57:04 11281

11281

本文档的主要内容详细介绍的是FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文主要包括了:FPGA读写SDRAM的实例,SDRAM控制器核心介绍,系列SDRAM数据手册

2018-12-25 08:00:00 56

56 一个DMA控制器,实际上是采用DMA方式的外围设备与系统总线之间的接口电路,这个接口电路是在中断接口的基础上再加DMA机构组成。习惯上将DMA方式的接口电路称为DMA控制器。

2019-04-01 16:08:06 10025

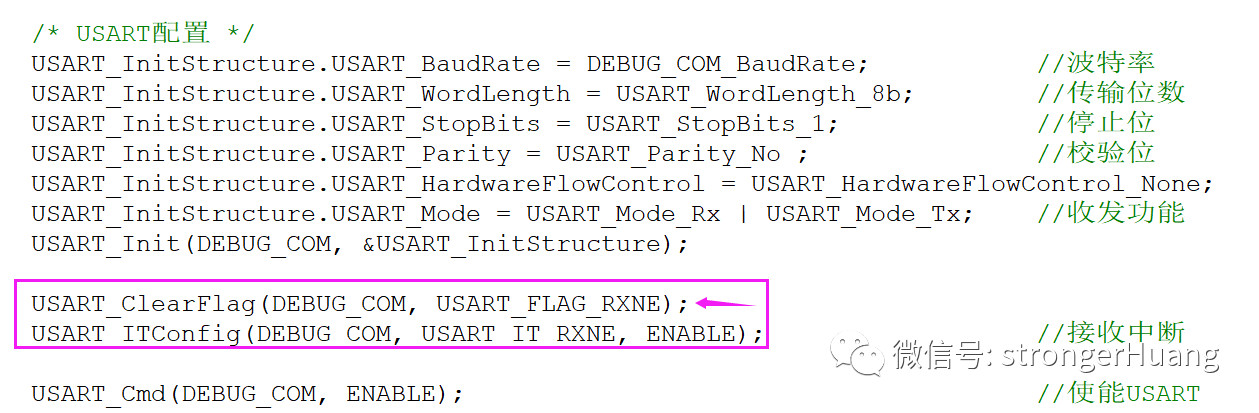

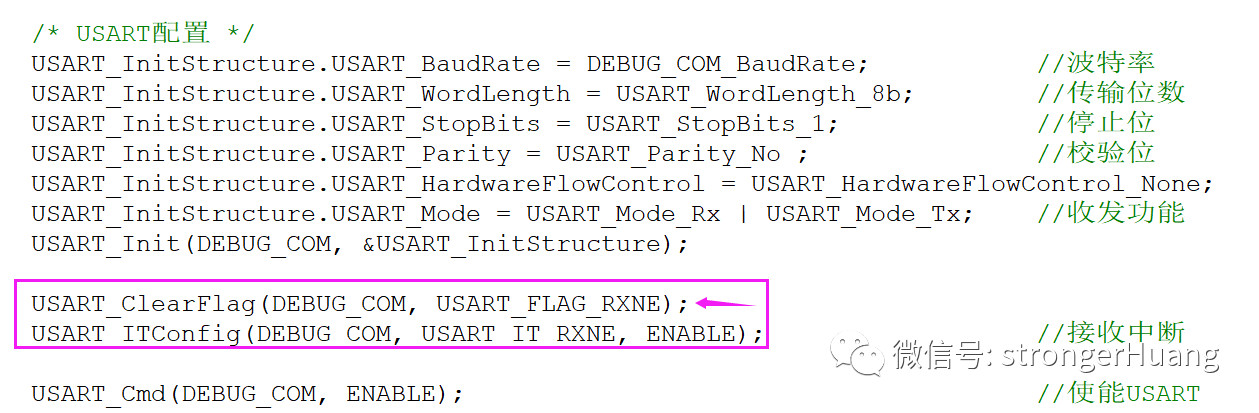

10025 STM32串口中断、DMA接收的几点注意地方

2020-03-04 13:57:48 19929

19929 在USART文章中讲解了串口的轮询和中断模式,本文介绍一下通过DMA模式控制串口传输。

2020-09-23 11:08:10 10189

10189

项目做到一半,碰到个尴尬问题:PWM使用的DMA通道与串口接收的DMA通道撞车了,咋办?考虑一下,决定放弃idle中断+dma的串口不定长数据接收方案,回到中断接收去。

2022-02-16 11:35:02 2347

2347

一种基于FPGA的RFID读写器设计

2021-04-19 08:55:07 6

6 项目做到一半,碰到个尴尬问题:PWM使用的DMA通道与串口接收的DMA通道撞车了,咋办?考虑一下,决定放弃idle中断+dma的串口不定长数据接收方案,回到中断接收去。

2021-04-27 06:00:08 12

12 、DMA 申请等。所有 TIME2 的中断事件都是通过一个 TIME2 的中断通道向 STM32 内核提出中断申请,那么 STM32 中如何处理和控制 TIME2 和它众多的、不同的、中...

2021-11-15 14:06:04 0

0 单片机I/O设备的控制方式主要有三种:程序循环检测、中断驱动和直接内存访问。

2021-11-23 17:51:42 3

3 学习stm32中断、DMA通信原理和编程方法。使用stm32tubemx和HAL库分别完成以下编程练习:(1)用stm32F103核心板的GPIOA端一管脚接一个LED,GPIOB端口一引脚

2021-11-23 17:51:43 12

12 一:什么是DMA?1.DMA简介: DMA,全称为:Direct Memory Access,即直接存储器访问。DMA 传输方式无需 CPU 直接控制传输,也没有中断处理方式那样保留现场和恢复

2021-11-25 09:51:10 4

4 学习stm32中断、DMA通信原理和编程方法。使用stm32tubemx和HAL库分别完成以下编程练习:(1)用stm32F103核心板的GPIOA端一管脚接一个LED,GPIOB端口一引脚

2021-11-26 10:21:04 3

3 学习stm32中断、DMA通信原理和编程方法。使用stm32tubemx和HAL库分别完成以下编程练习:(1)用stm32F103核心板的GPIOA端一管脚接一个LED,GPIOB端口一引脚

2021-11-26 12:06:05 7

7 文章目录一、中断1.关于中断2.实例一按键控制LED3.实例二串口通信二、DMA编程三、总结四、参考资料一、中断1.关于中断1)什么是中断中断是处理器和外部设备的数据传输方式,一方通过申请中断的方式

2021-11-26 12:21:04 8

8 目录DMA通信原理DMA的基本介绍DMA工作原理STM32的DMA结构DMA的主要特性DMA寄存器列表DMA进行数据传输的必要条件中断实验练习STM32用HAL库点亮LED灯任务要求实验过程采用串口中断

2021-11-26 19:21:11 12

12 结果Ⅲ-DMA向上位机发送数据DMA1.创建STM32CubeMX工程2.keil代码修改3.结果小结链接Ⅰ-中断方式点灯中断中断通常被定义为一个事件,该事件能够改变处理器执行指令的顺序。这样的事件与 CPU 芯片内外部硬件电路产生的电信号相对应。中断是指计算机在执行期间,系统内发生任何非寻常的或非预期

2021-11-26 19:21:12 20

20 学习stm32中断、DMA通信原理和编程方法。使用stm32tubemx和HAL库分别完成以下编程练习:(1)用stm32F103核心板的GPIOA端一管脚接一个LED,GPIOB端口一引脚

2021-11-26 19:21:13 11

11 我看了很多DMA2D教程都是用阻塞方式来刷新屏 这样就消耗了性能 相当于没用DMA 所以我使用DMA2D中断来传输数据测试平台stm32f429 + 正点原子7寸1024x600液晶屏 45MHZ

2021-12-02 17:06:07 37

37 STM32 串口使用IDLE中断+DMA接收(HAL库函数)一、开发环境单片机型号:STM32H743IIT6工程配置环境:STM32CubeMX 6.3.0固件库:STM32CubeH7

2021-12-02 21:06:07 37

37 程序使用DMA传输,需要使用DMA传输完成中断,程序如下:void DMA2_Stream7_IRQHandler(void){ static u16 cnt

2021-12-04 17:21:05 7

7 控制器实现和完成优点:无需CPU控制 或 中断压栈-出栈过程,让RAM与IO设备间可快速传输数据,减少CPU负载stm32f4资源双AHB总线,一个用于存储器访问,一个用于外设访问编程接口仅支持32位访问的AHB使用DMA最多2个DMA控制器,总共2*8=16个数据流,每个DMA控制器用于管

2021-12-04 18:36:12 12

12 一、STM32中断使用NVIC 中断优先级管理Nested Vectored Interrupt Controller,嵌套向量中断控制器。CM3支持256个中断,16个内核中断,240个外部中断

2021-12-06 20:36:05 0

0 本篇博文基于完成嵌入式实验的目的,具体内容如下:学习stm32中断、DMA通信原理和编程方法。使用stm32tubemx和HAL库分别完成以下编程练习:1. 用stm32F103核心板的GPIOA

2021-12-06 20:36:06 11

11 一、STM32中断使用NVIC 中断优先级管理Nested Vectored Interrupt Controller,嵌套向量中断控制器。CM3支持256个中断,16个内核中断,240个外部中断

2021-12-07 10:51:11 7

7 目录一.中断模式编程1.STM32cubeMx项目创建2.Keil修改代码3.运行结果二.串口中断1.STM32cubeMx创建项目2.Keil修改代码3.烧录并运行程序三、DMA方式

2021-12-14 19:07:07 2

2 方法:一种是 :IDLE 接收空闲中断+DMA一种是: IDLE 接收空闲中断+RXNE接收数据中断都可完成串口数据的收发知识点介绍:STM32 IDLE 接收空闲中断功能:在使用...

2021-12-20 19:39:04 30

30 stm32作为从机,fpga作为主机。进行spi通信。stm32使用dma进行数据接收。在dma中断中进行接收数据和处理。通过调节fpga里面spi数据的发送频率。来保证stm32实时处理数据,做出控制相应。下面是fpga抓取到的spi信号。...

2021-12-22 19:29:34 90

90 STM32F407串口空闲中断+DMA空闲中断,DMA简介空闲中断区别于普通串口中断的每一字节数据进入一次中断的中断方式,空闲中断在一帧数据接收完成之后才会触发中断进行数据处理。使用空闲中断的好处

2021-12-24 18:50:00 28

28 如何来优化?比如四轴飞行器,当在不停地获取姿态控制方向时,又要去接收串口数据.答:使用DMA,无需CPU中断便能实现接收串口数据1.DMA介绍DMA,全称为: Direct Memory Ac...

2021-12-24 19:01:52 5

5 STM32中断与DMA通信编程中断模式编程CubeMx创建项目Keil修改代码串口中断cubeMX创建项目Keil修改代码DMA方式Keil修改代码总结参考中断模式编程用stm32F103核心板

2021-12-24 19:06:57 10

10 一.DMA介绍DMA详细介绍请转博客:嵌入式:初次了解STM32的USART串口通讯(中断方式)_LaiYiFei25的博客-CSDN博客DMA框图二.串口通信要求1)设置波特率为115200,1

2021-12-24 19:08:19 11

11 1. 串口为什么要使用DMA?好处?stm32单片机的串口没有FIFO,使用字节中断的方式去接收,会频繁进入中断,影响系统实时性。好在stm32的串口可以级联DMA使用,在大数据量连续发送/接收

2021-12-28 19:16:03 13

13 传送到外设,一般都要通过CPU控制完成,如CPU程序查询或中断方式。利用中断进行数据传送,可以大大提高CPU的利用率。 2:中断传送是由CPU通过中断服务程序来传送,每次要保护断点,保护现场需要多条指令,每条指...

2021-12-28 19:22:30 11

11 如果单片机不支持串口空闲中断和DMA,可以参考之前写的,串口只用接收中断,完成不定长的分包。这里以stm32L4的单片机举例,思路可拓展到GD32等支持DMA和串口空闲中断的单片机。串口DMA接收

2021-12-28 19:26:34 19

19 一、STM32中断使用NVIC 中断优先级管理Nested Vectored Interrupt Controller,嵌套向量中断控制器。CM3支持256个中断,16个内核中断,240个外部中断

2022-01-14 15:37:59 1

1 目录一、STM32中断1、何为中断2.中断相应的过程3.中断的优先级二、高低电平控制LED灯的亮灭三、中断实现串口通信四、实现用DMA连续向上位机发送数据五、总结六、参考资料一、STM32中断

2022-01-14 15:49:01 1

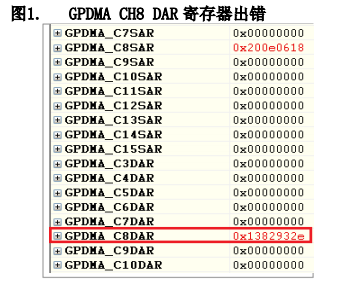

1 某客户发现修改代码后,STM32U59 SPI DMA 发送未产生传输完成中断,但修改的代码跟 SPI 以及 DMA 毫无关联。

2022-09-01 12:11:13 4434

4434 电子发烧友网站提供《安路ELF2 FPGA内置FLASH读写控制.pdf》资料免费下载

2022-09-27 09:32:18 2

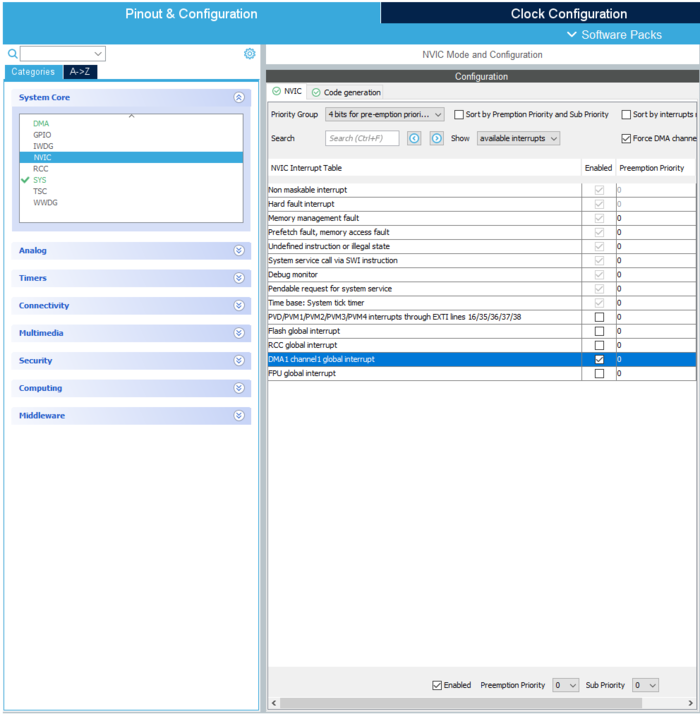

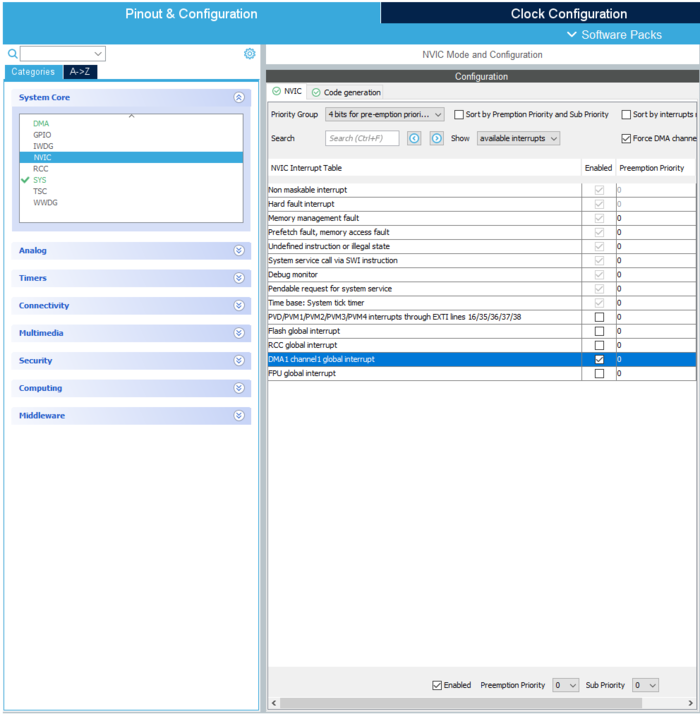

2 要使用中断配置 DMA,请按照内存到内存模式部分中详述的步骤进行操作。 在System Core 》 NVIC中启用DMA1 Channel 1 Global Interrupt如下图所示

2023-03-23 15:23:53 1713

1713

本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 745

745

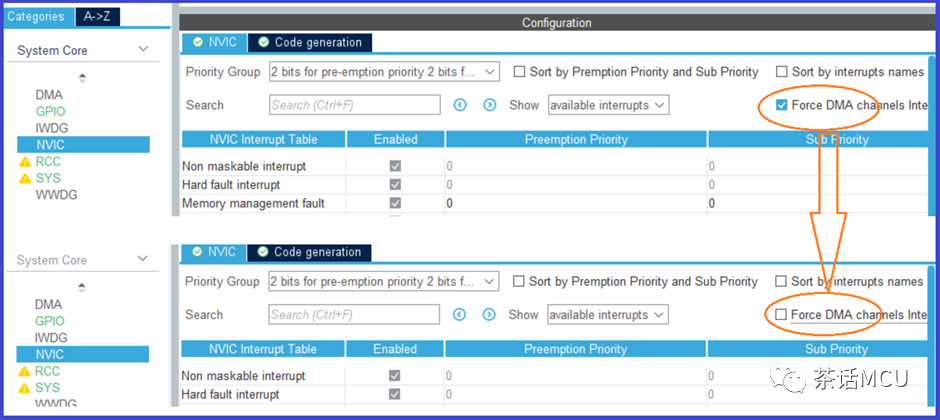

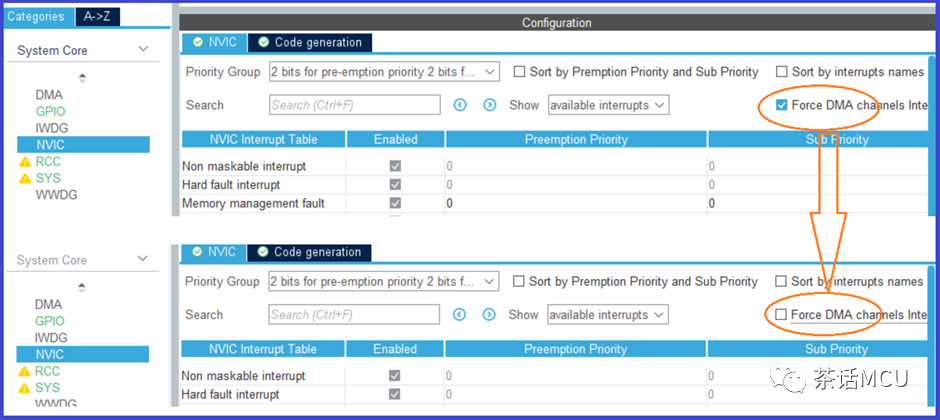

能不能在CubeMx配置界面将DMA中断的默认使能关闭? 这里再顺便分享一个跟CubeMx配置有关的话题。目前来看,我相信对不少人还是有帮助的! 我们在使用CubeMx对STM32芯片做初始化配置

2023-09-09 16:01:11 919

919

DMA不产生传输完成中断

2023-10-18 16:44:03 616

616

LPC5500_SDK例程:串口DMA发送+中断接收

2023-10-30 16:59:44 477

477

STM32串口中断及DMA接收常见的几个问题

2023-10-26 16:41:12 2296

2296

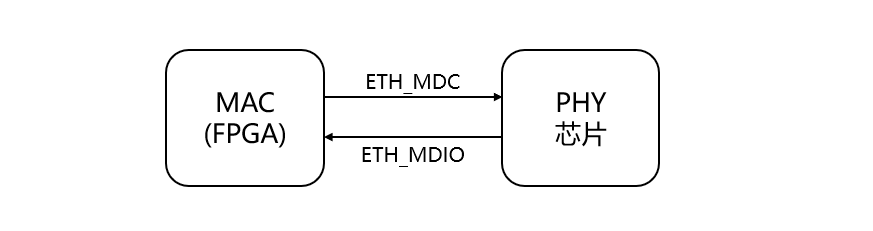

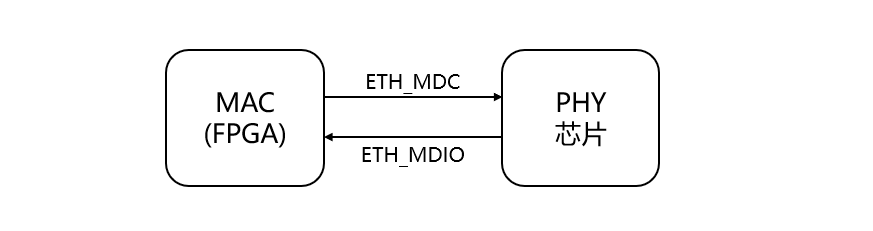

本文开源一个FPGA项目:MDIO接口读写测试。以太网通信模块主要由 MAC (Media Access Control)控制器和物理层接口 PHY (Physical Layer)两部分构成。其中

2023-10-01 09:46:00 983

983

电子发烧友网站提供《STM32L462 SDMMC DMA多次循环读写.pdf》资料免费下载

2023-09-19 15:11:45 0

0 用户使用STM32G473RET6芯片,开发环境STM32CubeMX+Keil(LL库)。使用DMA1通道1,在半传输中断和完全传输中断里,拷贝ADC采集的数据。在应用过程中发现DMA半传输中断和完全传输中断不能独立使用。

2023-12-01 09:19:48 797

797

DMA简介DMA控制器的作用不仅在增强系统性能并减少处理器的中断生成,而且还针对32位MCU应用程序专门优化设计。DMA控制器为存储器到存储器,存储器到外设和外设到存储器的传输提供了7个通道。每个

2024-02-22 08:13:55 148

148

正在加载...

电子发烧友App

电子发烧友App

评论