本文首先会对这个问题进行一般性地分析,在此基础上我们将以德州仪器公司 10G SERDES 器件 TLK10002 为例,提出一个新的解决方案,即采用双时钟模式提供 SERDES系统时钟,并且探讨

2013-09-26 14:34:31 3258

3258

GMII、SGMII和SerDes的区别和联系? GMII和SGMII区别,上一篇已经介绍了,这一篇重点介绍SGMII和SerDes区别。 GMII和SGMII SGMII接口 SGMII

2020-10-09 11:31:29 29959

29959

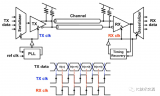

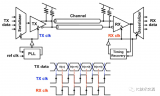

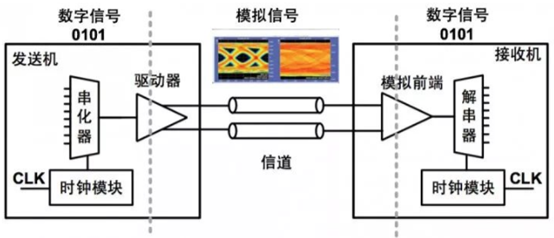

SerDes是串化(Serializer)和解串(Deserializer)的简称,下图给出了PHY的简图。发送端发送并行数据,时钟由ref_clk经过PLL锁相环振出的时钟提供,经过差分对信号传输至接收端,通过CDR恢复时钟并解串数据。

2023-08-16 17:19:23 2740

2740

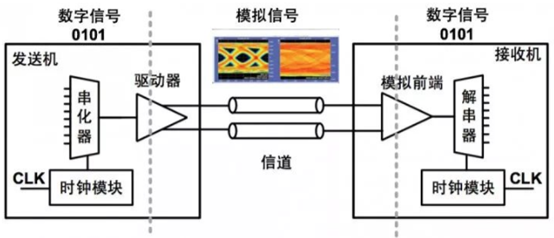

SerDes是SERializer(串行器)/DESerializer(解串器)的简称,是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。

2023-11-14 09:32:39 2479

2479

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。

2024-01-04 09:04:02 495

495

亲爱的Xilinx论坛,我正在实现基于SERDES协议的序列化传输。我需要在Kintex7上接收8个差分对,这些差分对承载由另一个Kintex7串行化的64位字,主时钟为100MHz。将托管FPGA

2020-03-17 09:53:11

/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道

2019-05-29 17:52:03

用户在产品选型和方案设计之初,对于硬件接口资源分配不熟悉,不遵守芯片规范使用导致项目出现问题,造成了严重损失。本期我们就此系列平台的SerDes资源分配做一篇文章。LS系列产品的资源不可为不丰富,其中最让人头晕的当属于SerDes协议。百度百科这样解释,SERDES是英文SERializer(串行器)/DE

2021-12-20 06:01:37

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。从PCI到PCI Express, 从ATA到SATA,从并行ADC接口到JESD204, 从RIO

2021-07-28 07:02:12

SerDes的发送端TX的均衡原理是什么?怎样利用高速接口SerDes去实现芯片间信号的有线传输?

2021-06-17 07:15:16

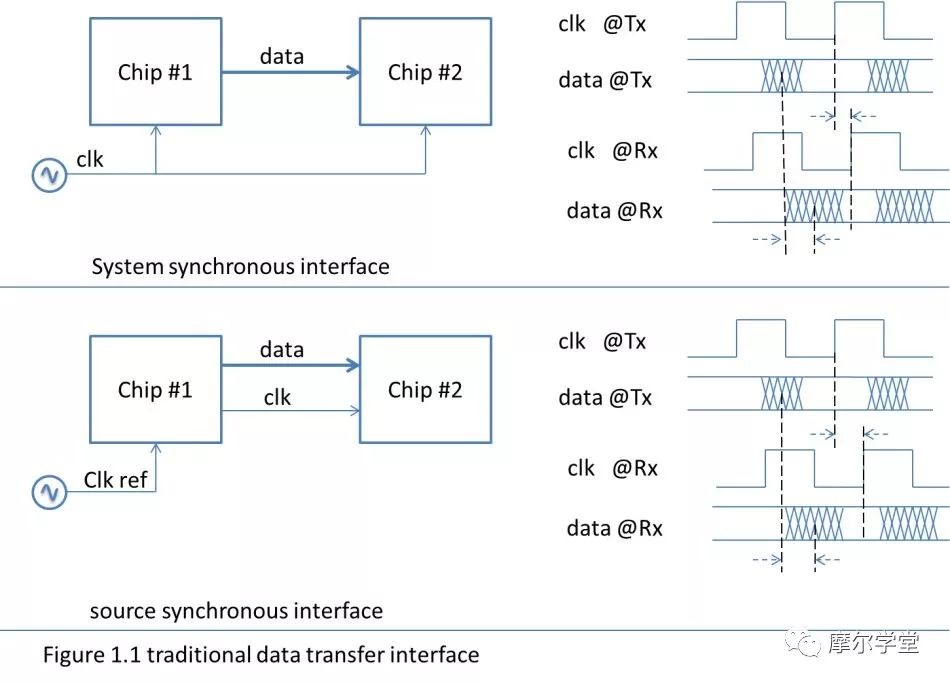

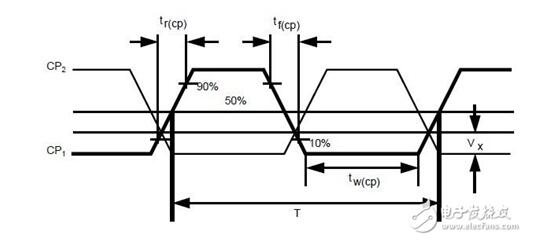

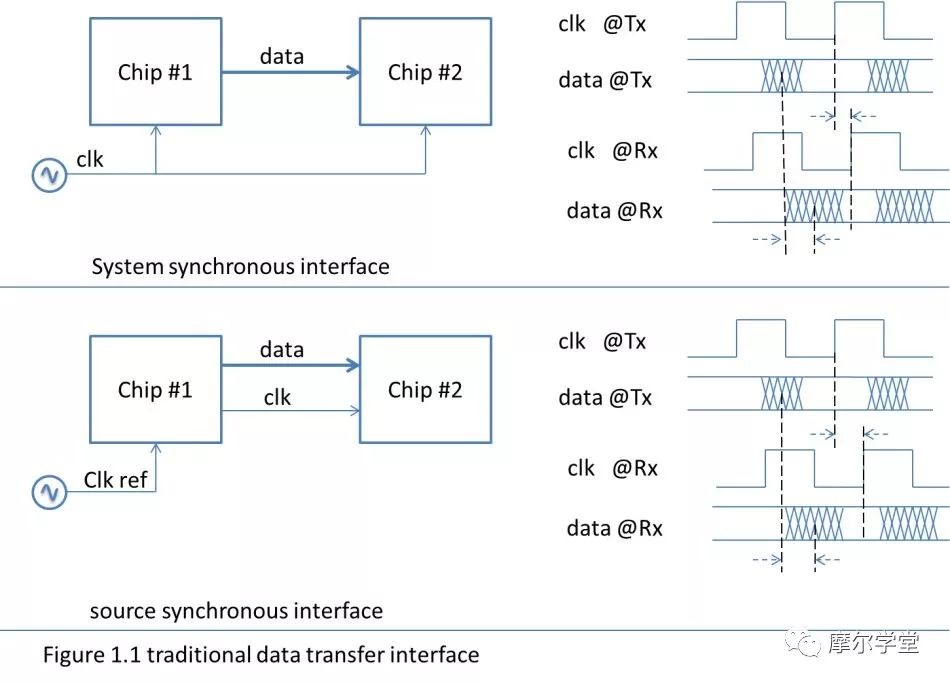

一、SERDES的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。随着接口频率的提高,在系统同步接口方式中

2021-07-26 07:33:44

一、SERDES的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加。a)、时钟...

2021-07-28 08:35:42

1.时钟频率是什么?时钟:顾名思义,时钟以精确和固定的时间间隔,触发电信号,其信号被控制单元用于推进CPU的内部操作。而CPU执行 取指令–解码–执行的速度为时钟速度(时钟频率)。在各类CPU当中每

2021-11-30 07:17:35

如题,9176DAC的PLL锁上了,证明时钟应该没问题,但是为什么DLL和serdes PLL锁不上呢?配置顺序,我是按照手册的START-UP SEQUENCE进行配置的。

2023-12-01 06:54:09

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-10-23 07:16:35

SerDes在93000平台上量产测试。本文将介绍Nautilus UDI方案是如何实现高速SerDes测试的,包括UDI结构,输入时钟设计,Load board设计,socket选型等多个测试环节。

2021-05-10 06:58:55

,频率为8MHz。 ②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。 ③、LSI是低速内部时钟,RC振荡器,频率为40kHz。 ④、L

2021-08-23 08:09:59

,SERDES-Ratio是7:1。我不能简单地将时钟乘以7,因为这使我得到154MHz,低于VCO的频率范围(400-1080MHz)。相反,我乘以21.从462MHz产生的频率很好。从这个频率我产生四个频率

2019-08-06 09:34:57

您好,Virtex7的SERDES运行的最大频率是多少?请问,有人可以帮我这个吗?在此先感谢,最好的问候

2020-07-30 17:20:12

大家好。BUFG资源和DCM / PLL模块在许多FPGA线路上使用专用时钟布线资源。对于SerDes应用,我们使用BUFIO2来获得DDR SerDes IOCLK,SerDes Strobe

2019-07-30 10:35:37

大家好, 在一个I / O块中有一个主serdes和一个slave serdes。如果我使用主设备,奴隶不能使用,是不是?谢谢。最好的祝福。

2020-06-08 15:03:22

什么是SerDes?

2021-06-24 07:52:02

嗨, 我计划在我的设计中使用SERDES(LVDS)作为背板。我已经浏览了virtex5用户指南中的advnced IO部分,并看过ISERDES_NODELAY和OSERDES宏。我已经看到了一些

2020-07-13 15:54:49

320ps的0.35 UI就是120ps)。一种常见的建立片上3.125GHz SERDES时钟的方法是利用一个精确的输入参考时钟,时钟频率为1/10的SERDES速率或312.5MHz。该参考时钟

2019-05-21 05:00:13

我正在使用IBert生成2.5 Gbps(PCIX)比特流; PCIX需要100 MHz参考时钟。在IBert时钟选项,系统时钟设置中,您可以将频率选项设置为10 MHz至100 MHz,我相信此值

2020-05-27 14:09:19

约束将无法在时序分析期间返回任何路径”,因此,当我们使用输入SerDes时钟资源来生成DDR时钟时,我们不会期望任何分析甚至是建立/保持违规的通知。2)在同一白皮书中,“OFFSET约束不优化由内部

2019-08-09 09:54:33

如何修改系统时钟频率?如何查看系统时钟频率?

2022-02-14 07:09:48

Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。

2019-10-21 07:09:44

SerDes的基本结构是由哪些部分组成的?怎样去更好地使用SerDes?

2021-09-22 06:25:17

SerDes是怎么工作的?SerDes有传输时钟信号吗?

2021-10-18 08:53:42

SERDES的作用有哪些?SerDes的主要构成可以分为哪几部分?

2021-10-18 09:25:08

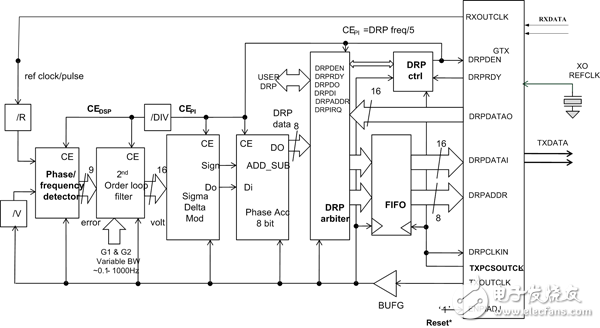

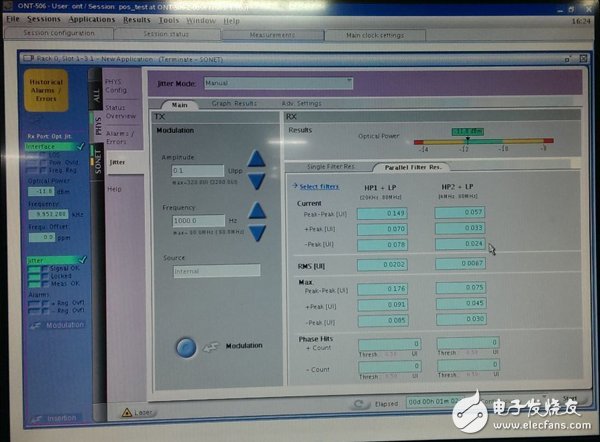

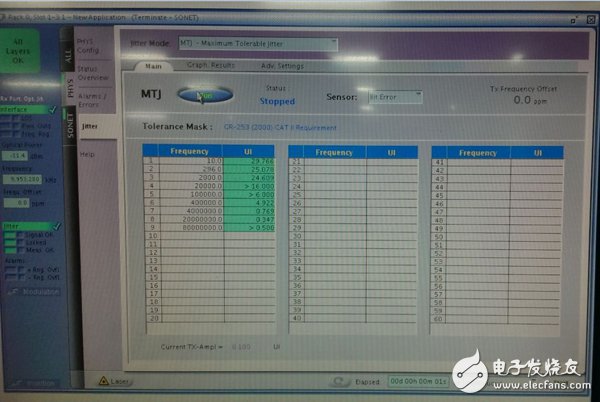

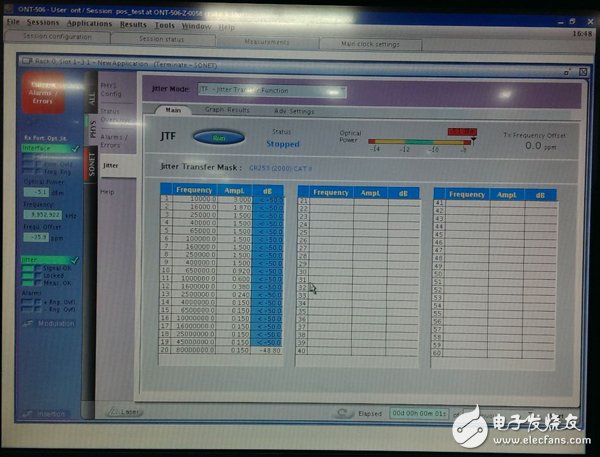

漂移及漂移形成的原因是什么?光纤漂移引起的SERDES FIFO溢出问题分析BBU SERDES 双系时钟方案及具体实现

2021-04-19 08:35:11

的serdes?2、如果serdes是各自的,是否共享输入时钟?(外部时钟,对于我们来说是156.25MHz)3、在研究SRIO速率配置时发现文档中描述:serdes的输出时钟不能超过3.125GHz,该描述是否准确?是否适用于所有的serdes模块?谢谢!

2018-08-06 06:17:36

6678中的srio的serdes和以太网的serdes是共用还是各自有自己的serdes?

2018-08-02 06:11:31

[size=150%]F题 发挥部分(2)题目要求本振信号频率可变,是要求本振频率自动跟随还是手动改变?

2018-07-23 00:22:35

时钟,用于块存储器写入或数据比较等。核心gen使用bufg缓冲来自aBUFIO2_2CLK的clk_div。除了使用更高频率的时钟管理器资源并同步两个频率域之外,是否有一种可接受的方法在结构中使用该

2019-06-19 06:38:52

大家好,我正在尝试实现一个可以处理内部高时钟频率的serdes,即。 1.2 GHz,当处于DDR模式时,我到目前为止所做的是将DCM输入时钟连接到25 MHz晶振时钟并将其乘以8以获得连接到DDR

2019-08-02 06:10:13

的参考时钟。让我们来看看SerDes模块的时钟结构。SerDes的参考时钟源有2个,SYSCLK或者外部输入的REF_CLK。SYSCLK是固定100MHz的频率,当SerDes参考SYSCLK

2020-10-28 17:15:14

是输入到SerDes的参考时钟。让我们来看看SerDes模块的时钟结构。SerDes的参考时钟源有2个,SYSCLK或者外部输入的REF_CLK。SYSCLK是固定100MHz的频率,当SerDes

2020-11-01 20:21:02

M31 SerDes PHY IP M31 SerDes PHY IP为高带宽应用提供高性能、多通道功能和低功耗架构。SerDes IP支持从1.25G到10.3125Gbps的数据速率

2023-04-03 20:29:47

射极跟随器原理及应用射极跟随器(又称射极输出器,简称射随器或跟随器)是一种共集接法的电路见下图,它从基极输入信号,从射极输出信号。它具有高输入阻

2010-01-14 15:06:43 132

132

射极跟随器

射极跟随器(又称射极输出器,简称射随器或跟随器)是一种共集接法的电路

2009-05-23 12:05:59 4295

4295

射极(源)跟随器,射极(源)跟随器原理是什么

射极跟随器又叫射极输出器,是一种典型的负反馈放大器。从晶体管的连接方法而言,它

2010-03-09 17:21:41 19179

19179 该应用笔记介绍如何根据STO超时、时钟频率和UART位时钟计算MAX9257/MAX9258可编程串行器/解串器(SerDes)的CCEN持续时间。

2011-07-30 22:55:13 1353

1353

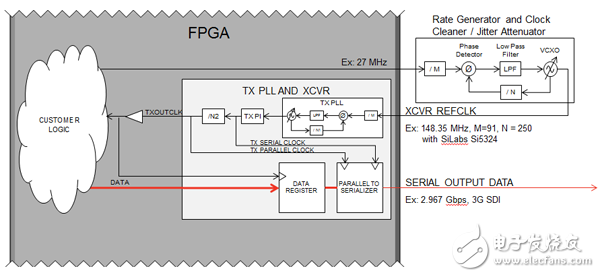

SERDES在数字系统中高效时钟设计方案,无论是在一个FPGA、SoC还是ASSP中,为任何基于SERDES的协议选择一个参考时钟源都是非常具有挑战性的。

2012-02-16 11:23:43 5384

5384

FPGA SERDES的应用需要考虑到板级硬件,SERDES参数和使用,应用协议等方面。由于这种复杂性,SERDES的调试工作对很多工程师来说是一个挑战。

2013-03-15 14:55:13 10360

10360

如何使用 HyperLynx DRC 来查找 SERDES 设计问题

2016-05-24 17:12:50 0

0 通常如果你的设计在较低时钟频率时通过了仿真,但是在较高时钟频率时却失败了,你的第一个问题应该是你的设计在某个较高时钟频率时是否达到了时序约束的要求。

2017-01-04 13:08:12 2107

2107

我们知道,SERDES对参考时钟有严格的相位噪声性能要求。通常,SERDES供应商会根据其SERDES采用的PLL以及CDR架构特点,以及性能数据,提出对参考时钟的相位噪声的具体要求。

2017-02-10 18:40:10 5965

5965

冲突、降低开关噪声、更低的功耗和封装成本等许多好处。而SERDES技术的主要缺点是需要非常精确、超低抖动的元件来提供用于控制高数据速率串行信号所需的参考时钟。即使严格控制元件布局,使用长度短的信号并遵循信号走线限制,这些接口的抖动

2017-10-26 15:37:45 4

4 时钟频率(又译:时钟频率速度,英语:clock rate),是指同步电路中时钟的基础频率,它以“若干次周期每秒”来度量,量度单位采用SI单位赫兹(Hz)。它是评定CPU性能的重要指标。一般来说主频数字值越大越好。外频,是CPU外部的工作频率

2017-11-10 14:21:26 23331

23331

)在单位时间内所出现的脉冲数量多少的计量名称;频率的标准计量单位是Hz(赫)。本文主要介绍什么是时钟频率及编程,具体的跟随小编一起来了解一下。

2018-04-28 09:49:46 42965

42965

CPU频率,就是CPU的时钟频率,简单说是CPU运算时的工作的频率(1秒内发生的同步脉冲数)的简称。单位是Hz,它决定计算机的运行速度。本文主要介绍cpu时钟频率计算公式及方法,具体的跟随小编一起来了解一下。

2018-04-28 10:32:58 32006

32006 和热裕量调整时钟频率。本文主要介绍的是时钟频率还能代表处理器性能吗?首先跟随小编来了解一下什么是cpu的时钟频率。

2018-04-28 16:42:56 7158

7158 的量产测试。那么,Nautilus UDI方案是如何实现包括UDI结构、输入时钟设计、Load board设计、socket选型等多个测试环节高速SerDes测试的呢?

2018-06-10 10:51:17 4434

4434

Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。

2019-05-24 15:33:25 4073

4073

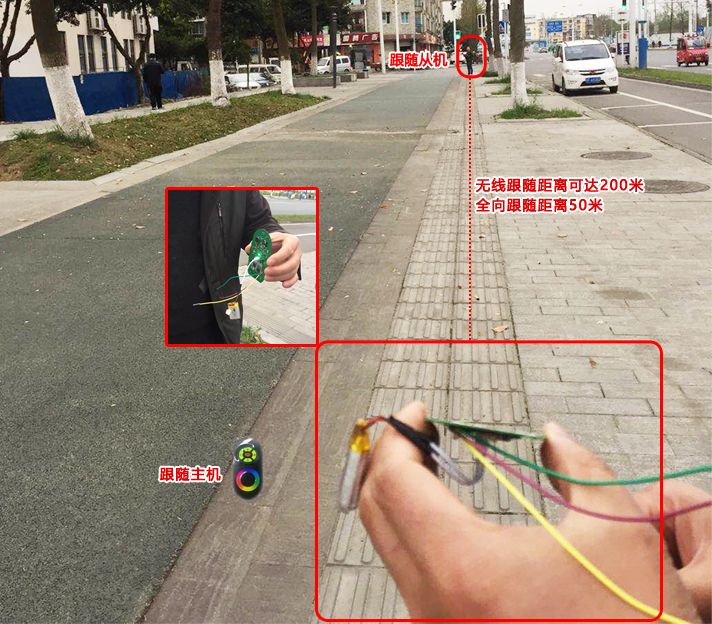

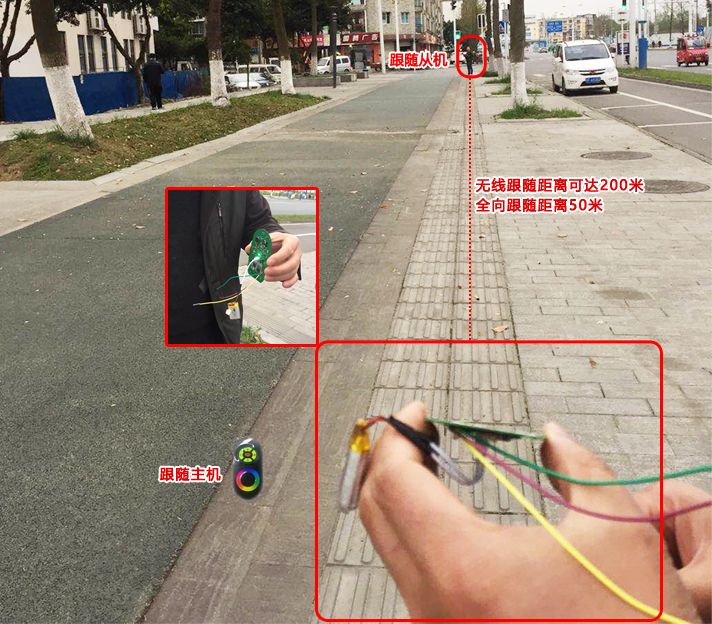

自动跟随又被称为自动跟随系统,可用于行李箱自动跟随、载货车自动跟随、购物车自动跟随、婴儿车自动跟随、无人机自动跟随、轮椅自动跟随、分拣车自动跟随、环卫车自动跟随、冲浪板自动跟随、高尔夫球包自动跟随等不同领域的跟随功能!

2019-10-14 16:25:04 5729

5729

cpu时钟频率的单位是Hz,是以【若干次周期每秒】来度量,因此量度的单位采用的是SI单位赫兹(Hz),目前主流电脑和手机的CPU时钟频率单位已经迈入了GHz的时代。

2020-05-14 09:43:51 9584

9584 随着SerDes 速度的增加,参考时钟所需的 RMS 相位抖动性能随之减少。在本次网络研讨会上,我们概述最新一代FPGA、光学DSP、相干DSP 和网络处理器的参考时钟要求,并重点介绍Si54x Ultra Series XO 和 VCXO 产品家族的关键功能

2020-11-03 17:13:10 2613

2613 为满足目前的56GPAM-4 SerDes技术,以支持更高带宽的100G+以太网和光网络设计。硬件开发人员通常需要100fs(典型值)以下RMS相位抖动规范的时钟。这些设计通常需要与CPU和系统时钟等其他频率时钟混用。

2020-11-12 15:25:55 4154

4154 为 VCU129 开发板提供的 BOARDUI.exe 可用于为板载 Si5348 时钟模块编写程序。默认频率为 156.25Mhz,该频率的设置文件在 BOARDUI 的 clockFiles 目录下提供。如何修改时钟频率?

2022-02-08 15:09:04 2924

2924 为了学习xilinx serdes 原语的使用,以及交流学习经验,在工程项目中方便的应用SERDES进行设计,故编写此文档。

2021-02-26 10:04:00 37

37 PLL设计和时钟频率产生机理免费下载。

2021-06-07 14:36:43 22

22 ,另一个优势是能够通过一对差分对信号引脚(而不是8、16、32或N个数据引脚和一个时钟引脚)发送数据。在串行传输这个方面得益于更小的数据包和更密集的pcb而节省了成本。具体取决于晶片成本、封装成本、PCB成本和PCB拥塞等因素。 距离优势 在过去的十年里,SERDES在PCB和基

2021-07-23 11:59:46 3795

3795 SerDes/Differential Pair-- The Feature of High Speed Designreference list– reference1:link 应对未来高速

2021-11-07 10:21:00 47

47 关于外部时钟晶振频率选择芯片的主晶振频率范围一般来说在数据手册(Datasheet)和技术参考手册(Technical Reference Manual)中都有介绍。你提到的时钟先分频再倍频,这个

2021-11-16 18:36:01 26

26 1.时钟频率是什么?时钟:顾名思义,时钟以精确和固定的时间间隔,触发电信号,其信号被控制单元用于推进CPU的内部操作。而CPU执行 取指令–解码–执行的速度为时钟速度(时钟频率)。在各类CPU当中

2021-11-20 15:36:02 10

10 机械周期、时钟周期、脉冲、晶振频率之间的关系晶振频率与脉冲的关系时钟周期与脉冲的关系机械周期与时钟周期的关系整理下学到的机械周期、时钟周期、脉冲、晶振频率之间的关系晶振频率与脉冲的关系晶振频率脉冲

2022-01-13 10:45:45 10

10 晶振频率是晶体振荡器的固有频率,而时钟频率是以时间为准的振荡频率,一个时钟周期等于两个振荡周期,所以晶振频率等于2倍时钟频率。那么这两个频率之间有什么区别?

2022-01-29 16:57:00 9435

9435 FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。

2022-10-31 11:28:41 1350

1350 SerDes 是空间到时间到空间的转换。并行数据同时传输但占用不同的物理互连,串行数据共享相同的物理空间但占用不同的时间时刻

2023-01-31 14:13:37 3369

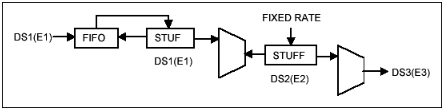

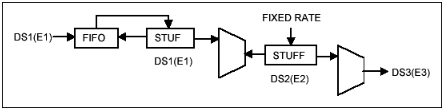

3369 在发射端,DS3(E3)时钟和DS1(E1)时钟由输入引脚派生,但DS2(E2)时钟频率是DS3(E3)时钟频率的一小部分。出于设计原因,分数将表示为整数比率,这取决于设备的模式。DS1(E1)时钟可以容忍基于DS3(E3)时钟频率和器件模式的频率范围。

2023-02-22 10:10:18 467

467

的。在使用SerDes的过程中,设计者有太多的疑惑:为什么在传输的过程中没有时钟信号?什么是加重和均衡?抖动和误码是什么关系?各种抖动之间有什么关系?时钟怎么恢复?等等这些问题,如果设计者能够完全理解

2023-03-16 10:28:11 1915

1915

同时介绍一种采用光电集成技术的,即采用光SerDes而非电SerDes的高速收发器。

2023-04-01 09:28:58 1078

1078 在IIC协议中涉及到两根线:SCL与SDA。SCL就是时钟信号线,SCL线上的频率就叫时钟频率。在对IIC总线进行学习与使用时,经常会听到设置IIC的时钟频率为xxxHz,或者设置IIC的数据传输率为xxxKbit/s。明明概念里可以进行配置的只有一个时钟频率,那么这个数据传输率这位老兄是怎么个情况。

2023-04-04 14:03:54 2614

2614 如何改变spi的时钟频率? 改变SPI的时钟频率需要以下步骤: 1. 选择合适的时钟源和分频器:SPI接口的时钟源可以是内部时钟或外部时钟,需要根据具体情况选择;同时需要根据所需的SPI时钟频率

2023-06-03 16:36:02 2130

2130 首先我们要了解什么是SerDes,SerDes的应用场景又是什么呢?SerDes又有哪些常见的种类?

2023-06-06 17:03:55 4707

4707

的特性,因此时钟将成对描述为DS3(E3)、DS2(E2)和DS1(E1)。本应用笔记阐明了发送时钟的频率容差、发送和接收时钟速率能力以及DS1/E1发送和接收时钟接口的详细信息。

2023-06-13 15:39:46 317

317

8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data Recovery,时钟数

2023-07-27 16:10:01 1566

1566

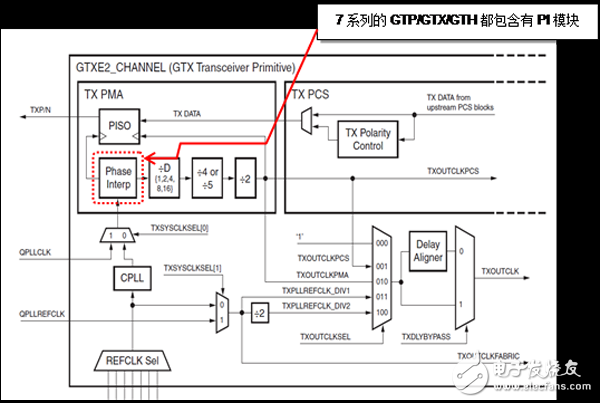

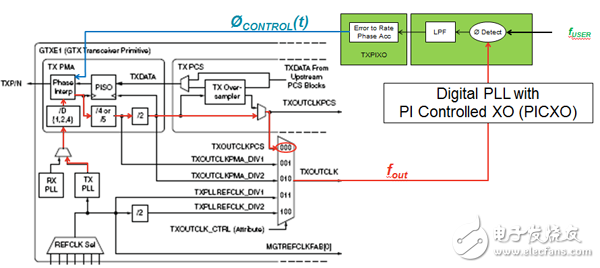

Xilinx公司的许多FPGA已经内置了一个或多个MGT(Multi-Gigabit Transceiver)收发器,也叫做SERDES(Multi-Gigabit Serializer/Deserializer)。MGT收发器内部包括高速串并转换电路、时钟数据恢复电路、数据编解码电路、时钟纠正和通道绑定电路

2023-07-29 16:47:04 468

468

在芯片设计中,为了便于定位故障,有时候需要确认部分时钟频率是否正确,需要部分debug手段。常见的方式是:将时钟信号引到芯片管脚,通过仪器测量。这类方式必须要测量仪器,并且需要熟练使用,耗时较长。还有一种简单的方式,通过时钟计数的方式判断时钟频率是否正确。

2023-09-20 14:17:06 385

385

的。在使用SerDes的过程中,设计者有太多的疑惑:为什么在传输的过程中没有时钟信号?什么是加重和均衡?抖动和误码是什么关系?各种抖动之间有什么关系?时钟怎么恢复?等等这些问题,如果设计者能够完全理解

2023-10-16 14:50:37 558

558

尽管设计和验证很复杂,SERDES 已成为 SoC 模块不可或缺的一部分。随着 SERDES IP 模块现已推出,它有助于缓解任何成本、风险和上市时间问题。

2023-10-23 14:44:59 449

449

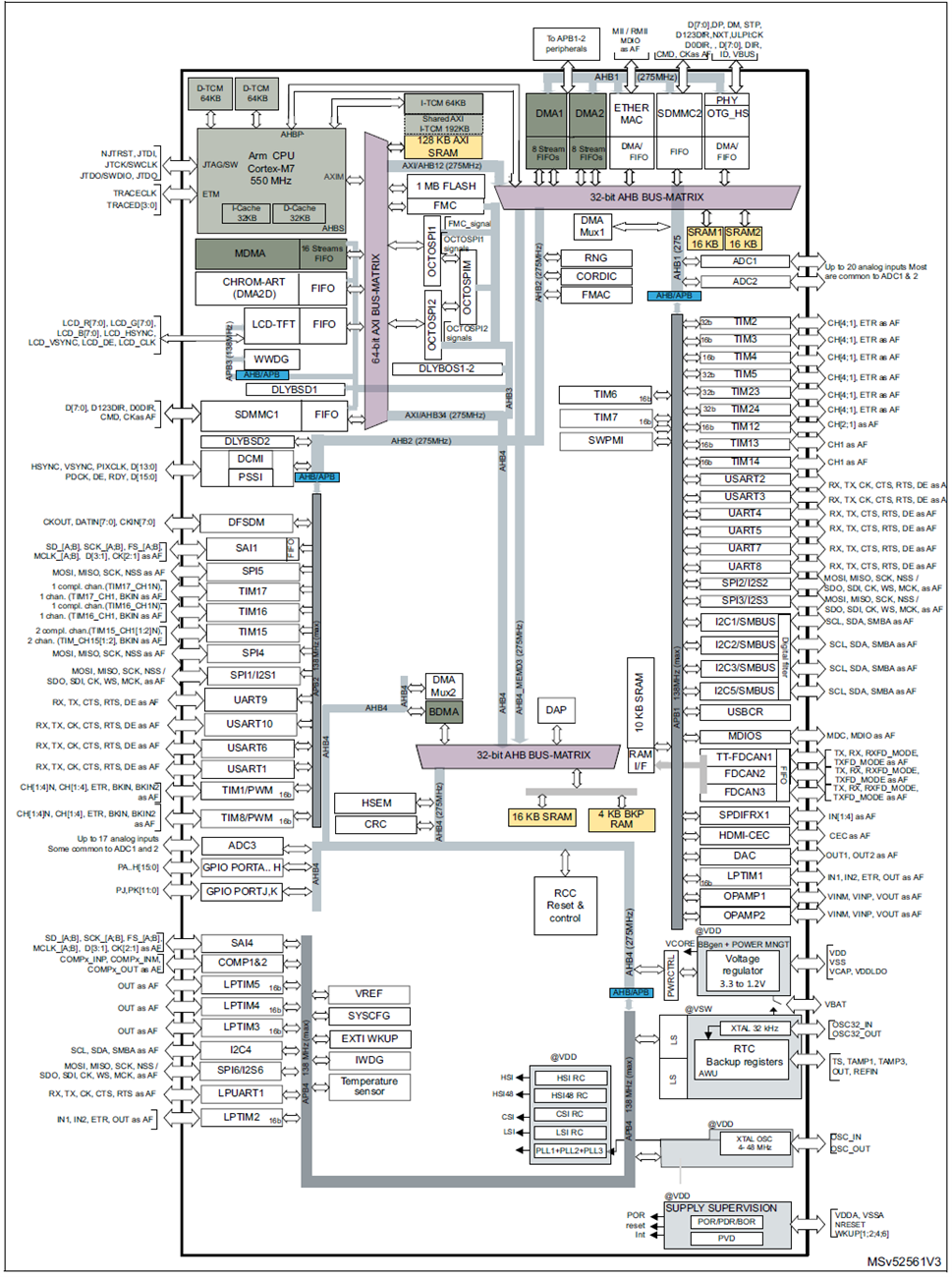

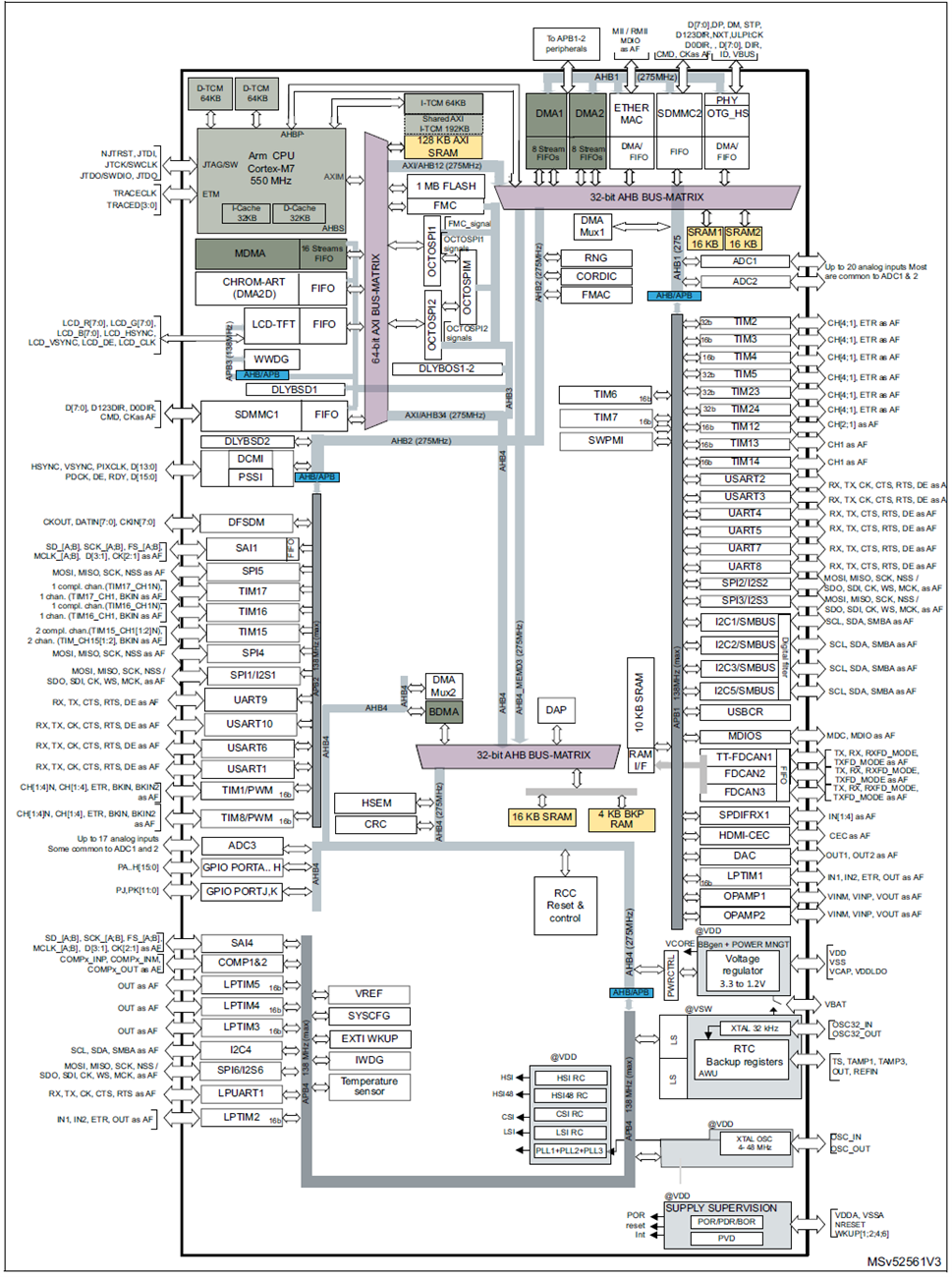

针对常规STM32系列性能测试所引起的准确度低、可靠性差、操作困难等问题,文中提出了一种关于I/O响应频率以及定时器最高频率的极限性能测试方法。通过对STM32H7时钟频率进行最高频率配置,分别

2023-10-24 14:51:18 674

674

电子发烧友网站提供《时钟和频率合成的应用领域.pdf》资料免费下载

2023-11-27 10:41:13 2

2 晶振频率和时钟频率本质上有何区别呢?时钟频率有什么作用? 晶振频率和时钟频率是两个相关但又有所不同的概念。下面我们将逐一介绍这两个概念的含义、区别和作用。 首先,我们来了解晶振频率。晶振是一种

2024-01-24 16:11:35 307

307

正在加载...

电子发烧友App

电子发烧友App

评论