Altera公司 (NASDAQ: ALTR)今天宣布,其28 nm Stratix® V GX FPGA已经收录在最新的PCI-SIG® Integrators名录中,符合PCI Express® (PCIe®) 3.0规范(Gen3)要求。

2013-05-23 10:34:54 1803

1803 ,2GB的DDR3。 6、标准JTAG接口。 7、支持BPI模式快速加载。 基于赛灵思的V7 的FPGA开发的PCIe DMA IP支持8.0Gbps(Gen3)at x8,x4,x2和x1的硬核,包括

2016-03-11 10:57:58

赛灵思的最新7系列FPGA芯片包括3个子系列,Artix-7、 Kintex-7和Virtex-7。在介绍芯片之前,先看看三个子系列芯片的介绍表,如下表1所示: 表1 全新Xilinx FPGA 7

2012-09-21 13:46:16

VIRTEX-5FPGA - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

我目前正在使用示例设计文件模拟virtex-7 690tffg1927-3 GTH。在以_exdes.v结尾的示例设计顶级文件中,我更改了参数EXAMPLE_SIM_GTRESET_SPEEDUP

2020-03-06 10:02:12

Layerscape MPU 中是否有支持 PCIe GEN3 16 通道的 EVB?

2023-05-30 08:01:56

(Spartan-6, Virtex-5 FPGA)和Gen 2、5.0Gbps/Lane(Virtex-6/7 Series FPGA)和Gen 3、8.0Gbps/Lane(Virtex-7

2015-06-21 13:38:12

, Virtex-5 FPGA)和Gen 2、5.0Gbps/Lane(Virtex-6/7 Series FPGA)和Gen 3、8.0Gbps/Lane(Virtex-7/UltraScale

2017-06-06 14:46:24

查看我使用我公司拥有的逻辑和协议分析仪捕获的PCIe GEN3跟踪时,没有迹象表明TLP摘要中的ECRC值存在问题。但是,当我在Windows 7笔记本电脑上查看保存的跟踪/配置.ala文件时,似乎

2018-11-05 10:31:03

描述 这款经验证的参考设计是一款 PCIe Gen-3 高速前端卡设计,旨在扩展 PCIe 子系统的 PCB 线迹距离。该电路板适合安装在主板与 PCIe Gen3 插卡之间的 x16 通道宽度

2022-09-21 07:43:27

你好。我使用GTH收发器(gen3,8x,refclk 100 Mhz)生成了用于PCI Express的Virtex-7集成模块,然后我尝试模拟

2020-08-07 10:03:37

“ID不匹配”错误。附件是日志文件。这是否意味着Virtex-7 FPGA可能因短路而损坏?如果是FPGA损坏,Xilinx有没有办法帮助修复它?或者,如果我可以配置Vivado硬件管理器在编程期间绕过ID代码检查?谢谢,健IDcode_test.txt 3 KB

2020-08-10 08:00:05

你好,我是与FPGA有关的初学者,但我对以下内容感兴趣:Xilinx Virtex-7 FPGA VC707评估套件我注意到PCIe插座是x8,但我的PC主板只有x16?两个插座兼容吗?问候,鲁道夫

2020-03-17 10:00:32

你好,我想获得Eval板“Xilinx Virtex-7 FPGA VC707评估套件”,但我有一些问题: - 我们是否必须通过LCD附近的接口将该板连接到PC,以便它能否工作?如果我们不这样做

2019-09-05 13:09:14

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3资料。

2016-05-27 16:39:58

嗨,我想在我的PCIe Gen3插槽上使用VC709,但它不起作用。首先,我的电脑规格:英特尔i7-4770(Haswell)华硕Z87 Pro-V三星DDR3 4GB x 4VC709连接套件

2019-09-09 10:40:29

提供 Virtex-4、Virtex-5、Virtex-6 、Virtex-7、 Kintex-7ZYNQ-7000系列等.. ALTERA优势产品系列:Stratix、 Arria、 Cyclone、 MAX、 Agilex系列等二手FPGA 货真价实

2019-07-28 17:47:39

(Virtex-6/7 Series FPGA)和Gen 3、8.0Gbps/Lane(Virtex-7/Kintex UltraScale FPGA)2. 自适应链路宽度,支持PCI Express x8

2015-11-11 15:06:39

描述这款经验证的参考设计是一款 PCIe Gen-3 高速前端卡设计,旨在扩展 PCIe 子系统的 PCB 线迹距离。该电路板适合安装在主板与 PCIe Gen3 插卡之间的 x16 通道宽度

2018-08-14 07:00:49

CFP2光纤以太网收发器模块相连接,板级的Virtex-7 H580T 3D FPGA用于接收以太网数据流,该FPGA通过4个工作在25Gbps的GTZ 28.05Gbps SerDes来跟两个

2017-02-10 17:19:24

我们如何使用Virtex-4 FPGA的Block-RAM来存储矩阵/ Vector的内容。例如,如何在BRAM中存储矢量A = [1 2 4 5 6 7 9 3]?OR矩阵B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-27 06:43:47

我们如何使用Virtex-4 FPGA的Block-RAM来存储矩阵/ Vector的内容。例如,如何在BRAM中存储矢量A = [1 2 4 5 6 7 9 3]?OR矩阵B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-29 09:16:36

我们如何使用Virtex-4 FPGA的Block-RAM来存储矩阵/ Vector的内容。例如,如何在BRAM中存储矢量A = [1 2 4 5 6 7 9 3]?OR矩阵B = [1 2 3 45 6 7 8 9 1 4 5 232 1]

2020-05-29 14:41:56

嗨,如何在Virtex-7 FPGA中实现动态部分配置?问候,Suresh Palani

2020-05-29 11:30:45

需要更多引脚,所以如果我们选择Virtex-7那么我将会放松永远。当我想在fpga本身生成数据而不是从PC将其传输到fpga时,我陷入了困境,因为目前我正在使用NDIS驱动程序执行此操作,没有人知道Windows何时会停止支持这一点。如果您能帮助我们对这两种设备进行比较,我将不胜感激。温暖的问候

2020-07-20 07:07:12

我试图在virtex 7而不是kintex 7上使用PRC的实验3(UG947),在更改.xdc文件以与VC709兼容后,我成功生成了比特流文件和prom.mcs(PIN I /使用(UG947

2020-08-07 08:15:27

Virtex-7 PCI Express Gen3集成块迁移到我的Kintex板并使其工作?我是否必须进行任何具体更改?先谢谢你!

2020-07-16 10:12:19

在我们的应用程序中,我们让多个Virtex-7设备通过SRIO相互通信。在UG476中,建议使用100nF交流耦合电容。在页307上,它指出:“发射器应交流耦合到接收器。交流耦合电容的推荐值为100

2020-07-28 10:43:01

对于VC707评估套件或VC709连接套件的Virtex-7“参考设计”中包含的内容,我感到很遗憾。具体来说,我想设计一个新的Virtex-7板。我习惯于其他大芯片的“参考设计”,其中参考设计包括我

2020-08-13 09:08:44

我需要一些帮助来评估Virtex-7演示板的性能。我有ML501板。我记得10%被用于系统架构和设备,如Microbleze,ports,.......我使用其他90%来执行特定的处理单元 - 30

2020-07-16 12:44:21

嗨,我正在通过JTAG为Virtex-7开发系统内配置。我已经阅读了7系列FPGAs配置用户指南,但没有关于JTAG指令以及单/多设备配置顺序的详细信息。在哪里可以找到Virtex-7的单/多设备配置顺序信息?

2020-05-29 12:35:45

你好我有一个在MIcroBlaze上运行linux的设计要求。我能够在我的Virtex-7 FPGA上下载比特流(在Vivado 2014.4中生成)。我使用Impact来编程我的FPGA。我因此

2020-04-02 10:05:40

嗨,我将UltraScale Architecture Gen3集成块用于PCI Express v4.1 ipcore作为端点。我生成了示例设计,并尝试使用测试平台进行仿真。在模拟中,没有数据包从

2020-04-22 08:15:39

嗨,我有一个virtex-7系列板,我还没有在互联网上找到引脚说明文档。我怎样才能为virtex 7分配引脚描述?

2020-07-26 19:37:58

你好,我正在开发一个在VC709开发板上使用Virtex7 FPGA的系统。该应用程序使用32Mb的板载Block RAM作为设计中的存储元件。 FPGA配置序列完成后,有没有一种方法可以使用PC上的JTAG / USB接口直接写入和读取Block RAM的内容?谢谢,

2019-09-29 14:00:01

`描述这款经验证的参考设计是一款 PCIe Gen-3 高速前端卡设计,旨在扩展 PCIe 子系统的 PCB 线迹距离。该电路板适合安装在主板与 PCIe Gen3 插卡之间的 x16 通道宽度

2015-05-08 11:31:58

SI52147-EVB,用于PoE无线接入点的时钟发生器评估板。 Si52147是一款符合PCIe Gen1,Gen2和Gen3标准的9端口PCIe时钟发生器

2020-08-27 14:27:11

嗨,我想检查7系列设备XC7K325T-2FFG900是否支持PCIE PHY GEN3?谢谢,

2020-07-25 08:11:39

我正在使用zynq芯片和VIRTEX-7设计电路板。我想知道在Zynq PL引脚和Virtex-7 IO引脚之间选择配置数据线(例如Slave SelectMAP X8,X16,X32)的方法。在

2020-06-05 10:31:19

嗨,我发现Vivado webpack版本v2014.4不支持安装在NetFPGA SUME板上的eh Virtex-7 690 FPGA。我想知道购买NetFPGA SUME板的任何许可证捆绑

2018-12-18 10:36:47

适用于Xilinx Virtex-7 FPGA开发板的32位DDR4 SDRAM

2020-12-30 07:39:14

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包软件。提供了一些基础的函数库以及常用的控制函数模块,配合

2022-05-19 09:16:05

赛灵思多平台Virtex-4 FPGA的性能及应用

赛灵思(Xilinx)的Virtex-4现场可编程门阵列(FPGA)是首款基于ASMBL(Advanced Silicon Modular Block)架构的多平台FPGA系列。通过采用不同的平台(LX、FX

2009-06-26 08:11:39 41

41 概述详情:Virtex@-7 T和XT FPGAs可在-3、-2、-1和-2L级速度等级,其中-3级性能最高。-2L器件在VCCINT=1.0V时工作,并被屏蔽以获得较低的最大静态功率。速度规格

2023-07-25 14:46:49

Kintex®-7 FPGA系列为您的设计提供28nm技术最好性价比, 同时为您提供高DSP比率, 高性价比封装, 以及支持PCIe® Gen3与10千兆以太网等主流标准. 与前一代相比, 新一代

2023-07-25 14:50:00

描述 Kintex®-7 FPGA 为您的设计在 28nm 节点实现最佳成本/性能/功耗平衡,同时提供高 DSP 率、高性价比封装,并支持 PCIe® Gen3 和 10 Gigabit

2023-11-10 14:22:14

赛灵思已向客户推出世界最大容量FPGA:Virtex-7 2000T。这款包含68亿个晶体管的FPGA具有1954560个逻辑单元,容量相当于市场同类最大28nm FPGA的两倍

2011-10-26 14:31:29 1491

1491 Virtex-7 2000T FPGA的容量是市场同类最大28nm器件的2倍,而且比赛灵思最大型Virtex-6 FPGA大2.5倍。虽然2000T由4个切片组成,但它仍然保持着传统FPGA的使用模式,设计人员可通过赛灵思工具流程

2011-10-26 09:11:30 2795

2795 Altera公司(Nasdaq: ALTR)宣布,成功实现28-nm Stratix® V GX FPGA与PLX®技术公司(Nasdaq: PLXT) ExpressLane™ PCI Express® (PCIe®) Gen3的互操作

2011-12-14 09:28:09 677

677 赛灵思宣布Virtex-7 H580T开始发货常见问题解答,Virtex-7 HT采用赛灵思的堆叠硅片互联 (SSI)技术,是提供业界带宽最高的 FPGA

2012-05-31 17:59:14 1871

1871

任何一种 split 交易协议都存在 Requesters 得不到期望的 Completion 的风险。为了允许 Requesters 使用一种标准方式从这种情况下恢复,规定了 Completion timeout机制。 PCIE 规范规定发出需要 Completions 的 Requests 的 PCIE 设备必须实现 Completion Timeout 机制。配置 Requests 除外。PCIE 设备每发出一个需要 Completions 的Requests,Completion timeout 机制被激活。PCIE Root Complexes, PCI Express-PCI Bridges, 和 Endpoints 需要实现 Completion timeout 机制。Switches 不需要主动发起操作。

2017-11-18 13:13:50 1994

1994

赛灵思近日推出内置28Gbps收发器的Virtex-7 HT系列支持下一代100-400Gbps通信系统应用适用于行业最高带宽线路卡的全新FPGA, 可以提供多达16个28Gbps串行收发器,可支持主要的高速串行、光学和背板协议,这里以QA形式对这一新品进行了深度解读。

2017-11-24 20:42:02 2426

2426 Virtex-7 485T I/O处理能力

2018-06-05 13:45:00 2618

2618 Virtex-7 485T DSP处理能力

2018-06-05 02:45:00 3246

3246 Virtex-7 485T功耗演示

2018-06-05 02:45:00 3159

3159 赛灵思Virtex-7 2000T 演示

2018-06-05 01:45:00 2632

2632 Virtex-7 GTH 收发器与Altera Stratix V GX 收发器的功能对比情况

2018-06-06 01:45:00 3572

3572

Xilinx公司全球最大容量芯片Virtex-7 2000T 性能演示。

2018-06-04 13:47:00 5120

5120 Virtex-7 FPGA系列旨在满足宽带通信、高阶无线基础设施、高端数字广播、雷达图像处理及其它航空航天和军用产品等关键细分市场应用需求。Virtex-7为这些应用提供了高容量、高吞吐量、低时延、低功耗、可扩展等优异特性。

2018-06-04 01:47:00 5349

5349

Xilinx公司介绍Virtex-7 X690T GTH Demo。

2018-05-22 13:47:47 8473

8473 赛灵思Virtex-7 GTX收发器演示

2018-05-24 13:49:00 4199

4199 在Virtex-7 x690T FPGA中首次公开演示集成PCI Express x8 Gen3端点功能

2018-11-21 06:06:00 3213

3213 ICHEC讨论了FPGA对HPC应用的适用性,并重点介绍了能够利用特定FPGA上所有DSP的器件的最佳数据模式。

利用Xilinx Virtex-7 FPGA和Kintex KU115,ICHEC充分利用了re

2018-11-20 06:42:00 2425

2425 Virtex-7 H580T FPGA与CFP2光模块连接

2018-11-20 06:05:00 3379

3379 演示运行x8 Gen3 PCI Express Link的Xilinx Kintex-7 FPGA KC705板。

2019-01-04 11:30:00 3877

3877 查看UltraScale FPGA中集成的PCIe Gen3模块的性能演示。

第一个演示显示了PCIe链路上的最大数据吞吐量;

demo#2利用现成的DMA引擎和软件驱动程序来代表典型的用例。

2018-11-28 06:22:00 3464

3464 Virtex-7 GTH收发器与Altera Stratix-V GX器件Battle Kits Demo

2018-11-30 06:31:00 2787

2787 观看Xilinx 28nm FPGA系列中第二款器件的演示 - 高性能Virtex-7 XV485T。

2018-11-30 06:26:00 3271

3271 Virtex®-6 FPGA内置支持PCIExpress®Gen2兼容接口。

本视频介绍了在ML605评估套件上运行的用于PCI Express技术的Virtex-6 FPGA集成模块的三个演示。

2018-11-22 06:30:00 2820

2820 通过Virtex-7 2000T FPGA中的GTX收发器实现高速串行性能。

2018-11-22 06:27:00 3461

3461 Virtex-7 H580T是全球首款全可编程异构3D FPGA,具有最高速度的低抖动28Gbps收发器。

2018-11-22 05:55:00 3475

3475 用于virtex™-7 FPGA GTX收发器的Chipscope™Pro ibert核心是可定制的,设计用于评估和监控virtex-7 FPGA GTX收发器。该核心包括在FPGA逻辑中实现的模式

2019-02-25 16:43:08 15

15 大程度地实现差异化。 Virtex-7 FPGA拥有多达96个高级串行收发器,使设计人员能够将突破性的带宽构建到下一代通信解决方案中。Virtex-7 FPGA可提供多达200万个逻辑单元和超过5TMACS DSP的吞吐量。这些资源支持大规模并行数据处理体系结构,这些体系结构在每个时钟周

2020-06-05 13:55:40 1522

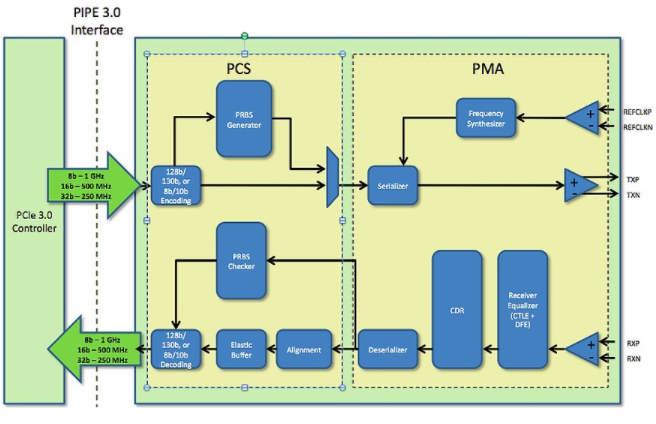

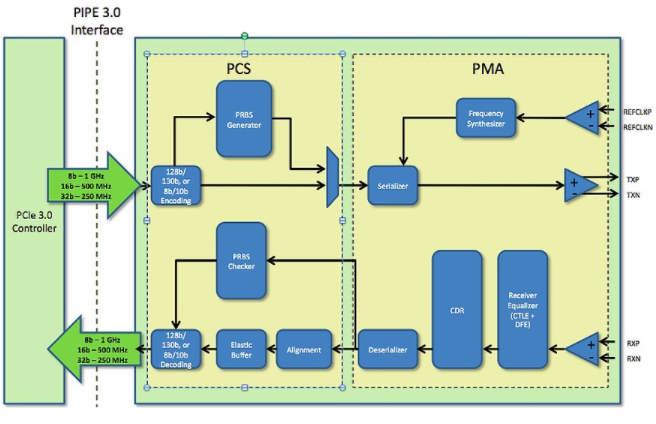

1522 借助128b/130b 编码方案和加扰多项式,PCIe Gen3 提出了许多传输和接收问题,所有这些问题都在最新规范中得到解决。

2022-06-14 15:27:59 1592

1592

ON Semiconductor Gen3 扫描 LiDAR 演示器的性能测量和模型验证

2022-11-15 20:12:52 0

0 电子发烧友网站提供《UltraScale+ FPGA Gen3集成模块.pdf》资料免费下载

2023-09-15 14:26:00 0

0 高通骁龙8 Gen3基于台积电N4P工艺制程打造,CPU部分包含1颗Cortex X4超大核、5颗Cortex A720大核和2颗Cortex A520小核,CPU主频最高为3.19GHz,集成了Adreno 750 GPU。

2023-10-15 11:03:15 1164

1164 高通骁龙8 Gen3旗舰芯片已经确定将搭载在多款手机上,其中包括小米14系列、一加12系列、真我GT5 Pro、魅族21系列、红魔9系列、荣耀Magic6系列、OPPO Find X7系列等。

2023-10-24 16:53:10 952

952 随着骁龙8 Gen3在小米14系列的首秀开始,11月注定会是骁龙8 Gen3终端刷屏的月份,各厂商纷纷交出自己对骁龙8 Gen3的阅读理解,仿佛谁不是首批搭载,谁就要成为那个被“美式霸凌”的显眼包。

2023-12-06 09:41:52 307

307

据悉,本次发布会的亮点之一是全新的旗舰级芯片——骁龙8s Gen3。此芯片将作为骁龙8 Gen3之后的次高端产品面世,而搭载它的首款设备可能就是小米Civi 4手机。

2024-03-13 09:59:09 113

113

电子发烧友App

电子发烧友App

评论