在占用极低资源的情况下轻松创建适合在DSP48E1Slice或逻辑中实现的高阶多相IIR滤波器。

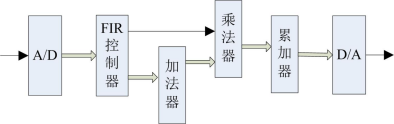

设计人员常常为自己的应用选择有限脉冲响应(FIR)滤波器,因为此类滤波器易于理解掌握且得到出色的设计与IP实现工具的支持。赛灵思FIR编译器是一种用于将MATLAB®生成的系数映射到DSP和FPGA逻辑资源中的理想工具。不过在大幅降低FPGA资源占用的情况下设计出能够满足特定滤波规范要求的无限脉冲响应(IIR)滤波器是可行的。选用IIR滤波器的主要弊端就是使用设计工具时需要掌握一些专业知识,通常后续还需要手动编写RTL代码。不过只要您完成滤波器的架构设计并以定点方式表达出来,利用像赛灵思System Generator这样的新型工具就能自动为您生成HDL。赛灵思的一篇相关白皮书中全面介绍了各种传统IIR滤波器[1]。

现在我们来了解一下如何在占用极低FPGA资源的情况下实现高性能多相IIR滤波器。这些滤波器结构特点在于NK+1阶的滤波器仅用K次相乘就能实现。此类滤波器对系数量化敏感度低,故可有效地以定点方式实现。此外滤波器级上任何节点的最大增益都是有界的,即中间计算只需要1位余量。这里我们提供的是一种通用架构,适合于实现流水线化并映射到赛灵思7系列器件中的DSP48E1Slice中。该架构包括一定数量的无乘法器五阶椭圆滤波器设计,适合在少量FPGA逻辑片中高效完成多相插值和抽取处理。

MATLAB能够将IIR滤波器设计分解成较低阶级联。这种较低阶级联与直接实现高阶差分方程的做法相比,拥有更加理想的数值特性。一般来说低阶滤波器选用的是二阶双象限段(SOS),其采用的是直接型1结构。每个SOS需要完成四次相乘、三次相加和部分舍入,以减少进入级联中用于下一个滤波器的位宽。对于定点实现一般还需要增加一个乘法器来实现段间缩放。

不过级联分解法对插值器或者抽取器来说并非是一种有效的架构,因为它没有发挥多相分解的作用。例如在插值过程中,在将输入数据应用到滤波器之前,需要先在样本之间插入N-1个零,实现输入数据上采样并将输入采样率提高到与输出采样率相等。但级联IIR滤波器由于每个SOS内存在的反馈路径,就无法通过插入零来降低计算量。

用于多相分解的IIR滤波器

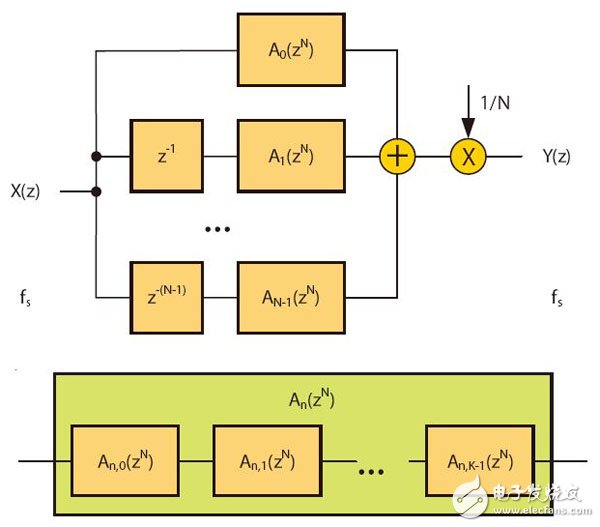

本文介绍的滤波器采用图1中所示的并联滤波器分解架构。在并联方式下,每个分支上的滤波器依次比上一分支多延迟1。此外每个分支中的滤波器限制为N带。每个分支的延迟数由输入/输出采样率决定,但每个An(zN)滤波器的项只涉及z-N幂数,就是说差分方程式只对每第N个输入/输出样本进行计算,而对之间的全部样本忽略不计。

传输函数为被延迟的N带全通滤波器An(zN)之和。即:

此外还可以把每一个全通滤波器表达为基本全通段的级联,如图1所示。设全通段的总段数为K,则H(z)的阶数为NK+1。即有:

图1:上面是IIR滤波器的并联形式;下面是由级联的基本滤波器组成的每个分支。

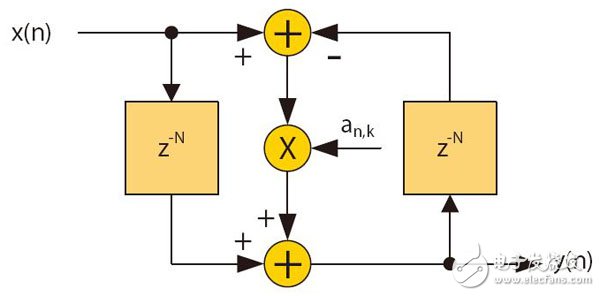

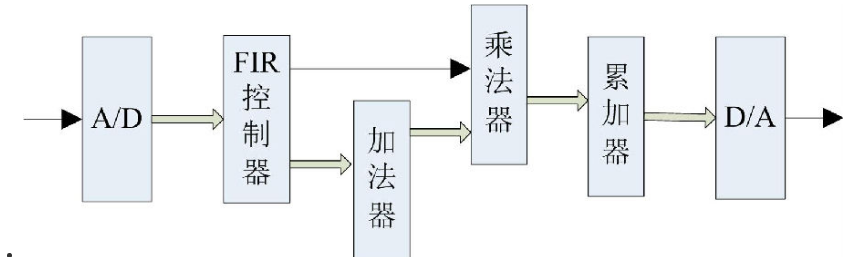

图2是在直接型1中实现的基本全通段。它由两个N-样本延迟元和一个单系数乘法器组成。除了便于使用标准的乘法器,使用直接型1还有其他优势。它能够高效地映射到DSPSlice中并在级联条件下共享延迟资源。

图2:基本全通段

插值和抽取

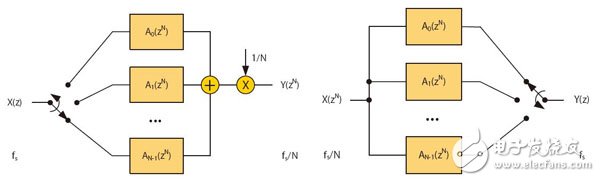

这种滤波器架构可以自然地映射为图3所示的抽取和插值结构中。这里用换向开关在更高采样率下切换到每个样本,取代了图1中所采用的延迟元。

对隔N插值和抽取的操作,我们既可以围绕图3提供的理想结构开展设计,也可以设计由质因数采样率转换组成的级联。分解为质因数[2]可以简化系数优化问题,因为自由变量的数量较少,且得到的滤波器级联十分接近理想状态。在许多应用中,需要的采样率转换为2的幂,可通过反复隔2插值或抽取来实现。为不失普遍性,我们先来验证N=2时的特例。

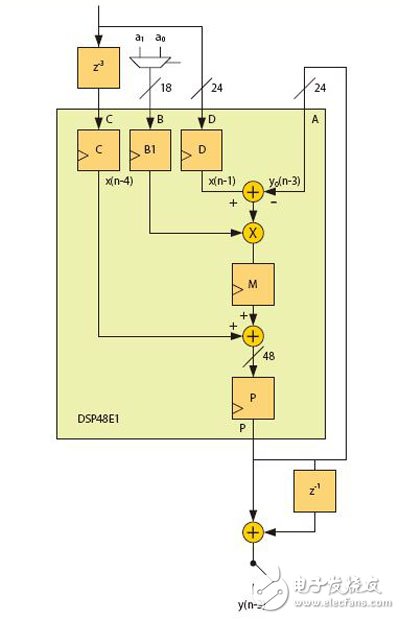

根据图3所示,N=2时低通滤波器总阶数为5,虽然它由两个二阶全通段和一个延迟元组成。现在应该明确的是,与使用SOS实现该五阶IIR滤波器所需的十个乘法器和八个加法器相比,在理想情况下本例只需要两个乘法器和五个加法器。如果考虑到是隔2抽取,即对每个输入样本只有一个分支处于活跃状态,那么还可以有更大程度的节省。这相当于把输入序列分为两个半采样率序列,分别为奇次样本和偶次样本。然后将这些样本应用到全通分支并加总。此外每个基本段内的延迟元可以在较低速率下运行 ,从而让存储需求减半。这个设计可以高效地实现流水线化并映射到一个DSPSlice,因为两个分支的输出滤波器可使用外部加法器进行累加。所以实现一个如图4所示的五阶隔2抽取IIR滤波器,只需要一个DSP48E1Slice。插值也存在类似的情况,由每个分支滤波器依次提供一个交织器的的样本。另外,支持隔2插值也只需要一个DSPSlice。

A、B、C、D和P端口依据赛灵思7系列命名法[3]。您可以级联DSPSlice来实现更高阶的滤波器,而且由于采用双分支结构,每个分支的流水线延迟相等。需要注意的是因为反馈路径只能延迟2,需要使用三个内部寄存器的DSPSlice无法完全实现流水线化且。与在输入端寄存相比,使用M寄存器可以在更高频率下运行且功耗更小。当N=3或者更大的数时,既可以采用让DSPSlice在最大频率下运行的做法,也可以采用让DSPSlice最大限度地实现流水线化的做法。后者可以通过让滤波器在双通道TDM模式下工作来实现,此时延迟元数量翻倍,A输入反馈路径使用Slice中的寄存器A1和A2,这样C输入之前的延迟就从3增加到5。

图3:抽取(左图)与插值(右图)

图4:隔2抽取,映射到赛灵思DSP48E1

量化和裕量

此类N带结构已被命名为波数字滤波器(WDF),因为它们可以模拟经典模拟滤波器中的双端无损梯形网络。文献中对此类含有椭圆响应的滤波器设计有全面的介绍。这种设计与用于模拟、数字域间转换的双线性变换相结合,为设计数字椭圆滤波器和巴特沃斯滤波器提供了有力的方法。使用梯形滤波器的另一个优势在于此类结构沿袭了对系数量化低敏感度的特性。这意味着要在不含劣化等纹波特性的情况下实现能满足100dB阻带需求的滤波器,系数使用18位的字长度绰绰有余。对基本段[4]稳态增益特性的分析,发现增益最低的算术节点的最大增益为2.0,且发生在预加法器的输出处。这对定点设计而言有着显著的意义,因为它意味着我们只需要在预加法器输出增加1位即可。在赛灵思DSP48E1Slice内的预加法器输出没有饱和逻辑存在,故将A和D的输出限制为24位可以防止滤波器的运行发生数字溢出,以及更为重要的是,让运行达到DSPSlice的最大内部精度。虽然稳态增益被限制在2.0,阶梯响应下的瞬态会超过2.0,因此建议只使用23位,为安全运行留出裕量。对某些数据源,比如说24位音乐而言,您可利用预先知晓的信号特性,应用完全的动态范围。

如果输入数据不足24位,应在字中左对齐,因此会产生部分分数位。例如,对于16位输入数据而言,理想的选择是留出1位保护位、16位数据位和7位分数位。与浮点相比,一般只需要3到4位分数位就足以实现理想的精度。

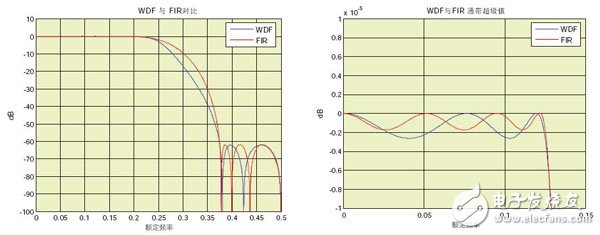

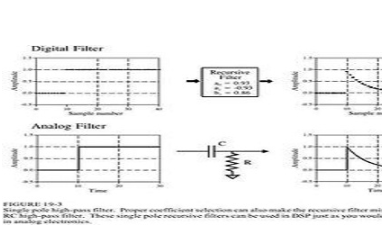

图5:满足相同阻带(左图)和通带(右图)规范的21阶FIR滤波器和五阶WDF

生成滤波器系数

R.A. Valenzuela和A.G. Constantinides[5]的专著中已充分介绍了采用双分支结构实现为任何阶数椭圆滤波器生成系数的方法。图5所示的是一种标准化通带为0.125的五阶(两个系数a0=0.1380,a1=0.5847)WDF滤波器,与使用帕克斯-麦克莱伦算法设计的22抽头FIR滤波器相比,它能够满足相同的通带纹波和阻带衰减指标。结果表明滤波器阶数通常下降到原来的1/4,且与FIR所用的11个乘法器相比(考虑对称因素),WDF只需要两个乘法器。

在半带WDF中,阻带和通带纹波并非互不相干。不过通过合理设置阻带衰减就能得到可忽略不计的通带纹波。例如图5中的滤波器的通带纹波为10-6dB。FIR的优势在于能够单独设定这两个设计参数,这样在给定阶数的情况下,可以设定较高的通带纹波来帮助满足阻带需求。

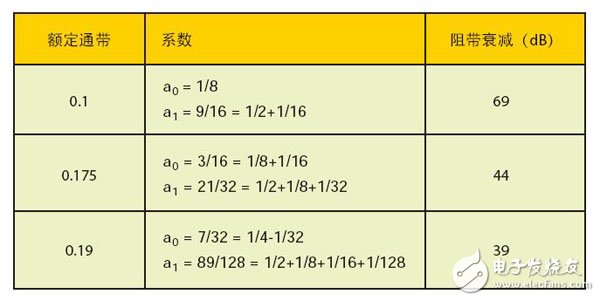

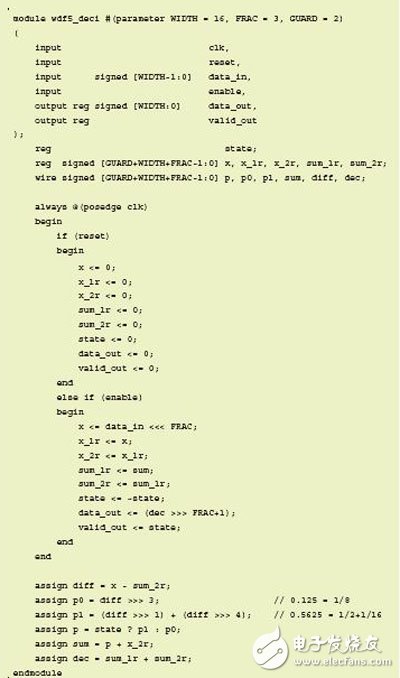

接下来我们来验证一下如果不使用DSP48E1,而是通过高度量化系数在部分LE中实现滤波器情况会得到什么。回顾一下,由于WDF滤波器以模拟梯形滤波器原型为基础,那么针对特定的通带我们应该能够找到低位密度的系数。比特 应尽量以标准分解方法写入,从而最大程度地减少加法器的数量,如表1所示。

表1 - 三种样本通带的量化系数

虽然0.19通带的五阶滤波器的阻带衰减已经不错了,但是将两个这样的滤波器简单级联就可以得到阻带为-78dB的10阶滤波器。例如表1中的第一个抽取器可以用图6中给出的少许几行Verilog代码来实现。

图6:实现表1中第一个抽取滤波器的Verilog代码

有效资源

我们已经展示了自然而然映射到插值和抽取中的IIR滤波器构建。该结构比IIR二阶段甚至FIR都拥有更多有效资源。它能充分映射到DSP48E1Slice的预加法器/乘法器/后加法器中,且对于18位系数的定点量化效应十分稳健,从而给出可控制的100dB阻带。一些无乘法器五阶设计可允许用于特定通带宽,可将其映射到一些逻辑寄存器和加法器中以降低DSP资源占用。

参考文献:

1. 赛灵思白皮书WP330,《赛灵思FPGA中的无限脉冲响应滤波器结构》,2009年8月;

2. 作者:P.P. Vaidyanathan,《多速率系统和滤波器组》,Prentice-Hall出版社,纽约州Englewood Cliffs,1993年;

3. 《赛灵思7系列DSP48E1 Slice用户指南》,1.5版本,2013年4月3日;

4. 作者:Artur Krukowski,Richard Morling,Izzet Kale,《多相位N路径IIR结构量化效应》,IEEE仪器测量汇刊,第51卷第6号,2002年12月;

5. 作者:R.A. Valenzuela和A.G. Constantinides,《高效率插值抽取数字信号处理方案》,电子电路和系统,IEEE会议记录第G部分第130卷第6号,1983年。

电子发烧友App

电子发烧友App

评论