引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。

2022-07-22 09:46:39 682

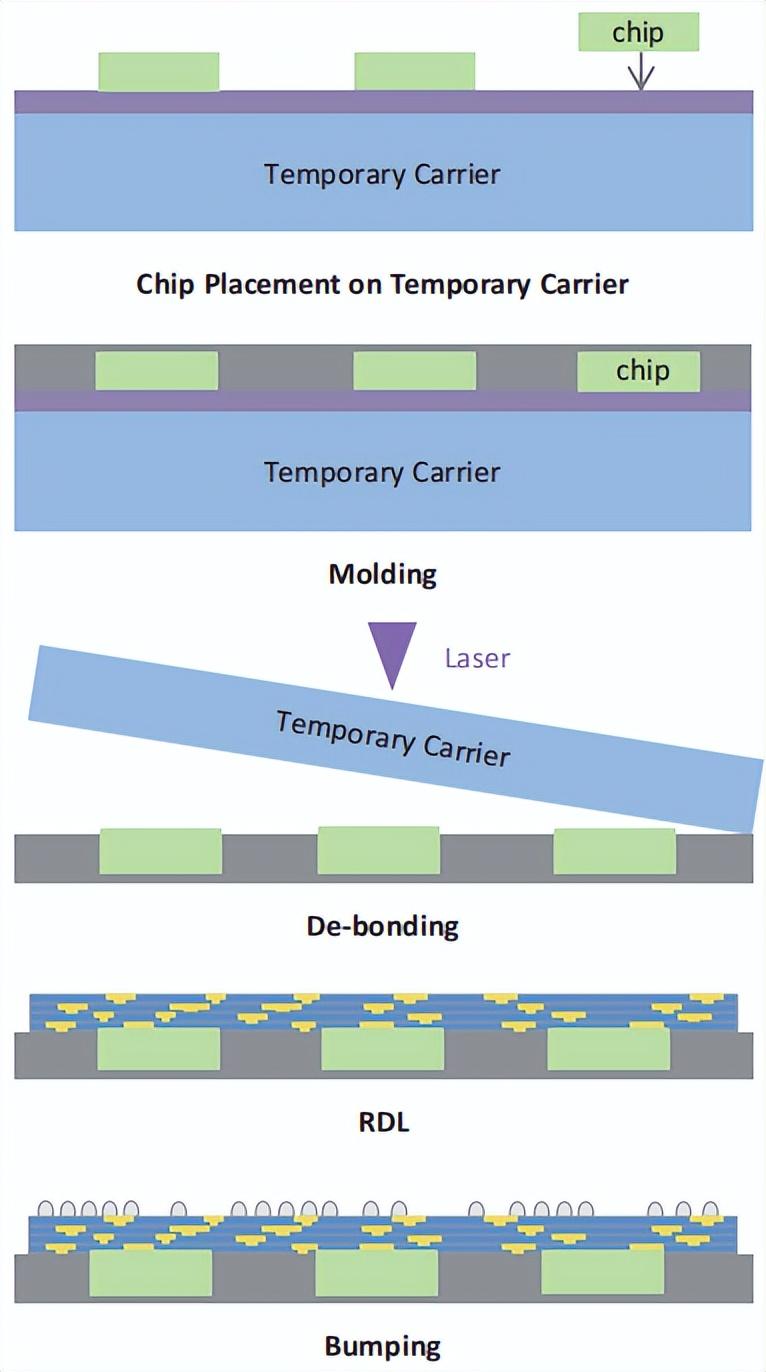

682 ),通过RDL替代了传统封装下基板传输信号的作用,使得扇出型封装可以不需要基板而且芯片成品的高度会更低,所以扇出型封装的发明初衷其实是降低成本,而且由于扇出型封装在封装面积上没有扇入那么多限制,整个封装设计也会变得更加灵活和“自由”。因此扇出封装最先在一些小面积、低性能的领域被推广开来。

2023-11-27 16:02:01 2459

2459

14.2节提到的问题①,即设计中有很大的扇出,对于如何获知该扇出信号有多种途径。常见的途径是通过FPGAEditor(Xilinx)或者Fitter里Resource Section

2024-03-20 17:33:34 491

491

本文的目的是了解为什么Deca的扇出技术最近被高通用于其PMIC扇入WLP die的保护层。严格的说,这仍旧是一个扇入die与侧壁钝化所做的扇出封装。因此,本文的第一部分将描述扇入式WLP市场以及

2019-07-05 14:21:31 7031

7031 会有比较详细的结构图,因为是新人对于找资料解决问题,还是比较弱,往往无从下手)2. 想对FPGA的IO,设计成可配置的形式,可以当普通IO口使用,有输入输出,也可以配置成复用模式,可配置成复用功能,复用输入功能好像会遇到扇入的问题,大家有没有比较好的思路。

2015-10-31 20:13:49

本人菜鸟,求FPGA入门级资料,谢谢{:1:}

2014-01-16 23:56:48

几个不错的资料哦,给大家共享下《FPGA系统设计的主要思路和方法初探》.pdf (766.25 KB )FPGA验证简介.pdf (255.69 KB )FPGA经验总结(精华).doc (1.03

2019-05-27 02:11:57

FPGA毕竟不是ASIC,对时序收敛的要求更加严格,本文主要介绍本人在工程中学习到的各种时序约束技巧。 首先强烈推荐阅读官方文档UG903和UG949,这是最重要的参考资料,没有之一。它提倡

2020-12-23 17:42:10

我想在fpga上做一个报文解析的功能,就是将一串01数据发送给FPGA,然后fpga对数据进行报文解析,然后再将解析后的数据发送给电脑,想问各位大神解析模块应该怎么写?有没有相关的资料可以参考的???急求???

2017-11-13 16:04:16

fpga初学资料,刚开始看感觉不错,分享一下

2013-12-03 19:14:55

fpga教程之华为verilog教程下载ModelSim SE 十分钟入门教程下载Mico32入门上手资料说明书完全下载Altera和Xilinx Modelsim仿真库 FPGA 管脚分配需要考虑的因素

2010-06-21 14:59:01

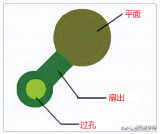

学习allegro 16.5 进行时,扇出使用的过孔问题请教,麻烦大家给答疑一下。谢谢了,祝大家劳动节快乐。看了于博士的视频,4层的板子,对BGA器件进行了扇出操作。1:为什么信号引脚和电源引脚扇出

2015-04-30 23:50:16

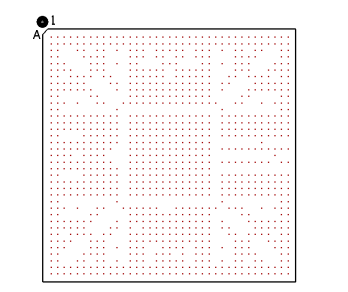

,我现在讲我的自动扇出步骤给大家说一下,在BGA上面点击右键,选择component atcions 然后选择fanout component,这是会弹出一个对话框,你要是不想要BGA的外边焊盘扇出

2015-01-07 16:07:17

Altium Designer 9,BGA扇出的时候,外面一圈焊盘出去的线不符合规则设置,我是对ROOM里的线宽设置的是6mil,外面的线是10mil,扇出时BGA外面一圈的焊盘引出的线是10mil,不知道是怎么回事?想删掉重新扇出,不知道怎么删,难不成要手动一个一个删?求高手帮忙!

2015-01-07 15:56:28

AD15做扇出时,选择如图,但是做出来的扇出是有很多没有扇出,多是GND,和一些POWER,在规则设置上,我把把有我Clearance都取消了,请大神赐教,感谢

2015-01-16 10:44:37

如上图所示,进行BGA fanout操作后,只有一小部分焊盘fanout成功,为何其他的焊盘没有任何反应?

2016-03-16 10:59:00

`BGA扇出报错`

2017-03-30 10:46:38

、选择BGA Fanout 的层:Setup/Layers Setup,BGA一般放在TOP Component 层,Plane Typet 选No Plane ,Routing 选 Any,然后“OK

2012-11-02 16:01:14

设置了BGA扇出之后,却连线不了,这是咋回事撒?求助各位~~

2012-11-21 10:20:41

IPTV DDR孔扇出,下边这和VIA孔怎么显示NO FEFALT

2019-09-30 05:36:43

原点座标,Setup/origin.二、选择BGA Fanout 的层:Setup/Layers Setup,BGA一般放在TOP Component 层,Plane Typet 选No Plane

2019-06-10 10:05:00

PADS中 BGA Fanout扇出 教程

2013-09-14 21:31:46

PCB 布线是先扇出还是先摆器件? 先摆器件 有的靠的太近 扇出会出现错误

2016-01-25 23:18:18

示意图第一步,点击执行菜单命令 Route-Create Fanout,进行扇出,如图 5-123 所示;图 5-123执行自动扇出示意图第二步,执行自动扇出的命令之后呢,还需要对参数进行设置,如图

2020-04-21 08:00:00

概述:MAX3845是TMDS® 2至4扇出开关和电缆驱动器,用于高达1.65Gbps的DVI™或HDMI™信号的多显示器分配。输入输出均为TMDS标准信号,符合DVI和HDMI标准。因为TMDS为

2021-05-17 07:06:20

嗨,我正在使用vivado 2013.4并且在实现后从触发器的Q引脚到180个负载(RAMB36E1上的ENBWREN引脚)获得高扇出网络。它符合时间,但是,我希望网络能够得到缓冲。1.有没有

2018-10-18 14:28:10

`altium designer PCB工具进行BGA Fanout时,为了确保能够正常扇出,需要进行如下设置:1.规则设置快捷键D+R,设置如下几项:1)clearence间距设置2)width

2015-10-29 12:34:17

接口视频教程时序图赞阅读解析练习讲解命令书籍资料:《勇敢的芯伴你玩转Altera FPGA》电子版 下载 (FPGA初学者首选)书籍:FPGA开发全攻略电子版(超清,上下册全)玩转FPGA,这些资料不要

2019-05-17 18:19:21

案例进行实战演练,让学员理论与实际结合,彻底掌握BGA扇出的方法。直播大纲1、BGA的概念解析以及设置2、布线规则添加与规则管理器介绍3、区域规则介绍与添加4、各类BGA芯片扇孔与出线实战演示5、你

2021-03-30 22:03:56

我在fanout 时遇到一个问题,有一些有网络的引脚它没有给我扇出,是怎么回事,能帮我解答一下吗,谢谢

2019-09-06 05:35:11

为啥自动扇出了还报错啦,求解

2019-09-09 03:12:20

求助0.5mm焊盘,间距0.8mm的BGA封装怎么设置自动扇出45度;我规则设置线宽4mil,间距也是4mil,可是自动扇出45度的方向失败,而且有些焊盘扇出不了,如下面第一张图;;;手动扇出是没有问题的,下面第二张图@Kivy @Pcbbar 谢谢!!

2019-09-19 01:08:11

我在时序改进向导中读到,手动复制源可以减少扇出。任何人都可以解释复制源的含义吗?还有一个选项来设置最大扇出,我在合成属性对话框中默认为100000,而我在某处读到默认最大扇出为100.我不明白

2018-10-10 11:50:47

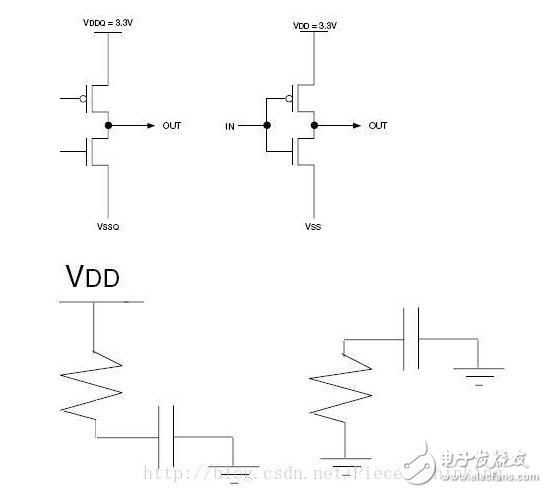

今天我们要介绍的概念是fanin,扇入。是指单个逻辑门的输入的数量;如下图为一个fanin为3 的与门;需要注意的是,在STA中,我们不允许出现多个输出单元同时驱动一个输入pin的情况,...

2021-07-29 06:34:09

`勇敢的芯伴你玩转Altera FPGA连载13:实验平台复位电路解析特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD FPGA的时钟

2017-10-23 20:37:22

BGA扇出 点击工具栏的创造fanout: 注意走线的设置应如下图所示,将bubble模式关掉。 在点击fanout命令后,按照下图所示设定fanout的设置:选择合适的过孔

2021-12-31 06:54:47

在HDL中改变电气连接(改变IC器件pin的net),在原有fanout过板子基础上,再次倒板子。某些IC器件的fanout消失了,某些器件的IC器件的fanout没有消失,但是fanout出来的孔

2015-11-09 15:23:42

基于DSP与PC机的PCI总线高速数据传输资料解析,不看肯定后悔

2021-06-03 06:47:49

你好什么是FPGA IO引脚的扇出....我正在使用LVTTL 3.3信号电平...我想将FPGA连接到比较器的锁存信号....我有32个比较器需要从FPGA给出锁存信号....问候,维诺德

2020-06-02 14:22:53

只是将TDI信号扇出到所有FPGA,而不是一次扇出1。是否有示例图表显示如何完成此操作?我该如何处理TDO?我可以期望所有这些设备同时进行编程会出现什么样的功率峰值?谢谢,唐

2020-05-14 07:01:03

中,一个时钟源要驱动多个器件,因此可使用时钟缓冲器(通常称为扇出缓冲器)来复制信号源,提供更高的激励电平。图 1. 使用扇出缓冲器创建大量单输入频率副本LMK00304 扇出缓冲器就是一个很好的例子

2022-11-21 07:25:28

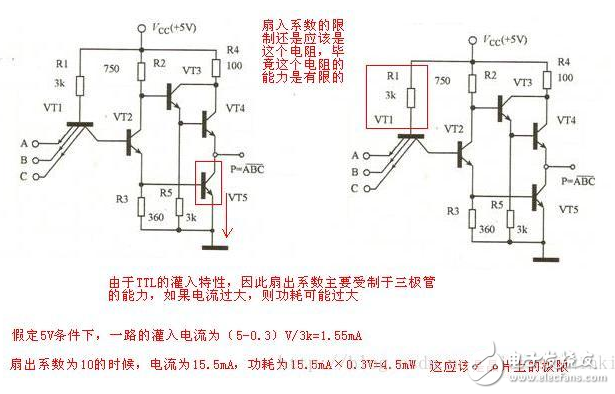

在上拉和下拉电阻中是不是有对应的拉电流和灌电流?拉电流和灌电流是什么意思?扇出系数是指什么?

2021-04-07 06:46:24

嗨,所有,在正常的I/O引脚,我们考虑扇出计算时,我们有更多的设备连接到单一逻辑输出。在I2C除了总线电容的情况下,我们是否需要考虑扇出?我发现高输出电流和低输出电流,低电平输入电流这些参数需要考虑吗?谢谢

2019-10-09 13:12:37

求大神分享一下PADS中BGA Fanout扇出教程

2021-04-25 07:37:39

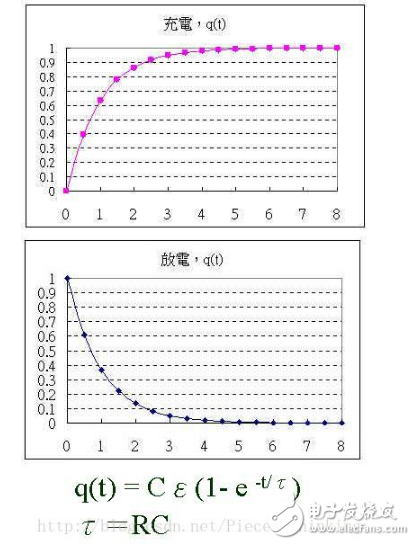

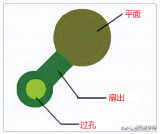

在我们常规设计中对滤波电容fanout时,要从pin拉出一小段粗引出线,然后通过过孔和电源平面连接,接地端也是同样。fanout过孔的基本原则就是让这一环路面积最小,进而使总的寄生电感最小。滤波电容的常见fanout方式如下图所示,滤波电容靠近电源pin放置。

2019-07-31 08:36:05

用FPGA做的MCU内核的汇编指令集完全解析,FPGA使用VHDL编写MCU内核,使用PHP编写汇编器,使用vc studio编写FLASH下载器,全套资料在 www.creuu.com 免费下载

2020-03-04 18:53:52

遇到过很多次了,各种不同的FPGA均遇到过这种问题。改动一个完全跟逻辑没有关系的地方就不能正常工作,但将某些信号扇出到输出管脚上之后又能正常工作了。请问这种现象是什么原因产生的?有没有什么比较好的解决方法?

2014-08-01 16:11:56

AD9513可否用于数字信号的fanout driver(带有编码、不需要分频)?

2018-08-20 07:20:03

请问一下fanin是什么意思?

2021-10-29 07:14:15

请问下谁知道DDR扇出为什么只扇出电源和地的部分,其他都没有扇出来?

2016-11-28 13:04:19

转载一篇讲述高扇出的解决办法的博文。链接:http://blog.163.com/fabulous_wyg/blog/static/174050785201322643839347/

2014-04-29 21:41:20

FPGA设计中,经常会出现由于设计不合理产生的布线问题,较为突出的一点就是门控时钟和多扇出问题。门控时钟指的是不用FPGA内部的全局时钟资源BUFG来控制触发器的时钟沿输入端而是采用组合逻辑和其它

2012-01-12 10:40:20

在我的设计中,我有几个高负荷信号,现在我认为我的定义和Xiinx对高扇出的定义是完全不同的。如果我看到一个控制信号,当使用12.5ns周期时扇出为300,净延迟为7.5ns。我开始担心了。当时间报告

2018-11-01 16:13:02

布线前期准备和扇出... 795.1 前期准备................. 795.1.1 布局优化............ 795.1.2 自动布线密度评估............... 795.1.3 关键信号手工布线.............. 815.2 扇出(FANOUT) ...

2008-08-05 14:36:19 0

0

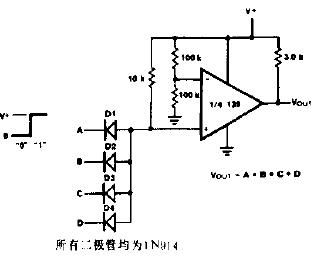

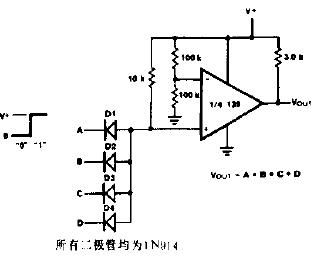

高扇入与门电路图

2009-04-02 09:20:04 518

518

扇出系数,扇出系数是什么意思

扇出系数No:扇出系数No是指与非门输出端连接同类门的最多个数。它反映了与非门的带负载能力 。

2010-03-08 11:06:20 8029

8029 扇入系数系数,扇入系数是什么意思

扇入系数NI: 门电路允许的输入端的数目,称为该门电路的扇入系数。一般NI≤5,最多不超过8。实

2010-03-08 11:07:40 2052

2052 一、建立原点座标:(用PADS 2005 打开没有layout BGA文件)1.鼠标右键,点选"Select Traces/Pins",再点BGA的左上角的一

2010-06-24 17:49:42 7505

7505 DDR3内存已经被广泛地使用,专业的PCB设计工程师会不可避免地会使用它来设计电路板。本文为您提出了一些关于DDR3信号正确扇出和走线的建议,这些建议同样也适用于高密度、紧凑型的电路板设计。

2018-06-16 07:17:00 8959

8959

本文档的主要内容详细介绍的是FPGA基础及7系列FPGA基本原理的基础资料说明

2019-04-28 08:00:00 15

15 找到目标后,可以利用max_fanout来限定其扇出值,让工具在实现过程中复制驱动端寄存器来优化。如果高扇出网络并不是由同步逻辑来驱动,则可能需要修改代码。

2019-07-25 11:45:52 2402

2402

在设计集成电路时,扇出是指门输入的数量a逻辑门输出可以连接到。虽然狗骨扇出是一种经得起考验的方法,但值得考虑针对特定应用的垫内扇出方法的优点,以及检查在制定扇出策略时应采取的各种考虑因素。

2019-07-25 09:58:04 3831

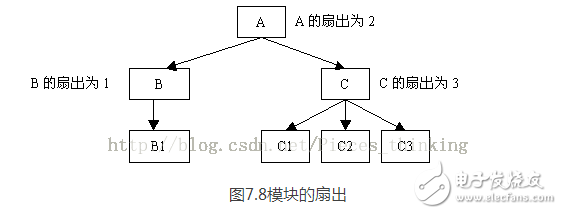

3831 Fanout,即扇出,指模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛。因此,在写代码时应尽量避免高扇出的情况。但是,在某些特殊情况下,受到整体结构设计的需要或者无法修改代码的限制,则需要通过其它优化手段解决高扇出带来的问题。

2019-10-13 14:55:00 3506

3506

在allegro软件中应该如何对BGA器件进行自动扇出呢? 答:在进行PCB布线之前,都需要先做扇出工作,方便内层布线。对于电阻电容后者是小的IC类器件,可以直接进行手动扇出,但是对BGA类的器件

2020-10-14 10:28:43 6992

6992

在先进封装技术中,晶圆级封装能够提供最小、最薄的形状因子以及合理的可靠性,越来越受市场欢迎。晶圆级扇出和WLCSP/扇入仍然是两个强大的晶圆级封装家族。不同于晶圆级扇出,WLCSP工艺流程简单,封装

2021-01-08 11:27:46 8883

8883

ARM与FPGA的接口实现的解析(应广单片机)-该文档为ARM与FPGA的接口实现的解析详述资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-22 09:47:55 14

14 EDID详细解析资料汇总

2021-09-23 15:30:17 22

22 1.扇出太多引起的时序问题。 信号驱动非常大,扇出很大,需要增加驱动能力,如果单纯考虑驱动能力可以尝试增加buffer来解决驱动能力,但在插入buffer的同时增加了route的延时,容易出现

2021-10-25 16:30:06 7702

7702 今天我们要介绍的概念是fanin,扇入。是指单个逻辑门的输入的数量;如下图为一个fanin为3 的与门;需要注意的是,在STA中,我们不允许出现多个输出单元同时驱动一个输入pin的情况,也就

2021-11-26 10:27:35 4824

4824

今天要介绍的时序分析概念是fanout。中文名是扇出。指的是指定pin或者port的输出端口数。 合理的选择fanout的数目对设计来说是非常重要的,fanout过大与过小都会对设计带来不利因素

2021-11-26 10:31:41 11753

11753

BGA扇出 点击工具栏的创造fanout: 注意走线的设置应如下图所示,将bubble模式关掉。 在点击fanout命令后,按照下图所示设定fanout的设置:选择合适的过孔

2022-01-11 12:08:40 4

4 测量扇出缓冲器中的附加抖动

2022-11-04 09:52:08 0

0 1 到 4 扇出缓冲器-74AVC1T1004

2023-02-16 21:16:26 0

0 1 到 4 扇出缓冲器-74AVC9112

2023-02-21 19:33:20 0

0 1 到 4 扇出缓冲器-74AVC1T1022

2023-03-03 19:53:47 0

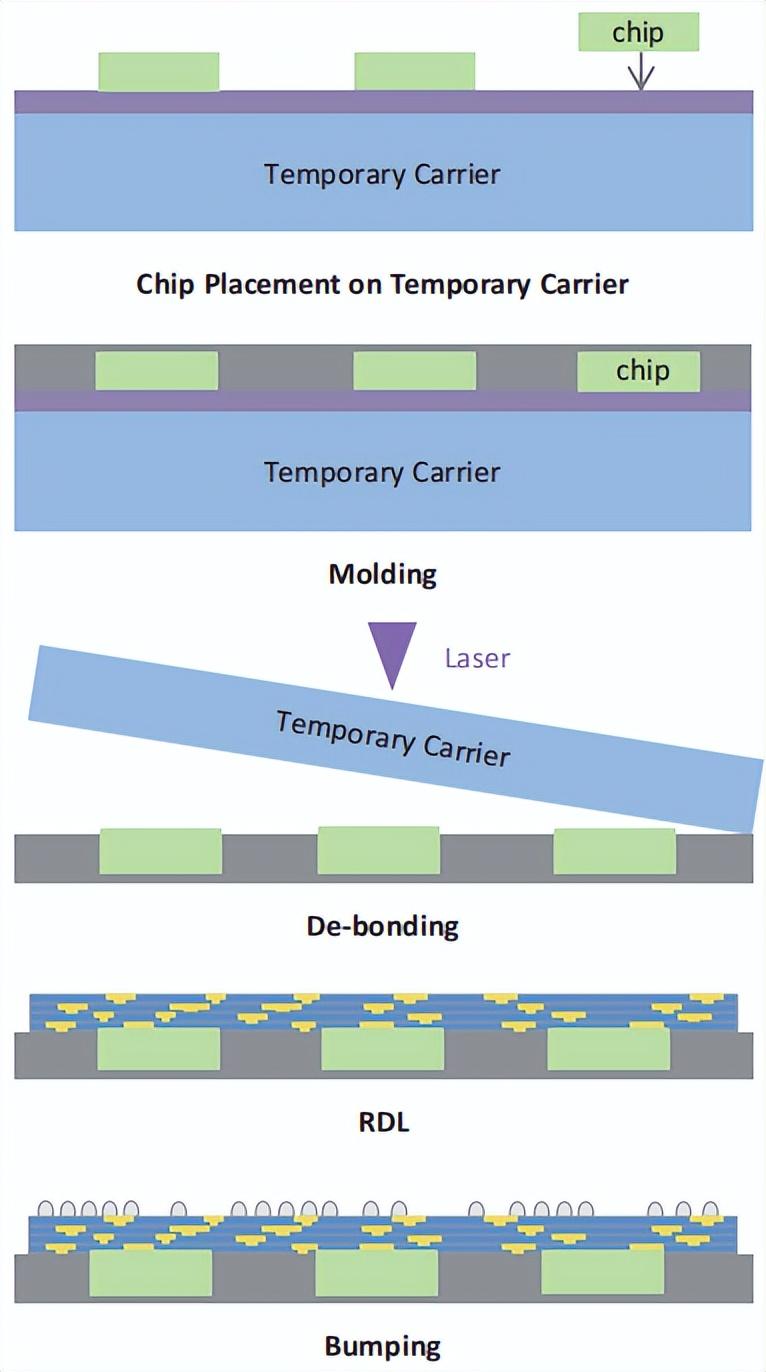

0 来源;《半导体芯科技》杂志 作者:黄泰源、罗长诚、钟兴进,广东鸿浩半导体设备有限公司 摘要 扇出晶圆级封装广泛应用于手机、车载等电子产品上。制造过程中需要使用到暂时性基板,而移除暂时性基板最适

2023-04-28 17:44:43 972

972

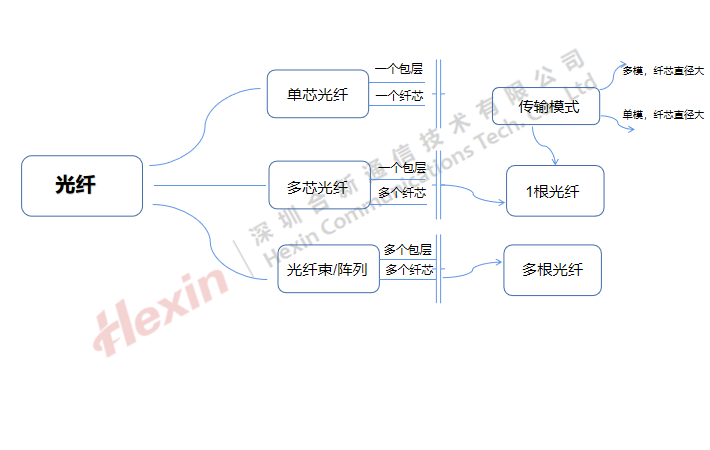

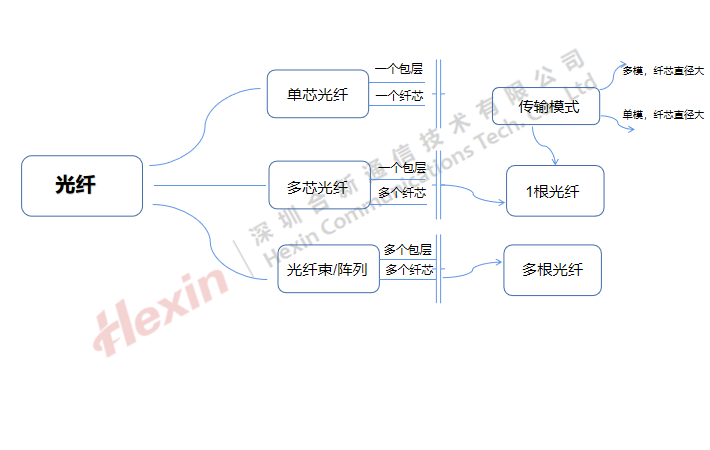

。而多光纤束可以做成各种形状,省空间,传输容量又够大。但多芯光纤有两个困难是影响到实际运用的:一.串扰,二.扇入扇出扇入扇出,就咱们单芯光纤与多芯光纤怎么对接,一般

2021-12-27 14:09:15 1408

1408

在 PCB 布局设计中,特别是BGA(球栅阵列),PCB扇出、焊盘和过孔尤为重要。扇出是从器件焊盘到相邻过孔的走线。

2023-07-18 12:38:12 1769

1769

、中文资料、英文资料,HMC940: 13 Gbps, 1:4 Fanout Buffer w/ Programmable Output Voltage Data Sheet真值表,HMC940: 13

2023-10-13 18:33:07

扇出型晶圆级封装技术的优势在于能够利用高密度布线制造工艺,形成功率损耗更低、功能性更强的芯片封装结构,让系统级封装(System in a Package, SiP)和3D芯片封装更愿意采用扇出型晶圆级封装工艺。

2023-10-25 15:16:14 314

314

电子发烧友App

电子发烧友App

评论