先给大家简单快速地介绍一下 Vivado 集成设计环境,即 IDE。当打开 Vivado 工程后,会有一个工程概要,向您介绍工程的设置、警告和错误信息以及工程的一般状态。

2012-04-25 09:00:43 6408

6408 作者:Mculover666 1.实验目的 通过例程探索Vivado HLS设计流 用图形用户界面和TCL脚本两种方式创建Vivado HLS项目 用各种HLS指令综合接口 优化Vivado HLS

2020-12-21 16:27:21 3153

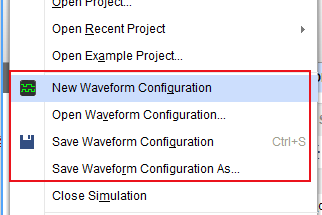

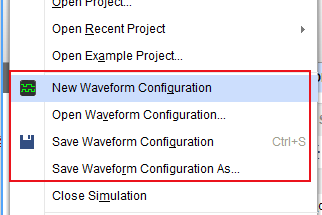

3153 配置显示为untitled。打开仿真后,File菜单中有与波形配置相关的指令: 这些控制功能依次是: New Waveform Configuration:创建一个新的波形配置,Vivado

2021-01-03 09:22:00 7311

7311

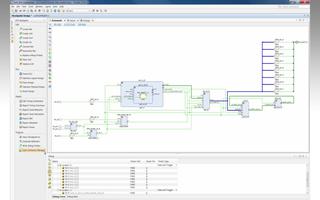

仿真功能概述 仿真FPGA开发中常用的功能,通过给设计注入激励和观察输出结果,验证设计的功能性。Vivado设计套件支持如下仿真工具:Vivado Simulator、Questa、ModelSim

2020-12-31 11:44:00 4723

4723

在Vitis完成这个过程的底层,实际调用的是Vivado。Vitis会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要在Vivado中分

2022-08-02 08:03:38 1016

1016

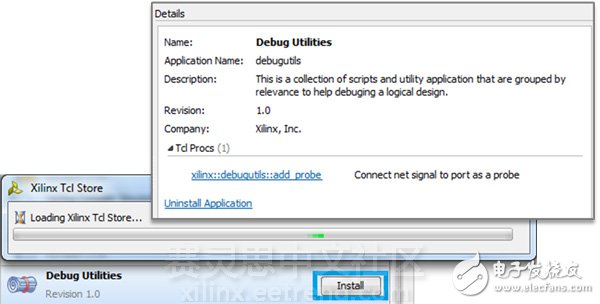

Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。

2022-09-14 09:09:56 1526

1526 双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 403

403

/ 134第5章 IP的管理 / 1355.1 定制IP / 1355.1.1 在Vivado工程中定制IP / 1355.1.2 在Manage IP中定制IP / 1395.2 IP的两种生成文件形式

2020-10-21 18:24:48

我在两台64位Windows机器上安装了2013.1,并且两者都崩溃了。 Vivado 2013.1窗口在崩溃之前会短暂出现。如果我从命令行运行,我会看到:****** Vivado v2013.1

2018-11-27 14:30:08

License(由VLM加载.xml文件),并在VLM中显示。我在论坛中尝试了很多解决方案: - 我重新安装了Vivado三次, - 我用禁用防病毒软件(Avast)运行模拟,我检查了它的“病毒库

2018-12-12 10:52:39

功能'Synthesis'和/或设备'xc7a35t'的有效许可证。请运行Vivado许可证管理器以获取有关确定系统许可的功能和设备的帮助。解决方案:在Vivado License Manager中检查

2018-12-26 11:30:48

你好,我们今天刚刚收到一个ZC706开发套件(带有Zynq XC7Z045),我们非常惊讶,因为在欢迎信中写道:“随着Vivado 2015.4的发布,该产品已被冻结。它将不会在后来的Vivado软件中运行”这应该是什么意思?我们正在使用最新的Vivado版本2016.1!谢谢,Cerilet

2019-10-10 08:24:14

你好,在Vivado 2016.4中运行Synthesis功能时,我收到了有效的许可证错误[Common 17-345]。请参阅附件和帮助。谢谢,Gursimar合成日志file.txt 2 KB

2019-01-04 11:22:27

嗨伙计,我在Vivado面临一个问题。我已经生成了三模式以太网MAC(TEMAC)的示例设计,作为Artix7 FPGA板的给定指令。在此之后,我测试了Tx和Rx用于TEMAC。我可以成功传输数据

2020-07-23 08:23:46

嗨,在我的Vivado实现tcl脚本中,以下行导致错误:设置SRC_PATH ./input.............#Input the netlistread_edif $ SRC_PATH

2018-10-18 14:26:39

Vivado实现线程卡在“编写放置器数据库”上。该路由成功完成并且Vivado许可证被释放,然后它将编写占位符数据库并且永远不会完成,只是在那里永久旋转。在Windows任务管理器中杀死线程后

2018-10-30 11:15:39

特性比较对 Vivado 和它的前一代设计套件,ISE 做一个组件功能上的平行比较和总结是很有用的。其目的是让那些具有在 ISE 下工作经验 (但是不具有 Vivado 下经验)的人能够更快的适应

2021-01-08 17:07:20

TakeVideos:快速使用的视频连接口,关联到DocNav,并筛选出Vivado使用的一些教学视频;Release NotesGuide:在DocNav中打开Vivado release Notes

2019-07-18 15:40:33

TakeVideos:快速使用的视频连接口,关联到DocNav,并筛选出Vivado使用的一些教学视频;Release NotesGuide:在DocNav中打开Vivado release Notes

2023-09-06 17:55:44

大家好,我想知道Vivado生成的HDL代码是否在Vivado自带的许可证之上有任何特殊的许可。考虑为AXI奴隶生成的代码,有什么阻止我在设置中使用它大学课程的论文?如果代码刚刚生成并从设计诉讼中

2018-12-20 11:23:27

嗨,我在Vivado 16.2中重新创建了一个在Vivado 15.2中完美运行的固件。当我尝试在IPI中验证设计时,它会给出错误和严重警告。这个版本的Vivado的参数propragation有

2020-08-06 07:55:13

:[Common 17-345]找不到功能'Synthesis'和/或设备'xc7a35t'的有效许可证。请运行Vivado许可证管理器以获取有关确定哪些功能和设备已获得系统许可的帮助。解决方案:在

2018-12-14 11:32:37

你好,我在Win10中使用vivado 2016.2 for zynq7020。我的时钟方案是zynq PS FCLK_CLK0-->时钟向导IP输入(Primitive PLL)的输入。合成

2018-11-05 11:40:53

请问各位大神,vivado中点击综合或者实现时,出现的number of jobs 代表什么意思?

2018-03-09 22:18:19

想到要写这一系列关于工具和方法学的小文章是在半年多前,那时候Vivado®已经推出两年,陆续也接触了不少客户和他们的设计。我所在的部门叫做“Tools & Methodology

2023-09-20 06:31:14

嗨,在Vivado 2015.4和ISE 14.7中实现的相同设计之间的资源利用率是否会有任何差异?考虑到这样的事实,IP在Artix-7 FPGA中重新生成FIFO(版本9.3到13.1)时钟向导

2019-04-24 09:12:08

大家好,感谢您的关注。 (这是我在论坛上的第一个主题〜)我已经了解到Quartus II具有Logic Lock功能,这对于组中的设计人员来说非常方便,并且还具有时序优化功能。我对vivado并不

2020-05-20 14:32:56

大家好,我正在尝试在Ubuntu 13.10上安装Vivado 2013.2我按照描述的步骤进行操作(sudo apt-get install openjdk-7-jre,sudo mv /opt

2018-12-10 10:29:37

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

你好:我没有通过ZC702评估套件和Vivado 2013.2中的PMOD1上的SPI外设通过EMIO获得预期的行为。我已阅读AR#47511我必须在MHS文件中更改或添加一些代码行,但我在项目目录中找不到MHS文件。 Vivado不使用MHS文件吗?我怎么解决这个问题?

2019-11-08 12:12:06

嗨,我正在寻找有关如何使用Xilinx Vivado创建Hard宏的示例。了解如何在设计中修复路由并在阅读pdf(下面)时,提到可以根据要求提供示例,这将非常有帮助。我是否可以收到一些此实施的示例

2018-11-12 14:42:01

在我们的设计中,Vivado实现结果因运行而异。我们想要从“最佳”实现中锁定两个模块的放置信息。然后将其保存以备将来运行。我们知道这可能与pblock和分层设计有关。但是,分层设计文档并不十分

2018-10-18 14:36:14

嗨,我有一个关于Vivado 2017.4实验版的问题。在发行说明中,它被描述为“注意:Lab Edition安装程序可以在32位或64位计算机上运行。”我在32位机器上下载了2017.4实验室

2019-01-07 10:31:57

嗨,当我在Linux系统上安装Vivado 2017.2时,由于与Vivado安装无关的原因,系统在安装过程中崩溃了。这给我留下了一个带有“半安装”vivado的系统,一些文件到位,但很多都丢失了

2018-12-25 11:10:25

你好ISE的合成与实现,最终资源利用分析报告正常。现在在Vivado中,在实现逻辑优化(opt_design)的第一步(实现)中投入了大量资源来优化模块(建议逻辑单元不加载),但是当ISE实现没有被

2018-10-24 15:23:00

你好,我从Digilent购买了一块ZYBO板,并兑换了Vivado Design Suite附带的优惠券。今天我试图实例化一个VIO核心,我的许可证出错了。如何访问Vivado Analyzer

2018-12-14 11:35:26

大家好,我已经安装了Vivado 2016.3。在安装过程中,我检查了Spartan 7包。但是当我启动Vivado时,目录中没有Spartan 7设备。 Vivado目前是否普遍支持Spartan 7?或者我是否通过安装工具犯了一些错误?最好的祝福,埃米尔

2020-08-11 07:25:38

您好,我正在为Vivado 2015.3课程做一个项目。该项目是边界扫描测试。我编写了所有VHDL代码并尝试实现。但是,实施还没有发生。我一直得到错误:[Synth 8-4169]使用条款中的错误

2019-04-15 12:38:48

你好,有没有办法在Vivado 2016.1中关闭特定的DRC违规或警告?其次是AR#63997的方向,我试过:set_property严重性警告[get_drc_checks RTSTAT-2

2018-10-26 15:03:13

我的目标是实现一个给定的C算法是一个FPGA。所以,我最近得到了一个Zedboard,目标是实现该算法是PL部分(理想情况下PS中的顶级内容)。我在FPGA领域和编写VHDL / Verilog方面

2020-03-24 08:37:03

你好我正在尝试在vivado HLS中创建一个IP,然后在vivado中使用它每次我运行Export RTL我收到了这个警告警告:[Common 17-204]您的XILINX环境变量未定义。您将

2020-04-03 08:48:23

让我知道vivado在zed fpga中创建coe文件,是否可以在project / srcs目录中找到它

2020-04-15 10:04:17

Vivado不断在vivado项目目录中创建new.jou和.log备份文件。如何禁用这些文件的创建和/或备份?以上来自于谷歌翻译以下为原文Vivado is constantly creating

2018-12-21 11:07:52

单击“开始”菜单中的“Vivado 2016.1”按钮后:然后我点击修复,然后:但事情并没有好转,因为Vivado没有按照应有的方式发布,相反,几秒钟之后,这就出现了:经过多次尝试但只得到了相同

2018-12-21 11:02:24

文件中匹配目标的时候,在可行的情况下更倾向于使用正则表达式。本文就介绍一下我常使用的正则表达式和一些在Vivado中应用的特殊之处,同时也有个别自己尚未解决的问题。

2021-01-26 07:03:16

今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

上一篇《Tcl 在 Vivado 中的应用》介绍了 Tcl 的基本语法以及如何利 用 Tcl

2023-06-28 19:34:58

《Vivado使用误区与进阶》电子书汇集了赛灵思专家团队在客户支持时所碰见的诸多实际案例,以及相对应的解决方案;还有多年总结下来的设计技巧与代码参数详解。是您学习和掌握Vivado开发套件的一本不可多得的实战指导资料。

2016-08-03 19:37:24 84

84 可能会让您无所适从,您真的了解和掌握了这款工具?还有全新的系统设计方法学?您真的体会到了Vivado设计套件的强大与高效吗? 《Vivado设计误区与进阶》汇集了赛灵思专家团队在多年的客户支持工作中所积累的经验和方案,每个小文章都力图选取

2017-02-09 04:32:12 197

197 在linux系统上实现vivado调用VCS仿真教程 作用:vivado调用VCS仿真可以加快工程的仿真和调试,提高效率。 前期准备:确认安装vivado软件和VCS软件 VCS软件最好安装

2018-07-05 03:30:00 10733

10733

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado2016.4的性能测试

2018-07-04 11:23:00 9674

9674

无论此刻你是一个需要安装Xilinx Vivado工具链的入门菜鸟,还是已有license过期的Vivado老铁,今儿咱就借着这篇文章,把学习「Vivado如何获取License」这档子事儿给说通透咯~ 手把手教程,分三部分讲述。

2018-07-03 09:54:00 58889

58889

vivado设计套件资料

2017-10-31 09:49:03 43

43 其实Tcl在Vivado中还有很多延展应用,接下来我们就来讨论如何利用Tcl语言的灵活性和可扩展性,在Vivado中实现定制化的FPGA设计流程。 基本的FPGA设计实现流程 FPGA的设计流程简单来讲,就是从源代码到比特流文件的实现过程。大体上跟IC设计流程类似,可以分为前端设计和后端设计。

2017-11-18 01:48:01 3295

3295

Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握

2017-11-18 03:52:01 4675

4675

1 Vivado HLS简介 2创建一个Vivado-HLS工程 2.1打开Vivado HLS GUI 2.2创建新工程 在 Welcome Page, 选择Create New Project

2017-12-04 10:07:17 0

0 在实际工程中,如何利用好这一工具仍值得考究。本文将介绍使用Vivado HLS时的几个误区。

2018-01-10 14:33:02 19813

19813

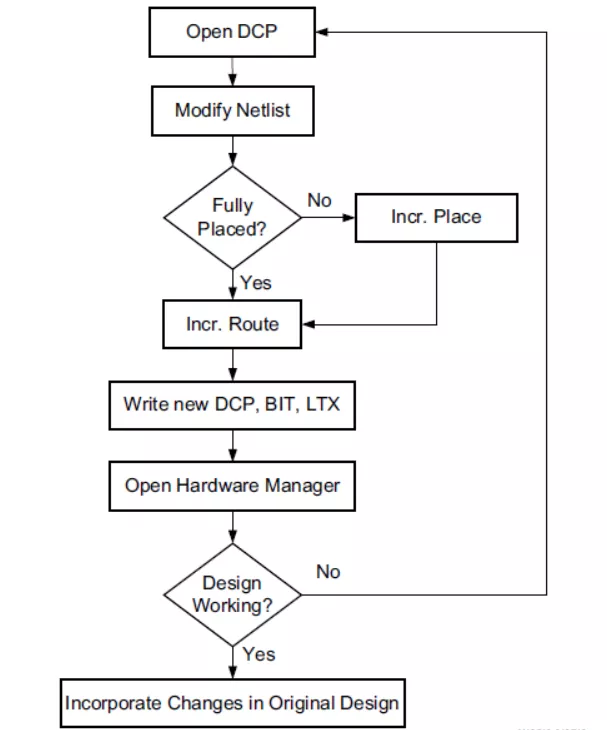

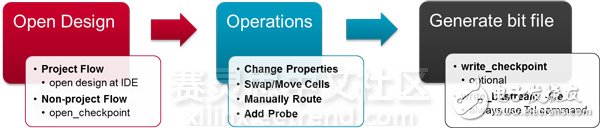

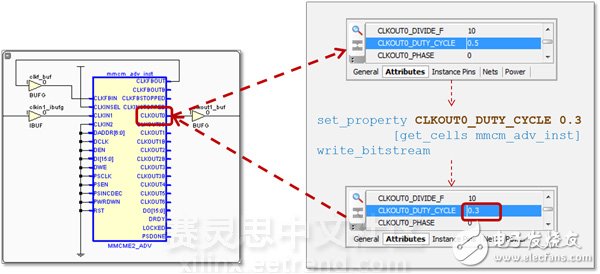

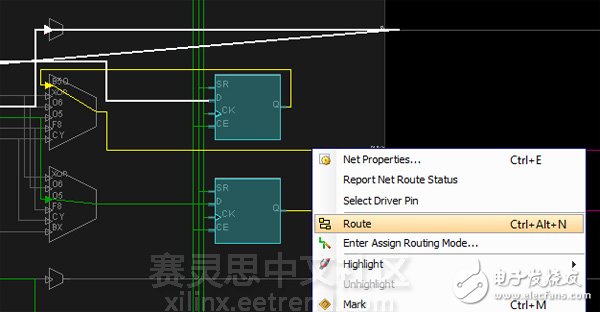

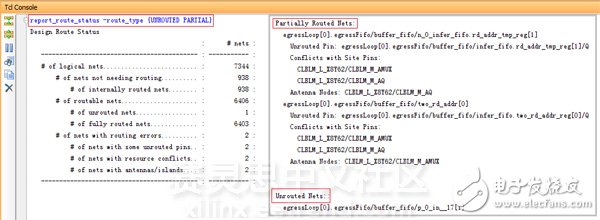

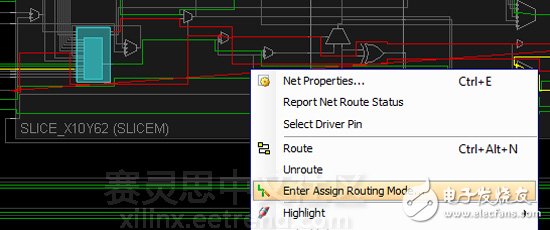

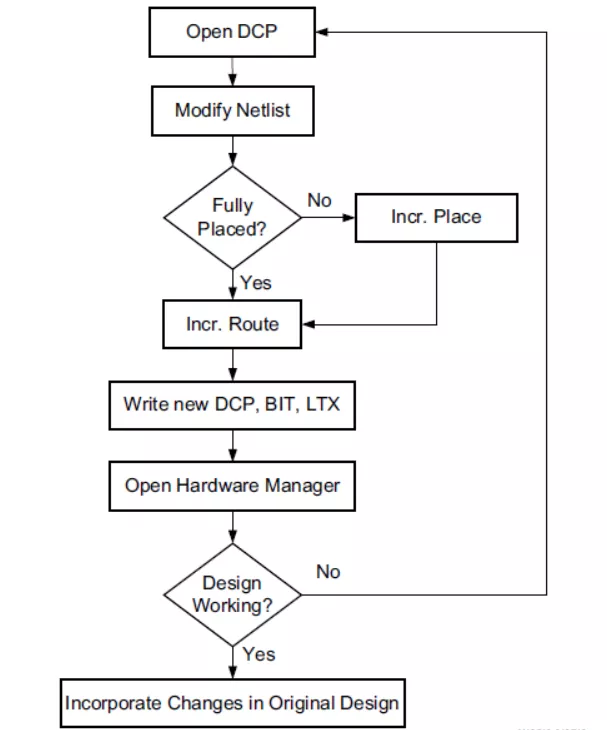

了解如何在Vivado中执行工程变更单(ECO)。

本视频将向您介绍ECO的常见用例,我们推荐的完成ECO的流程,优势和局限性,并将演示功能设计的ECO。

2018-11-21 06:40:00 4647

4647

本视频重点向您介绍了Vivado设计套件2017.3版本中的增强功能,包括操作系统和器件支持,高级增强功能,加速集成,实施和验证的各种升级和改进。欢迎收看本视频,了解更多有关

Vivado设计套件的新功能。

2018-11-21 06:15:00 3374

3374

了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-20 06:55:00 2340

2340 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-20 06:56:00 2512

2512 该视频介绍了2017.1 Vivado设计套件中的新外观。

它讨论了变更的动机,介绍了一些亮点,并演示了一些功能。

2018-11-20 06:27:00 2355

2355 了解Vivado Design Suite 2016中的新功能。

我们将回顾新的UltraFast方法检查,HDL模块参考流程和用于IPI设计的SmartConnect IP,语言模板增强,Xilinx参数化宏(XPM),GUI改进

2018-11-20 06:22:00 2247

2247 2015年Club Vivado开发者大会的预览。

2018-11-20 11:51:25 992

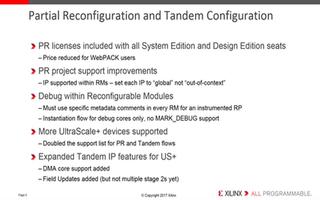

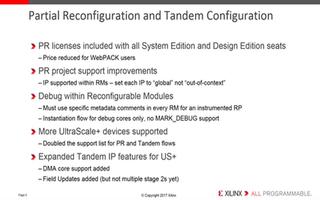

992 此视频重点介绍了新的Vivado Design Suite 2017.1版本的增强功能,包括操作系统和设备支持,新外观,部分重新配置广泛可用性等等......

2018-11-30 06:20:00 2537

2537

了解如何使用Vivado的创建和封装IP功能创建可添加自定义逻辑的AXI外设,以创建自定义IP。

2018-11-29 06:48:00 6801

6801

了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-29 06:32:00 3340

3340 了解使用Vivado 2016.1中引入的ECO流程进行调试的好处,以及在ECO布局中替换ILA调试探针所需的步骤。

2018-11-29 06:01:00 3316

3316

了解Vivado设计套件中的一些广泛的设计分析功能,旨在识别可能影响性能的设计中的问题区域。

2018-11-27 07:10:00 4613

4613 了解新Vivado Lab Edition的功能和优点,并熟悉其安装和典型使用流程。

2018-11-30 06:40:00 17064

17064 了解如何使用Vivado设计套件的电路板感知功能快速配置和实施针对Xilinx评估板的设计。

2018-11-26 06:03:00 3062

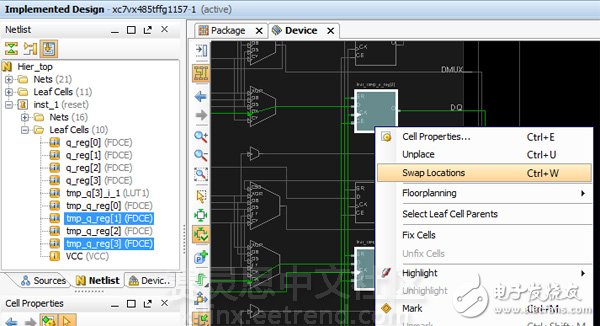

3062 物理优化是Vivado实现流程中更快时序收敛的重要组成部分。

了解如何在Vivado中应用此功能以交换运行时以获得更好的设计性能。

2018-11-23 06:06:00 3728

3728 了解如何使用2014.1中引入的新激活许可为Vivado工具生成许可证。

另外,了解Vivado 2014.1中的许可更改如何影响您,以及如何在激活客户端中使用新的Vivado License Manager

2018-11-22 07:10:00 2614

2614 了解如何使用Vivado在设备启动时及其周围进行调试。

你也会学习

使用Vivado 2014.1中引入的Trigger at Startup功能来配置和预先安装a

调试核心并触发设备启动时或周围的事件......

2018-11-22 07:05:00 4084

4084 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-30 19:24:00 4251

4251 在Vivado Design Suite中,Vivado综合能够合成多种类型的属性。在大多数情况下,这些属性具有相同的语法和相同的行为。

2019-05-02 10:13:00 3750

3750 中国大学MOOC

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-08-06 06:12:00 3450

3450

关于Vivado Dashboard的功能可阅读这篇文章(Vivado 2018.3这个Gadget你用了吗)Vivado 2019.1的Dashboard功能进一步增强。

2019-06-12 14:49:24 7677

7677

核的使用。 BRAM是FPGA定制的RAM资源,有着较大的存储空间,且在日常的工程中使用较为频繁。BRAM以阵列的方式排布于FPGA的内部,是FPGA实现各种存储功能的主要部分,是真正的双读/写端口的同步的RAM

2020-12-29 15:59:39 9496

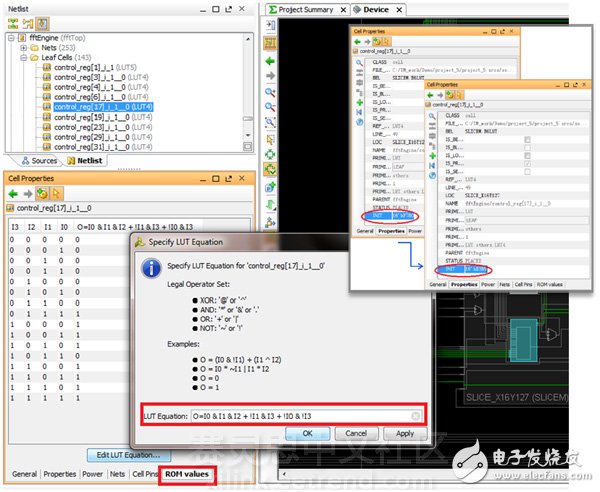

9496 带大家一起体验一下Vivado 的ECO流程,以vivado自带的Example Design为例, 直接用TCL命令修改网表,在正常的寄存器路径之间加一级LUT。 1. 打开Vivado 界面 2. 打开

2020-10-26 09:45:23 3366

3366

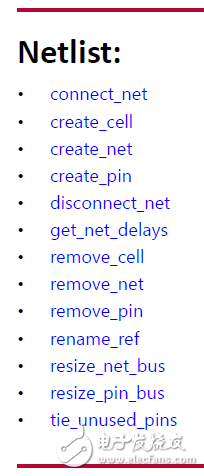

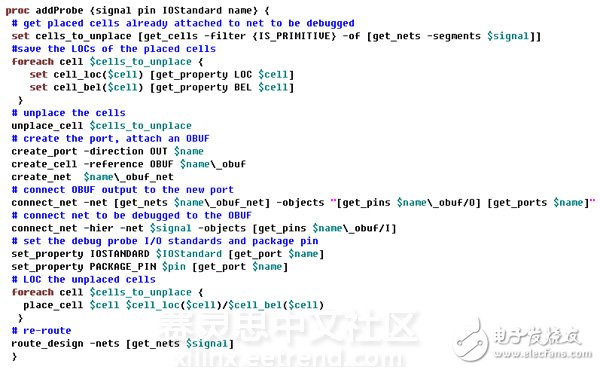

这里带大家一起体验一下Vivado 的ECO流程,以vivado自带的Example Design为例, 直接用TCL命令修改网表,在正常的寄存器路径之间加一级LUT。

2020-11-29 11:04:53 3879

3879

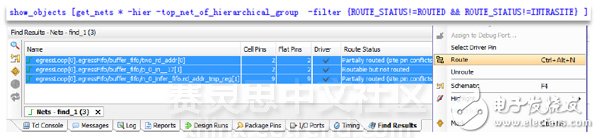

我们都知道FPGA的实现过程分为2步:分析综合与布局布线后就可以产生目标文件,这两个步骤中间有个非常重要的文件,那就是-网表。 下图是Vivado中网表列表示例: Vivado

2021-05-14 10:46:53 3783

3783

本篇文章来自赛灵思高级工具产品应用工程师 Hong Han. 本篇博文将继续介绍在Vitis中把Settings信息传递到底层的Vivado. 对于Vivado实现阶段策略的指定

2021-08-13 14:35:56 3900

3900 Vivado License Manager在使用Vivado License Manager时,如果通过如下图所示方式指定license的路径时,要保证路径仅包含ASCII字符而没有中文字

2021-09-12 15:15:19 5055

5055 【流水灯样例】基于 FPGA Vivado 的数字钟设计前言模拟前言Vivado 设计流程指导手册——2013.4密码:5txi模拟

2021-12-04 13:21:08 26

26 在《vivado使用误区与进阶》中,提到了一种叫 UltraFAST 的设计方法。

2022-03-30 11:53:26 3017

3017 Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado 2020.2为例,讨论如何升级Vivado工程脚本。

2022-08-02 10:10:17 1542

1542 ECO 指的是 Engineering Change Order ,即工程变更指令。目的是为了在设计的后期,快速灵活地做小范围修改,从而尽可能的保持已经验证的功能和时序。ECO 是从 IC 设计领域继承而来,Vivado上 的 ECO 便相当于 ISE 上的 FPGA Editor。

2022-08-02 09:18:04 2945

2945

Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。

2022-09-19 16:20:51 1309

1309 Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为

2023-04-15 09:43:09 958

958 对 FPGA 设计的实现过程必须以满足 XDC 中的约束为目标进行。那我们如何验证实现后的设计有没有满足时序要求?又如何在开始布局布线前判断某些约束有没有成功设置?或是验证约束的优先级?这些都要用到 Vivado 中的静态时序分析工具。

2023-05-04 11:20:31 2368

2368

今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

2023-05-05 09:44:46 674

674

关于 Tcl 在 Vivado中的应用文章从 Tcl 的基本语法和在 Vivado 中的 应用展开,继上篇《用 Tcl 定制 Vivado 设计实现流程》介绍了如何扩展甚 至是定制 FPGA

2023-05-05 15:34:52 1612

1612

vivado开发软件自带了仿真工具,下面将介绍vivado的仿真流程,方便初学者进行仿真实验。

2023-07-18 09:06:59 2137

2137

电子发烧友网站提供《Vivado Design Suite教程:动态功能交换.pdf》资料免费下载

2023-09-14 15:13:43 0

0 电子发烧友网站提供《Vivado设计套件用户:使用Vivado IDE的指南.pdf》资料免费下载

2023-09-13 15:25:36 3

3 定制的RAM资源,有着较大的存储空间,且在日常的工程中使用较为频繁。BRAM以阵列的方式排布于FPGA的内部,是FPGA实现各种存储功能的主要部分,是真正的双读/写端口的同步的RAM。 本片

2023-12-05 15:05:02 317

317

正在加载...

电子发烧友App

电子发烧友App

评论