随着无线数据传输量呈爆炸性成长,数字讯号处理技术和无线电设备在提升效能方面都面临巨大的压力。目前全球的重点都聚焦在4G LTE,而且在世界各地均有大规模部署,而业界也已展开5G网络的早期研发工作,目标是要将5G网络的数据传输量提升至4G网络的千倍以上。这种新兴的技术发展为系统商带来不断演进的的全新要求,其中包括提升系统整合度和系统效能、降低系统材料列表(BOM)成本、提高设计灵活度,以及加速产品上市时程等。

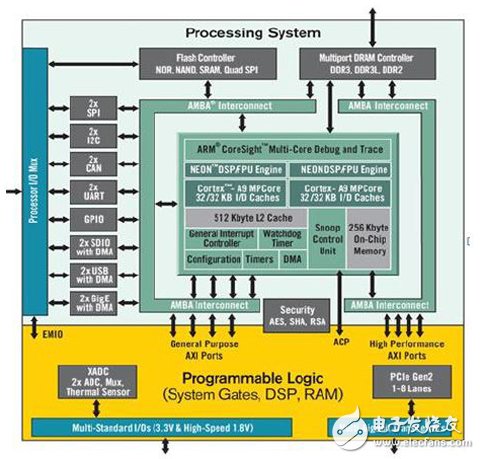

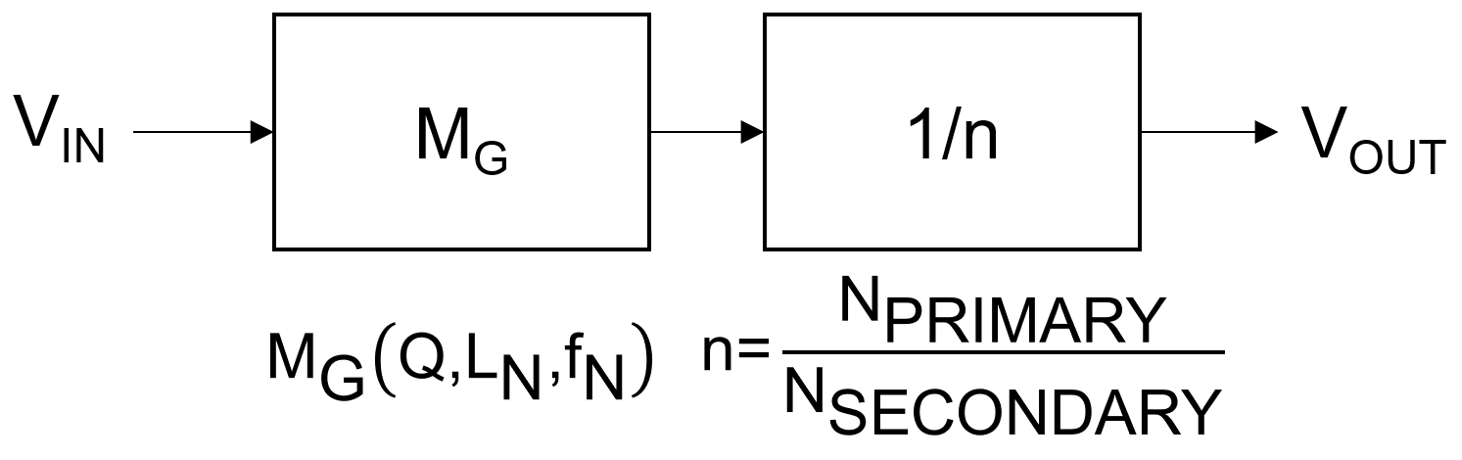

传统ASIC组件支持的硬件解决方案虽然尚可符合功耗和成本目标,但其所需的一次性工程费用(NRE)极高、缺乏灵活性,让产品的上市时程变得非常缓慢。为了因应市场的全新需求和克服以上种种挑战,赛灵思推出All Programmable SoC (APSoC)架构,并成功建置在Zynq-7000产品系列中。Zynq-7000组件采用赛灵思APSoC架构,透过硬件、软件和I/O可编程能力全面提升系统级的差异化、整合度和灵活性(如图一)。

图一 Zynq-7000 All Programmable SoC架构

赛灵思自2011年12月推出Zynq-7000组件以来,已广泛应用于通讯、数据中心、汽车、工业、航天与国防等众多领域。对通讯市场(尤其是无线应用领域)而言,Zynq-7000提供独特的优势:

其整合式可编程逻辑针对数字讯号处理提供高度优化;其采用的ARM Cortex A9处理子系统可有效建置典型无线设备(例如远程无线电和无线回程单元)的控制功能。

在采用Zynq APSoC组件设计无线应用时,必须选择能满足应用需求的操作系统。而在针对不同的无线应用时,必须考虑以下几个关键因素:

1. 电信级运作能力:电信级系统一般都要达到99.999%系统可靠度,也就是系统的正常运行时间要达到这么的水平。从系统运作的角度来看,这代表对系统各项特性的支持,例如冷/暖重开机、故障监测、侦测和处理,以及冗余,都要达到这程度。

2. 实时处理:实时不仅意味着速度要「非常快」,而且要有可预测的反应时间。相较于无线回程处理,远程无线电有不同的实时处理要求。无线电设备讯号处理任务繁重,因此支持讯号处理的处理器必须能满足严格的时序预算要求。

3. 诊断:为了支持现场诊断和事后诊断,需要收集和储存大量效能衡量数据和日志数据,藉此可追踪和管理无线应用的关键指标,例如效能衡量与统计数据、CPU使用率和故障监控、操作系统任务切换和事件历史等指标。

4. 工具与协定整合:除错与诊断环境全面整合,以及一些操作系统厂商提供的特定网络协议堆栈,都有助于设计人员开发有效率的系统和维护高效的系统运作。

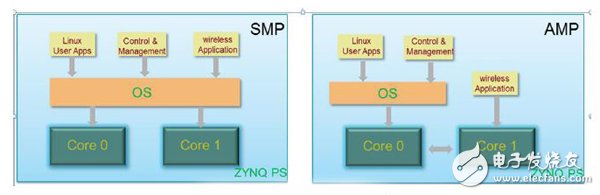

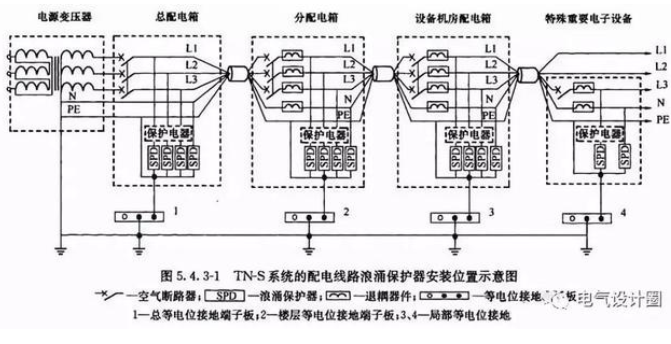

Zynq SoC整合了两颗ARM Cortex A9核心。软件设计师需要在可支持这款ARM核心的SMP(对称多处理架构)或AMP(非对称多处理架构)多处理器架构之间做出选择。如图二所示,在SMP系统架构中,两颗以上完全相同的处理器共同在单一操作系统实例中共享资源。

图二 SMP与AMP之比较

理论上,这种架构在同一个操作系统实例中会平等对待所有处理器。相反地,在有或没有操作系统实例和处理器互相不知彼此存在的情况下,AMP架构会对个别处理器有不同的待遇,而没有执行操作系统的核心则可能会执行一个被视为「裸机」实例的微程序代码。

通常SMP为较高阶的应用提供统一的操作系统平台。软件架构师在操作系统上建置应用时,无需考虑两颗核心之间共享资源和跨行程的通讯问题。此外,SMP的效能消耗会对时间要求严格的无线应用造成影响。相较于SMP,AMP备有操作系统实例的轻量级软件几乎完全没有消耗的问题,但需要精心客制的软件设计来实现处理器资源共享和处理器之间的通讯。

使用Zynq APSoC组件可有效建置多种重要的无线应用,其中包括无线电和无线回程。每种无线应用有不同的效能要求,而且需要操作系统支持不同的特性。无线电应用就是一个很好的Zynq应用案例,因为透过Zynq可建置包括所有数字前端处理功能的完整软硬件整合解决方案。

无线电数字前端应用是4G无线网络中典型远程无线电头端设备(RRH)的主要部分。这种应用的处理要求可分为讯号处理和控制处理。在讯号处理领域,Zynq可用以建置于高采样率滤波器,可达到数字升/降频变频、波峰因子抑制(CFR)和数位预失真(DPD)。然而,DPD是一个特例,需要同时使用Zynq的PS和PL。

DPD处理可细分为高速数据路径和更新路径。更新路径用于定期更新滤波器组的系数,非常适合用于ARM Cortex A9核心。一般来说,系数更新必须在几毫秒到几十毫秒内完成。由于计算的算术复杂性,可使用A9核心和嵌入式NEON SIMD向量运算单元来因应所需的高效能。此外,Zynq PL也可为各种需要大量处理器频率周期的功能提供硬件加速,因而Zynq PL、ARM A9核心和NEON协同处理器可进行协同作业。

无线电的控制处理一般用于初始的无线电校准、配置、警告、排程和从网络终止讯息。这样的作业一般在无线电应用中并不需要高效能,因此使用Zynq组件内建的单一ARM A9核心就能轻松管理。选择合适的架构来支持DPD应用和控制处理应用是非常重要,因为合适的架构会决定整体效能、可靠度和维护的容易度。

AMP模式是无线电应用的通用架构。在此模式下,可透过裸机模式提供一颗完整的ARM核心进行DPD处理作业,因而可提供更多运算余量以满足各种DPD系数更新所需的时间要求。而第二颗由操作系统控制的ARM A9核心则可执行控制和OAM等所有其应用。

在这种架构中,由于操作系统只能控制两颗ARM核心中的其中一颗,因此必须在两颗独立的核心之间建立建立处理器之间的通道,例如使用OCM (On Chip Memory)或共享内存。这对某些重要的控制应用尤其重要,例如用于监控DPD模块状况的应用。这种行程间的通讯(IPC)解决方案并没有标准可循,而是必须在AMP模式中单独开发。

SMP架构非常简单明确,就是使用单一操作系统实例同时控制两颗ARM核心,进而控制所有应用。IPC、除错、支持工具链都在相同的操作系统下运作。为了确保DPD应用有专属的资源,可在软件应用中使用「核心亲和性」(Core Affinity) 和「中断遮蔽」等特殊技术。在前面的案例中,DPD应用只在一个核心上执行,也就是除了操作系统排程器消耗外,DPD应用不会跟其他作业共享资源。而在后面的案例中,除了因DPD应用所需的执行作业外,各种中断服务会直接转由第二颗核心执行。如此一来, DPD应用可充分运用所有资源。

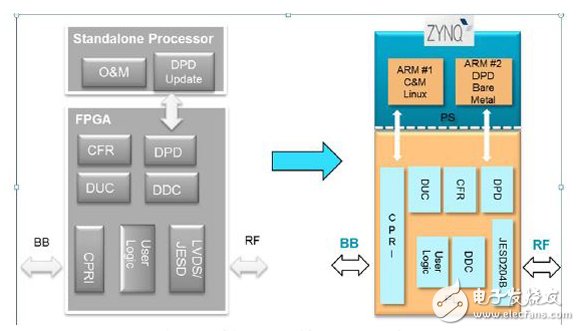

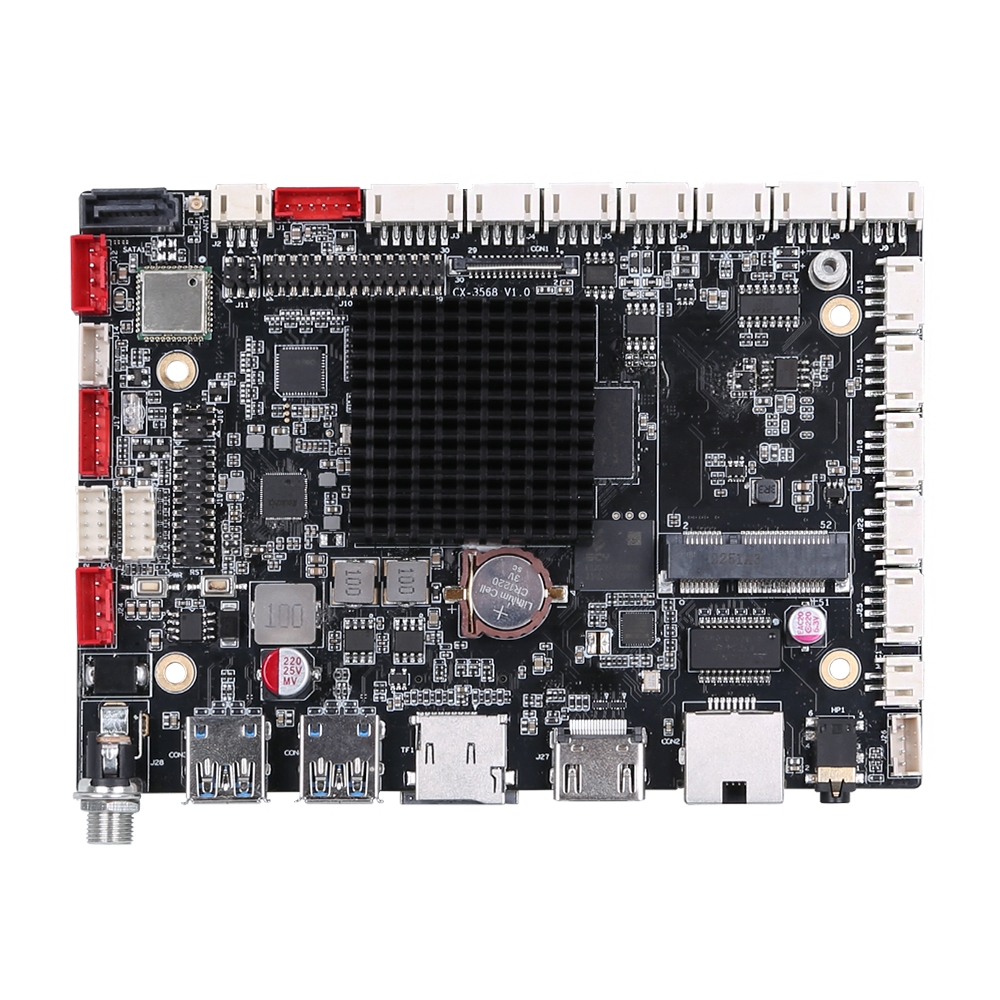

由此可见,Zynq APSoC是支持AMP或SMP架构的理想平台。如图三所示,Zynq整合两颗ARM核心的处理器、12.5Gb/s序列器/解除序列器 (SerDes)、可靠度更高的500MHz+ DSP,并能提供完整的数字前端功能,诸如DPD、CFR、DUC/DDC和CPRI/JESD接口等。这个解决方案无需在处理器和独立的FPGA组件之间设立接口,从而简化PCB设计。

从独立式多芯片解决方案转移到Zynq平台的单芯片整合方案是相当简单明了的。赛灵思提供全面的软硬件解决方案,其中更包括用于DUC、DDC、CFR和DPD的数字讯号处理IP库,有助多芯片方案顺利转移到Zynq平台。此外,赛灵思也提供对多种操作系统解决方案的支持,包含组件驱动程序、启动加载程序、BSP范例和常用的工具。当设计方案成功转移到Zynq平台后,系统效能即可大幅提升,也可节省整体功耗,并降低材料清单(BOM) 成本。

图三 从独立式解决方案转移到Zynq解决方案

以上,我们探讨了为无线应用选择操作系统的主要考虑因素、无线应用的建置架构和其中AMP与SMP比较的考虑因素,以及可直接运用赛灵思Zynq 7000组件的应用。总之,赛灵思提供的高阶组件能让基础架构设备设计人员在实现软硬件可编程性的同时,也可提升效能和系统整合度、降低材料清单 (BOM) 总成本与整体系统功耗,以及实现高可靠度和加速产品上市时程。设计人员现在不仅能加快开发设备,而且还能在设备部署完成后继续可提供现场更新,排除了与ASSP和ASIC等组件相关的风险。

电子发烧友App

电子发烧友App

评论