JEDEC 固态技术协会,微电子产业标准全球领导制定机构,今天宣布正式发布JEDEC DDR3L规范。这是广受期待的DDR3存储器标准JESD79-3 的附件。这是DDR3作为当今DRAM主导性标准演变的继续

2010-08-05 09:10:50 3509

3509 本文以Kintex-7系列XC7K410T FPGA芯片和两片MT41J128M16 DDR3 SDRAM芯片为硬件平台,设计并实现了基于FPGA的视频图形显示系统的DDR3多端口存储管理。##每片

2015-04-07 15:52:10 12311

12311

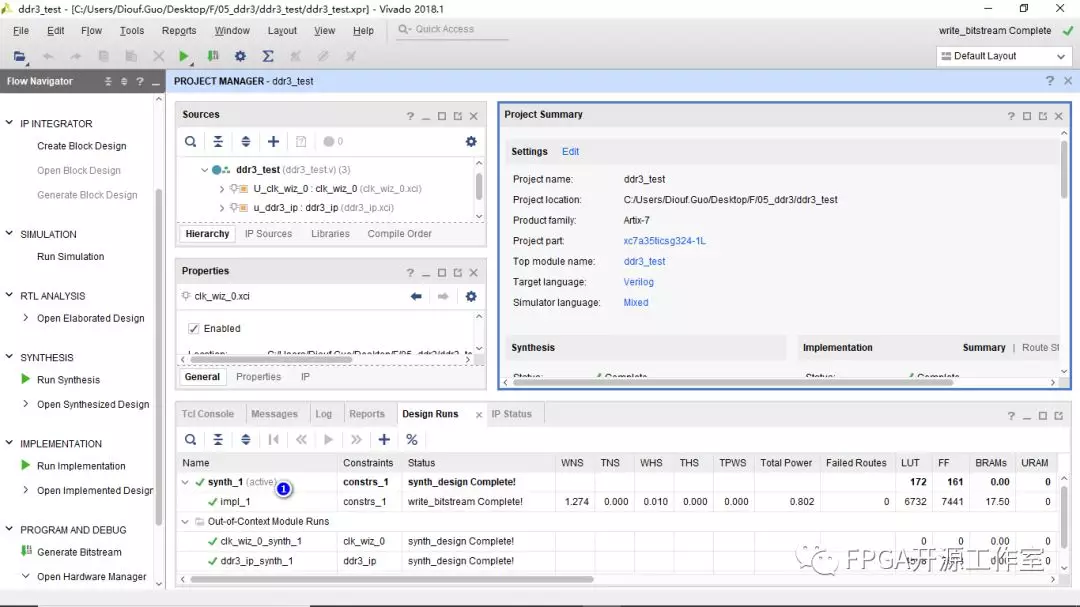

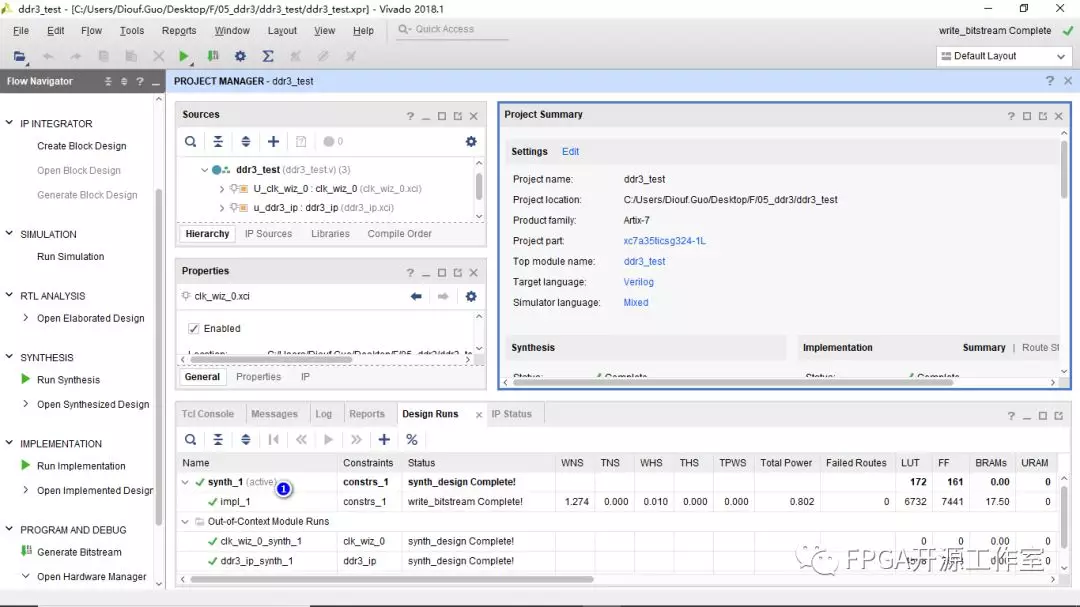

将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T FPGA

2020-12-15 16:45:16 2476

2476

讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。 软件

2021-01-01 10:09:00 3711

3711

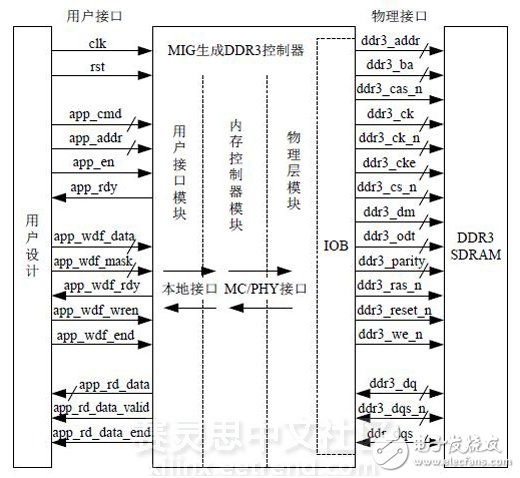

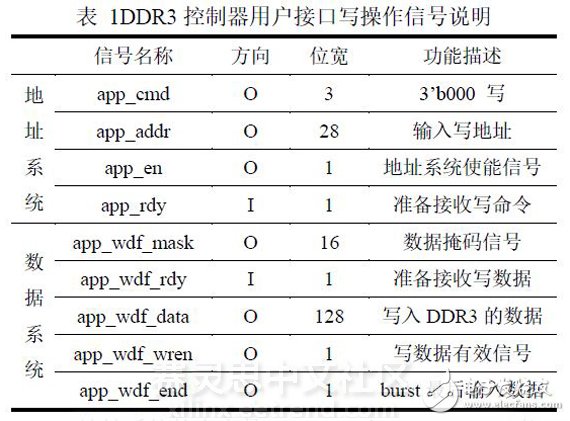

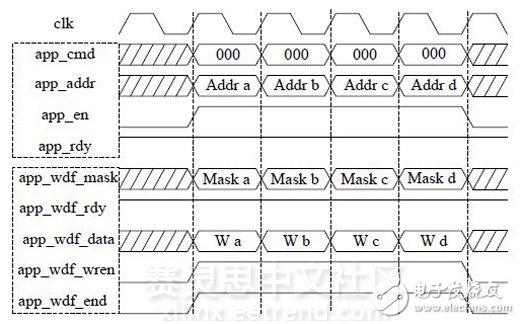

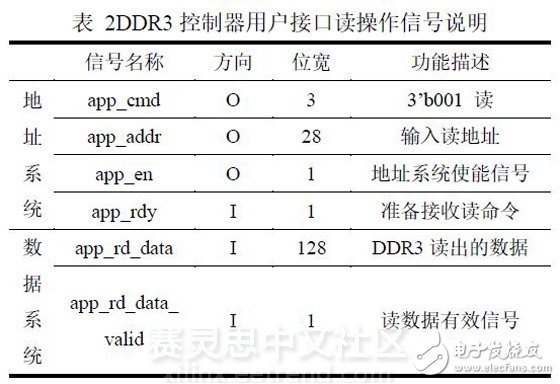

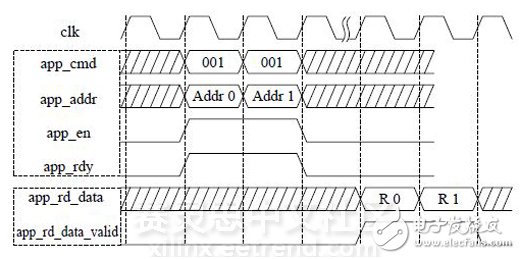

1. 背景 这篇文章主要介绍了DDR3IP核的写实现。 2. 写命令和数据总线介绍 DDR3 SDRAM控制器IP核主要预留了两组总线,一组可以直接绑定到DDR3 SDRAM芯片端口,一组是留给

2020-12-31 11:17:02 5068

5068

本实验为后续使用DDR3内存的实验做铺垫,通过循环读写DDR3内存,了解其工作原理和DDR3控制器的写法,由于DDR3控制复杂,控制器的编写难度高,这里笔者介绍采用第三方的DDR3 IP控制器情况下的应用,是后续音频、视频等需要用到DDR3实验的基础。

2021-02-05 13:27:00 8224

8224

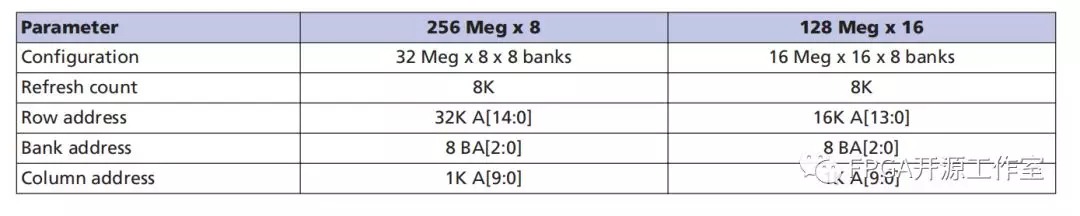

2022年4月20日,中国苏州讯 —— 全球半导体存储解决方案领导厂商华邦电子今日宣布,将持续供应DDR3产品,为客户带来超高速的性能表现。 华邦的 1.35V DDR3 产品在 x8

2022-04-20 16:04:03 2554

2554

同样的GEL在自制板上做DDR3初始化也OK(验证过,DDR3读写都正常,数据没有自跳变),可是问题来我,为什么我用同样的KEYSTONE DDR3 INIT在自制板上做DDR3初始化老是不成功,老是

2019-01-08 10:19:00

存储的所有命令然后实现外部内存的使用。DDR3重排命令的规则基于以下规则:1)如果读命令与先前的写命令操作的是一个不同的块地址(2048个字节),读优先级等于或大于写优先级。2)如果读命令与先前的血

2018-01-18 22:04:33

嗨论坛社区,我使用的是XC7K420T-2FFG1156 7系列FPGA,这里所有的银行都是HR银行。我想将4 GB DDR3连接到FPGA。我提到了xilinx EVM套件,其中DDR3与HP

2020-08-25 07:48:37

数据从L2传递到DDR3中比数据从DDR3传递到L2中运行周期大很多,将近后者的7倍

实验三:把L2SRAM中的数据存储到DDR3中

x_data 存储在L2SRAMZ中

y_dat存储在DDR3中

2018-06-21 17:19:51

嗨,我是FPGA领域的新手。现在我正在使用Genesys2。我必须控制DDR3内存。我在Digilent网站上找到了一些使用micrlaze处理器的DDR3示例。但是,在我的情况下,我不必

2019-05-05 15:29:38

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA进出。DDR3存储器系统在大多数情况下可以为这些基于FPGA的系统

2019-05-24 05:00:34

1概述 当今计算机系统DDR3存储器技术已得到广泛应用,数据传输率一再被提升,现已高达1866Mbps.在这种高速总线条件下,要保证数据传输质量的可靠性和满足并行总线的时序要求,对设计实现提出

2014-12-15 14:17:46

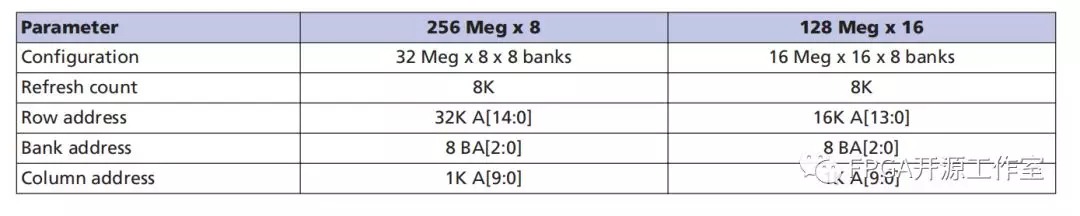

HI,我的FPGA是Kintex-7的XC7K410T-2FFG900。我的DDR3是2Gb,由128Mb * 16组成。 DDR3数据速率为1600Mbps,因此我必须在HP BANK中使用VRN

2020-07-21 14:47:06

大家好,最近在学习DDR3的读写,用的是Spartan-6的 x16,DDR3型号MT41J64M16,在进行write时,地址总是出现两遍,第一遍后面出现data=XXXX,感觉像是data

2018-06-28 19:11:52

CPU的DDR3总线只连了一片DDR3,也没有复用总线将DDR3的CS直接拉到地的话,DDR3初始化不成功所以说DDR3的CS信号是通过沿采样的吗,电平采样不行?无法理解啊还是有其他方面原因

2016-11-25 09:41:36

DDR3芯片读写控制及调试总结,1. 器件选型及原理图设计(1) 由于是直接购买现成的开发板作为项目前期开发调试使用,故DDR3芯片已板载,其型号为MT41J256M16HA-125,美光公司生产的4Gb容量DDR3芯片。采...

2021-07-22 08:33:54

不同的标准外,还应该能够提供动态的OCT和可变摆率,以此来管理信号的上升和下降时间。结论DDR3在未来即将超越DDR2的使用,高端FPGA提供的低成本、高效能、高密度和良好的信号完整性方案必须满足JEDEC读写均衡要求。来源:EDN CHINA

2019-04-22 07:00:08

各位大虾,我想设计一个检测FPGA的外挂DDR3硬件是否有问题的程序。目前先做初级阶段工作,主要实现以下几点:1、检测DDR3数据线DQ是否有错连和漏连(虚焊)的情况,如有找到对应的错误处;2

2013-04-12 13:00:45

DDR3的理论带宽怎么计算?用xilinx的控制器输入时钟200M。fpga与DDR的接口如下:

2016-02-17 18:17:40

=1.5V;但我看了一篇FPGA的DDR3 IP核例化文章,上面写FPGA的BANK1,3连接外部存储控制器(如下图,且只有四个BANK),所以要将DDR3连接在BANK3上。所以DDR3如何与FPGA芯片

2021-11-29 16:10:48

如果没有将均衡功能直接设计到FPGA I/O架构中,那么任何设备连接到DDR3 SDRAM DIMM都将是复杂的,而且成本还高,需要大量的外部元器件,包括延时线和相关的控制。

2019-08-21 07:21:29

各位专家,我使用altera的cyclone5的DDR3硬核控制器,输入时钟是国产的125兆50PPM有源晶振,现在调试时发现对DDR3的读写偶尔出错。我们测试DDR3接口的差分时钟,发现左右抖动

2018-05-11 06:50:41

先用spartan6对ddr3进行读写操作,想知道ddr3一般上电多久后可对其进行读写操作?求大神解答,感谢!

2014-06-14 16:13:45

你好,ISE版本为13.3,modelsim版本为10.1c 64bit.MIG工具为ddr3生成mcb。modelsim的transcript窗口中的消息如下

2019-07-08 08:44:42

本次发布 Gowin DDR3参考设计。Gowin DDR3 参考设计可在高云官网下载,参考设计可用于仿真,实例化加插用户设计后的总综合,总布局布线。

2022-10-08 08:00:34

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3资料。

2016-05-27 16:39:58

DDR3的IP核配置完毕后,产生了好多文件,请问如何调用这些文件实现DDR3的读写呢?看了一些文章,说是要等到local_init_done为高电平后,才能进行读写操作。请问DDR3的控制命令如

2016-01-14 18:15:19

稳定的工作。项目名称:DDR3。 具体要求:实现DDR3数据的读写。 系统设计:实现过程:1.新建工程之后打开Create BlockDesign,并修改Design name。2.按照系统设计依次添加

2021-07-30 11:23:45

本视频是Combat FPGA开发板的配套视频课程,本章节课程主要介绍Gowin中DDR3 的基础知识、DDR3的IP core的特性和使用以及DDR3的IPcore例程的仿真。课程资料包含DDR3

2021-05-06 15:34:33

嗨,我正在设计一个定制FPGA板&我将使用带有Kintex(XC7K160T-2FFG676C)FPGA的DDR3 RAM。我阅读了xilinx& amp; amp; amp

2020-04-17 07:54:29

关于DDR3的时序(Altera的外部存储器接口手册)1. 关于突发地址的对齐(Burst-Aligned Address),是指突发时加载的地址,与突发长度之间,正好符合对齐关系。即当前地址

2018-03-16 10:46:27

我是一名labview FPGA程序员,使用的是NI 7975 fpga模块,它具有kintex 7 fpga。该模块具有外部DDR3 DRAM 0f 2GB以及kintex 7 fpga资源。数据应该从芯片到芯片之间会有多少延迟?这是DDR3 DRAM双端口(同时读写操作可能??)???

2020-05-20 14:42:11

MT41J25616XX用于DDR3芯片。当我们使用MIG工具配置DDR3时,对于我们的FPGA,此DDR3组件未显示在支持的DDR3组件列表中。如果我们使用“创建自定义部件”添加我们的芯片,那么

2019-02-18 09:01:37

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA进出。DDR3存储器系统在大多数情况下可以为这些基于FPGA的系统

2019-05-27 05:00:02

控制器的编写,并在Kintex-7 FPGA芯片上完成了功能测试及实现。1 DDR3连续读写操作的FPGA 实现设计选用8片Mircon公司型号为 MT42J128M16的芯片作为缓存区。每片芯片

2018-08-02 09:34:58

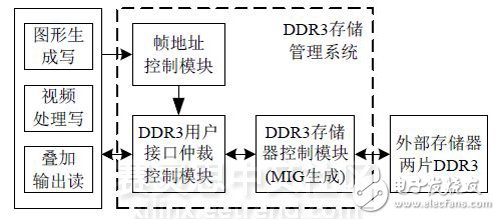

,设计的DDR3存储管理系统简化了多端口读写DDR3的复杂度,提高并行处理的速度。引言机载视频图形显示系统主要实现2D图形的绘制,构成各种飞行参数画面,同时叠加实时的外景视频。由于FPGA具有强大逻辑资源、丰富

2018-08-02 11:23:24

设计的基于AXI4的DDR3多端口方案虽然传输速率有所提高,但由于AXI4协议本身的复杂性增加了开发使用的难度。本文实现并验证了期货行情数据加速处理中基于FPGA的DDR3六通道UI接口读写防冲突

2018-08-02 09:32:45

Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取的应用背景,设计和实现了

2018-08-30 09:59:01

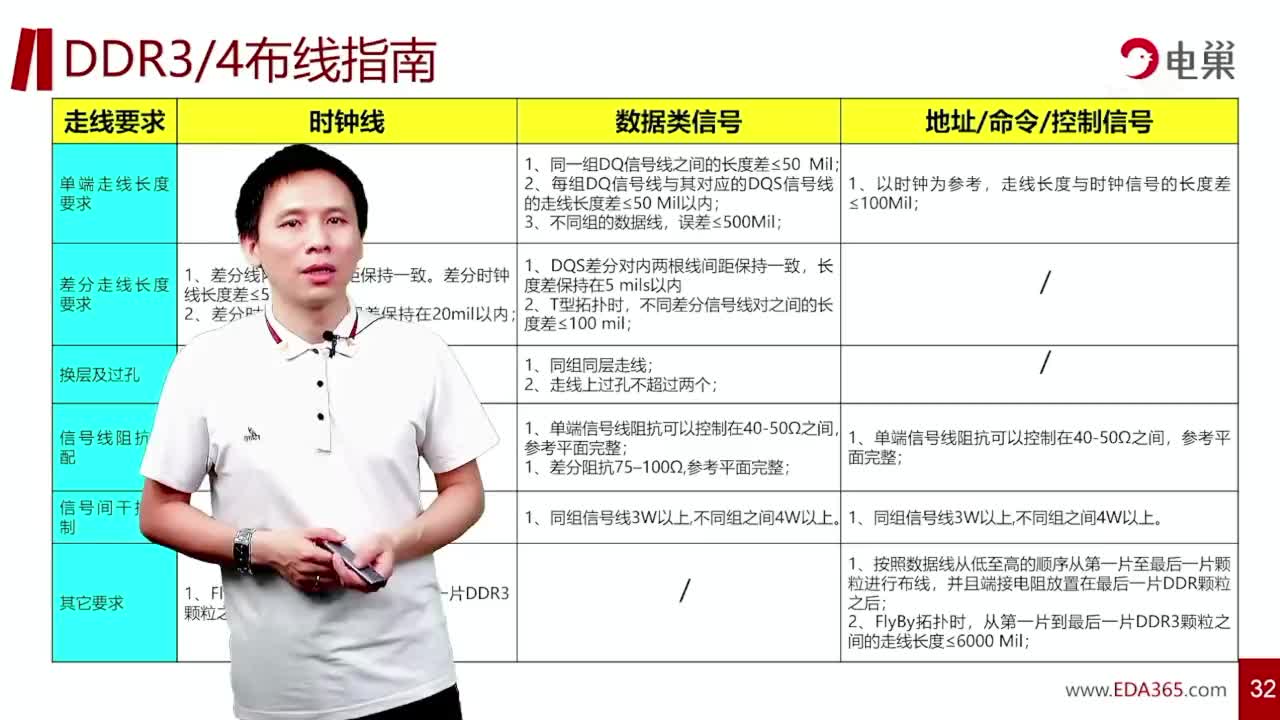

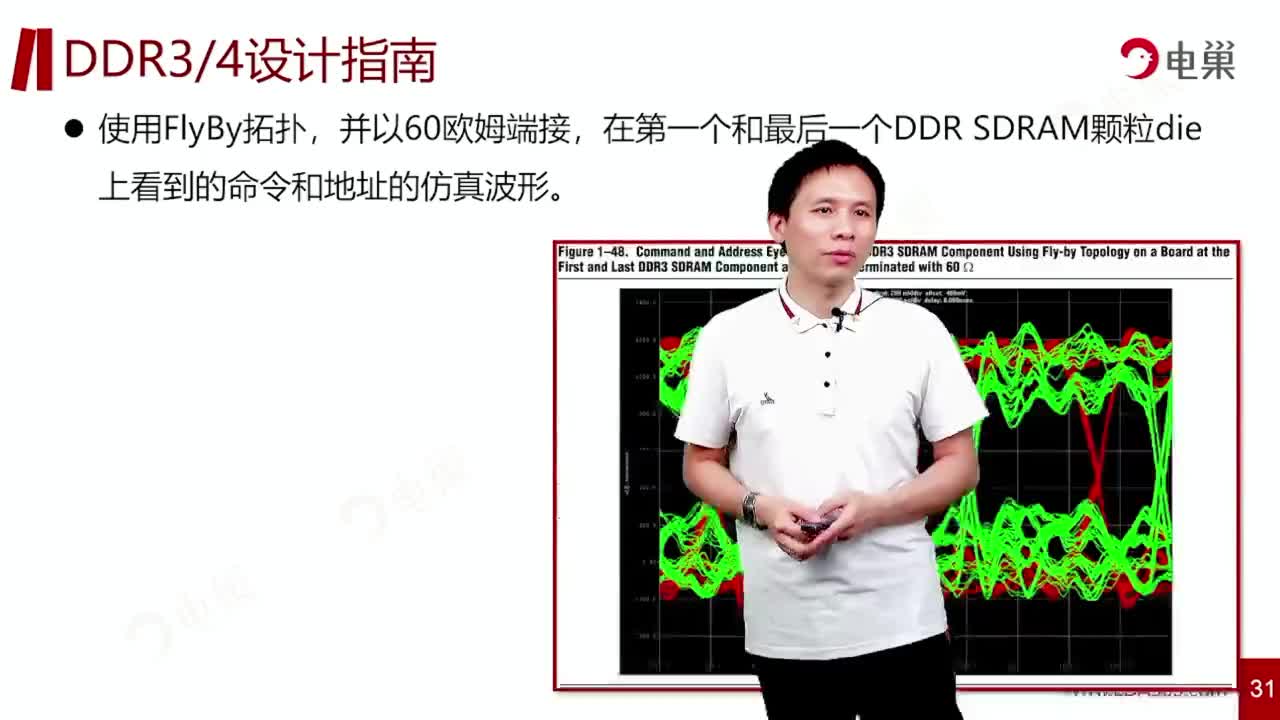

本手册以 DDR3 器件为例讲解硬件设计方法,包括 FPGA I/O 分配、原理图设计、电源网络设计、PCB 走线、参考平面设计、仿真等,旨在协助用户快速完成信号完整性好、低功耗、低噪声的高速存储

2022-09-29 06:15:25

吞吐量大、功耗低的需求,因此选择DDR3 SDRAM作为机载视频图形显示系统的外部存储器。本文以Kintex-7系列XC7K410T FPGA芯片和两片MT41J128M16 DDR3 SDRAM芯片为硬件平台,设计并实现了基于FPGA的视频图形显示系统的DDR3多端口存储管理。

2019-06-24 06:07:53

占用1个FIFO,高32bit的数据位宽则会闲置。由此可见,MPFE在使用上十分灵活,能够适应不同的应用方式,满足FPGA内部不同逻辑模块对Memory的读写访问。3 多端口前端的调度策略MPFE本身

2019-06-13 05:00:06

基于Xilinx MIS IP的DDR3读写User Interface解析特权同学,版权所有,转载请注明出处参考文档:ug586_7Series_MIS.pdf1. Command时序首先,关于

2016-10-13 15:18:27

均衡的定义和重要性是什么如何实现FPGA和DDR3 SDRAM DIMM条的接口设计?

2021-05-07 06:21:53

DDR3存储器控制器面临的挑战有哪些?如何用一个特定的FPGA系列LatticeECP3实现DDR3存储器控制器。

2021-04-30 07:26:55

现在因为项目需要,要用DDR3来实现一个4入4出的vedio frame buffer。因为片子使用的是lattice的,参考设计什么的非常少。需要自己调用DDR3控制器来实现这个vedio

2015-08-27 14:47:57

。然而,现在新一代中档的FPGA提供这些块、高速FPGA架构、时钟管理资源和需要实现下一代DDR3控制器的I/O结构。那么,究竟怎么做,才能用中档FPGA实现高速DDR3存储器控制器呢?

2019-08-09 07:42:01

在一个项目中,发现数据有异常,想判断FPGA外挂的DDR3正常工作。因为实际生产中,ddr容易出现虚焊或者使用一段时间后管脚出现接触不良等问题。{:2:}现在想编写一个程序来快速判断,不知道应该如何实现,不知道大家有没有好的意见,谢谢大家啦

2013-04-12 16:56:00

怎样对DDR3芯片进行读写控制呢?如何对DDR3芯片进行调试?

2021-08-12 06:26:33

目前有一个项目需要使用DDR3作为显示缓存,VGA作为显示器,FPGA作为主控器,来刷图片到VGA上。VGA部分已经完成,唯独这个DDR3以前没有使用过,时序又比较复杂,所以短时间内难以完成,希望做过DDR3控制器的大神指点一二。急求!!!!

2015-11-16 09:18:59

一、实验要求

生成 DDR3 IP 官方例程,实现 DDR3 的读写控制,了解其工作原理和用户接口。

二、DDR3 控制器简介

PGL50H 为用户提供一套完整的 DDR memory 控制器

2023-05-31 17:45:39

数据速率 800Mbps

一、实验要求

生成 DDR3 IP 官方例程,实现 DDR3 的读写控制,了解其工作原理和用户接口。

二、DDR3 控制器简介

GL50H 为用户提供一套完整的 DDR

2023-05-19 14:28:45

请问FPGA与DDR3是否必须在同一层放置,由于现在不在同一层,软件调试的时候图像有抖动,软件说是因为FPGA与DDR3未在同一层,导致时序有问题。

2018-12-26 09:37:37

我输入125兆时钟给FPGA,经过FPGA内部的PLL产生300兆的时钟给FPGA内部的DDR3控制硬核,但是现在发现对外部ddr3的读写数据不稳定。请问各位专家,ddr3的时钟频率稳定度需要多少PPM以内?对输入时钟的jitter有要求吗?

2018-05-10 15:42:23

我需要在V7中实现与DDR3 SDRAM相同的功能和接口。这意味着命令/地址,读取数据和写入数据流的方向与MIG的方向不同。这可以实现吗?

2020-07-14 16:18:04

本文介绍了以双口RAM 和FIFO 为例,利用多端口存储器设计多机系统。对双口RA 几FIFO进行了比较。

2009-11-27 12:03:34 6

6 用中档FPGA实现高速DDR3存储器控制器

引言

由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储技术进行了优化。下一代双数据速率(D

2010-01-27 11:25:19 879

879

在实际应用中,可能会碰到大型矩阵转置的需求,尤其是对于图像应用,转置就是实现图像的90°旋转。 由于FPGA片内的RAM资源一般不足以缓存这样大规模的矩阵数据,所以一般都要借助于外部的存储器,一般

2017-02-07 17:49:11 4005

4005

构建SoC系统,毕竟是需要实现PS和PL间的数据交互,如果PS与PL端进行数据交互,可以直接设计PL端为从机,PS端向PL端的reg写入数据即可,本节研究如何再实现PL端对DDR3的读写操作。

2017-09-18 11:08:55 23

23 DDR3是目前DDR的主流产品,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。最开始的DDR, 芯片采用的是TSOP封装,管脚露在芯片两侧的,测试起来相当方便;但是,DDRII和III就不一样了,

2017-11-06 13:44:10 8454

8454

为解决超高速采集系统中的数据缓存问题,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行

2017-11-16 14:36:41 19504

19504

本文详细介绍了在Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取

2017-11-17 14:26:43 24269

24269

针对采用DDR3接口来设计的新一代闪存固态盘(SSD)需要完成与内存控制器进行通信与交互的特点,提出了基于现场可编程门阵列( FPGA)的DDR3协议解析逻辑方案。首先,介绍了DDR3内存工作原理

2017-12-05 09:34:44 10

10 其他元件,占用了宝贵的电路板空间。

Stratix® III FPGA具有专用内置I/O电路,降低了高速DDR3存储器设计的难度。观看这一演示,了解怎样轻松实现1,067 Mbps DDR3存储

2018-06-22 02:04:00 3477

3477 大家好,我叫Paul Evans,是Stratix III产品营销经理。到目前为止,我已经从事了6年的双倍数据速率存储器工作,今天和大家一起讨论一下DDR3。DDR3的主要难题之一是它引入了数据交错

2018-06-22 05:00:00 8250

8250 /s;樊博等使用UI接口,DDR3通信的最大带宽可达3.8 Gb/s;张宇嘉等设计的基于AXI4的DDR3多端口方案虽然传输速率有所提高,但由于AXI4协议本身的复杂性增加了开发使用的难度。本文实现并验证

2018-08-01 15:25:11 3184

3184

这展示了DDR3内存的Kintex-7 FPGA接口功能。

2018-11-30 06:23:00 6002

6002 通过之前的学习,CPU可以读写DDR3了,PL端的Master IP也可以读写DDR3了,那二者就可以以DDR3为纽带,实现大批量数据交互传输。

2020-07-27 08:00:00 16

16 POD模式; 增加ACT_n控制指令为增强数据读写可靠性增加的变更点主要有: DBI; Error Detection;1 电源变化DDR3与DDR4的96 Ball封装pin定义...

2021-11-06 20:36:00 28

28 一、DDR3简介 DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据

2022-12-21 18:30:05 1915

1915 视频图形显示系统理想的架构选择。视频处理和图形生成需要存储海量数据,FPGA内部的存储资源无法满足存储需求,因此需要配置外部存储器。 与DDR2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电,能够满足吞吐量大、功耗低的需求,因此

2023-06-08 03:35:01 1024

1024 本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到AXI总线上,那就要通过MIG IP核提供的AXI接口来读写DDR。

2023-09-01 16:20:37 1896

1896

本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 745

745

DDR3是2007年推出的,预计2022年DDR3的市场份额将降至8%或以下。但原理都是一样的,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。

2023-10-18 16:03:56 518

518

正在加载...

电子发烧友App

电子发烧友App

评论