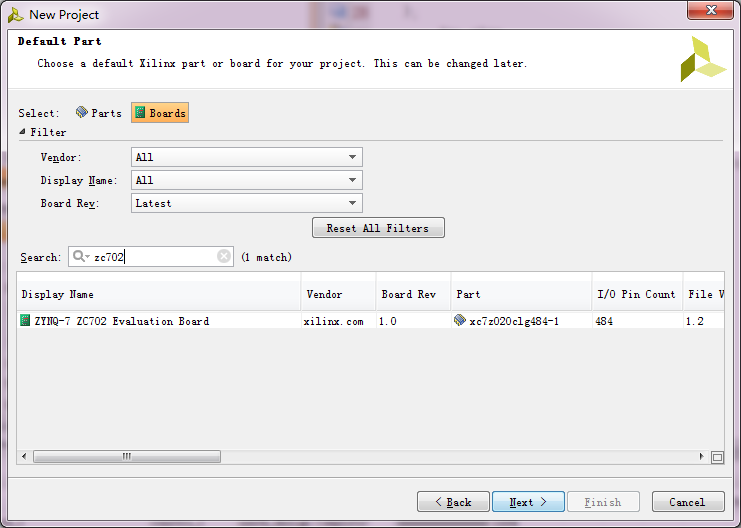

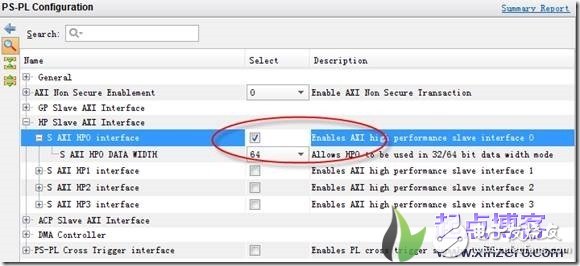

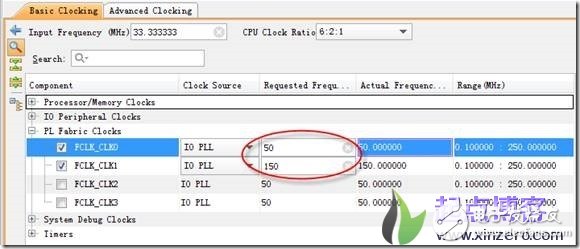

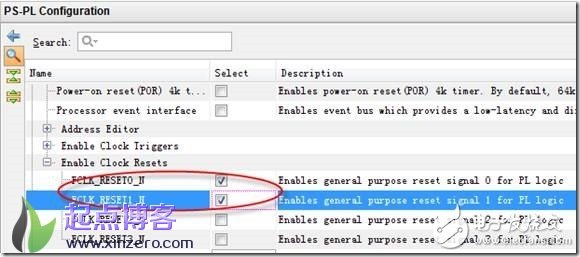

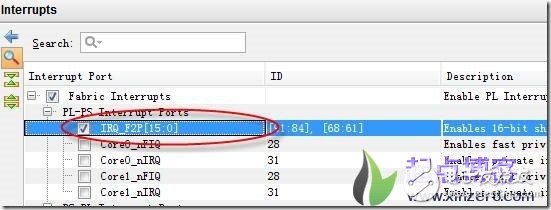

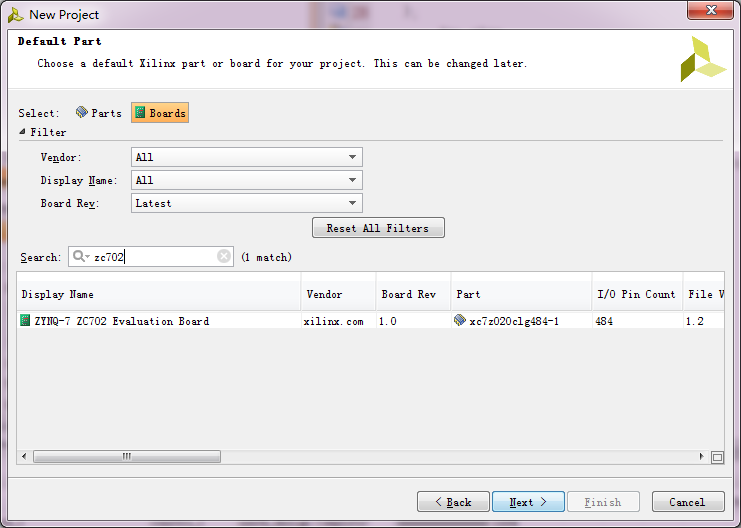

Boards选择zc702 2.单击Create Block Design, 命名 3.添加IP,ZYNQ7 Processing System 4.双击添加的IP,设置如下(主要是设置时钟,内存,输出,默认

2020-12-26 11:48:59 2941

2941

双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 403

403

嗨,我正在使用Vivado 13.2在Zynq 7000上实现嵌入式设计。这是我的设计流程1)创建了一个新项目my_ip,其中包含1个ngc文件和2个从Xilinx Fifo Generator生成

2020-04-15 10:22:15

关于Zynq的Vivado 2013.1发行说明说:“需要及早访问Vivado IP集成商”。这是什么意思?它是否真的支持Zynq开箱即用?提前致谢。以上来自于谷歌翻译以下为原文Vivado

2018-12-04 11:00:58

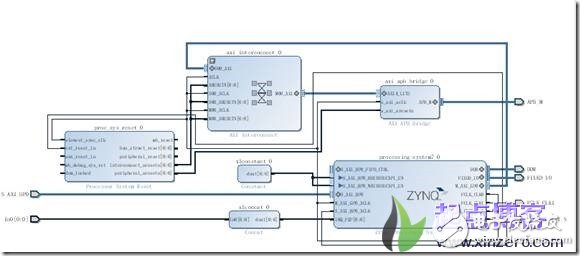

this:Vivado: New Project... New Block DesignThrow down a ZynqAdd an AXI InterconnectZynq Master ->

2018-10-24 15:26:21

你好。当我试图为我的ZYBO板合成zynq hw时,我得到了以下的licnese错误。我检查了我的vivado许可证是否在许可证管理器中正确加载。请参阅随附的文件了解详细信息。我该怎么办?警告

2018-12-25 11:03:50

Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCV应用加入赛灵思免费在线研讨会,了解如何在Zynq®-7000 All Programmable

2013-12-30 16:09:34

可能会用上,当然这个在后期也是可以补充添加的,使用Add Design Tools or Devices,安装完成后在开始菜单中有Xilinx的链接文件夹目录下选择对应版本的Vivado,目录下就有

2019-07-18 15:40:33

可能会用上,当然这个在后期也是可以补充添加的,使用Add Design Tools or Devices,安装完成后在开始菜单中有Xilinx的链接文件夹目录下选择对应版本的Vivado,目录下就有

2023-09-06 17:55:44

Xilinx设计工具ISE设计套件系统版+ Vivado系统版14.3是否可以为此版本的软件进行静默安装?任何意见,将不胜感激干杯以上来自于谷歌翻译以下为原文Xilinx Design Tools

2018-12-28 10:53:04

Xilinx+Zynq-7000嵌入式系统设计与实现++基于ARM+Cortex-A9双核处理器和Vivado的设计方法+高清+带索引书签目录_何宾,张艳辉编著

2018-06-19 22:47:16

Xilinx.Vivado.Design.Suite.2014.4-ISO 1DVDXilinx.Vivado.Design

2014-12-23 13:11:08

supply rails needed for a Xilinx® Zynq® 7000 series (XC7Z045)Design optimized to support 12V

2018-11-05 16:42:31

CPUCPU为Xilinx Zynq-7000SOC,兼容XC7Z035/XC7Z045/XC7Z100,平台升级能力强,以下为Xilinx Zynq-7000特性参数:TLZ7xH-EasyEVM

2022-01-03 07:50:21

今天给大侠带来简谈Xilinx Zynq-7000嵌入式系统设计与实现,话不多说,上货。Xilinx的ZYNQ系列FPGA是二种看上去对立面的思想的融合,ARM处理器的串行执行+FPGA的并行执行

2021-11-09 06:43:27

CPUCPU为Xilinx Zynq-7000SOC,兼容XC7Z035/XC7Z045/XC7Z100,平台升级能力强,以下为Xilinx Zynq-7000特性参数:电源接口和开关采用12V3A

2021-12-30 07:55:37

C66x 定点/浮点DSP以及Xilinx Zynq-7000系列SoC处理器XC7Z035-2FFG676I设计的异构多核评估板,由核心板与评估底板组成。XQ6657Z35-EVM评估板

2023-02-24 10:00:56

目的本文介绍广州星嵌DSP C6657+Xilinx Zynq7035平台下Xilinx Zynq7035算力指标。基本概念FLOPs/FLOPSFLOPs,Floating Point

2022-12-15 21:19:38

描述 PMP10601 参考设计提供为 Xilinx® Zynq® 7000 系列 (XC7Z015) FPGA供电时所需的所有电源轨。此设计使用多个 LMZ3 系列模块、多个 LDO 和一个

2022-09-28 06:24:34

描述此 PMP10600.1参考设计提供为 Xilinx® Zynq® 7000 系列 (XC7Z015) FPGA供电时所需的所有电源轨。此设计使用多个 LMZ3 系列模块、多个 LDO 和一个

2022-09-23 07:43:32

/valueTarget#echo 0 > /sys/class/gpio/gpio905/value图 61.1 Vivado工程说明进入BLOCK DESIGN开发界面,双击IP核框图,可查

2021-05-28 14:28:28

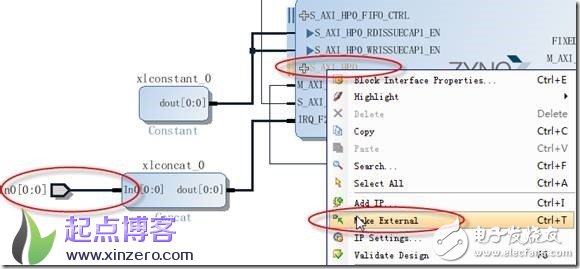

ZYNQ7000搭建嵌入式Linux操作系统-增加PL端外设一、VIVADO工程建立二、VIVADO工程设置虚拟机下生成内核和uboot.elfSDK生成设备树和BOOT.bin一、VIVADO工程

2021-12-17 06:42:06

为:MT25QL256ABA1EW9-0SIT。增加Block Design设计文件首先,打开已经完成的Vivado设计例程,点击Project Manager下面的IP Integrator -> Create

2023-02-13 20:21:27

本文主要介绍说明XQ6657Z35-EVM 高速数据处理评估板ZYNQ与DSP之间EMIF16通信的功能、使用步骤以及各个例程的运行效果。[基于TI KeyStone架构C6000系列

2023-03-21 15:30:37

... https://forums.xilinx.com/t5/Design-Entry/Mix-legacy-HDL-with-block-design-for- ZYNQ / MP / 678022

2020-05-19 08:15:15

各位大神,请教一个问题。目前正在使用Xilinx新出的Vivado 软件生成DMA和PCIE集成的IP核,在此基础上又生成了一个example design,但是在仿真的时候报错。是Xilinx的这款产品不够成熟还是我操作有错误??各位大神有没有遇到此类问题的??

2017-01-13 21:56:41

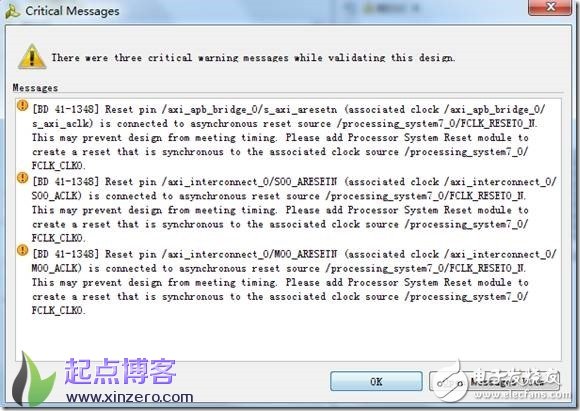

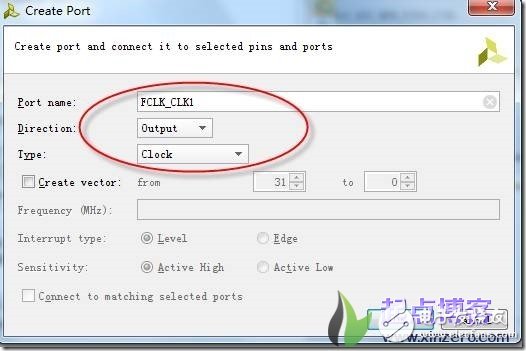

你好,我在Win10中使用vivado 2016.2 for zynq7020。我的时钟方案是zynq PS FCLK_CLK0-->时钟向导IP输入(Primitive PLL)的输入。合成

2018-11-05 11:40:53

哪位大神能够分享一下关于xilinx vivado 2013.4 的教程啊,小弟感激不敬!!!

2014-03-26 21:38:02

ZYNQ将CPU和FPGA集成到了一起 开发人员需要具备技能: 1.ARM操作系统应用程序 2.设备驱动程序 3.FPGA硬件逻辑设计 需要了解Linux操作系统,系统架构,FPGA和ARM系统之间

2021-07-22 08:55:46

嗨,大家好,在Zynq ultrascale +设备(xczu9eg-ffvb1156-2-e)上实现我的设计时,我注意到BRAM的急剧增加,导致实现失败。合成后Vivado报道2.

2018-11-08 11:24:01

`描述This TPS65218-based reference design is a compact, integrated power solution for Xilinx® Zynq

2015-03-10 15:15:21

在vivado 2017.2.1的place_design phase4.1中找不到存档错误。这是日志声明

2018-11-07 11:36:11

设计的方式。

为什么要用XVC?

方便,不需要额外的JTAG设备即可调试PL逻辑代码。

在 vivado 中绘制如下 Block Design:

以上 Block Design 包含两个重要的IP核

2023-09-16 14:15:14

页上点击获取。将邮箱中的Xilinx.lic文件下载好 然后点击如下的选项,将刚刚下载好的文件加载进来弹出如下的对话框,说明软件激活成功,可以免费使用30天 接下来点击桌面的Vivado 2017.4

2020-05-31 10:20:03

您好,我想下载Xilinx Vivado 2017.1但是,每次我收到以下错误:“由于您的帐户导出合规性验证失败,我们无法满足您的要求。”谁能帮我?提前致谢以上来自于谷歌翻译以下为原文Hello

2018-12-27 10:41:52

我的Zedboard附带了“ISE Design Suite:Design Edition Device Locked Edition Node-Locked”的许可证。我一直在使用Vivado

2019-10-14 07:00:16

至 ZYNQ 的 S_AXI_GP0,以访问 PS QSPI 控制器。

BD 中需要分配 XDMA 的 M_AXI 地址如下,可以用 AMD Vivado™ 的自动地址分配工具完成

2023-11-30 18:49:15

vivado you can now use IP integrator in which it is using IP to create a Block design.What is the most

2019-03-29 09:14:55

/sw_manuals/xilinx2017_4/ug905-vivado-hierarchical-design.pdf Particularly I am interested in Bottom

2018-11-12 14:42:01

请问一下Xilinx公司发布的vivado具体的作用是什么,刚刚接触到,以前一直用quartus ii,没有使用过ise,后来今天听说了vivado,不知道是做什么用的,希望大家都能参与讨论中,谢谢。

2015-04-15 16:51:00

框架,在本文中用于算法的仿真和参数的训练。 Vivado HLS和Vivado 是Xilinx公司Vivado Design Suite套件中的两个软件。vivado-HLS可以将 C,C++ 以及

2021-01-15 17:09:15

.Vivado 2016.4与Spartan-6不兼容。据Xilinx称,Vivado不支持任何早于7系列的设备系列。)根据以下说明,Xilinx System Generator可以嵌套在ISE Design

2018-12-27 10:55:34

假设我在Vivado 2015.2的Block Design中有三层设计。此块设计看起来像Hierarchy_0(Hierarchy_1(Hierarchy_2))。当我双击

2018-12-25 10:58:37

在一个Demo中找到一个工程叫petalinux_sd,我将它另存为My_Work,可是其中的Block Design仍然叫petalinux_sd,其顶层文件仍然叫

2021-08-06 16:04:53

大家好,我正在尝试在Ubuntu 13.10上安装Vivado 2013.2我按照描述的步骤进行操作(sudo apt-get install openjdk-7-jre,sudo mv /opt

2018-12-10 10:29:37

工程说明参照创龙TLZ7xH-EVM评估板(ZYNQ Z-7045/Z-7100)《基于TcL脚本生成Vivado工程及编译》文档,使用TcL脚本生成Vivado工程。(1)生成评估板

2020-09-17 09:48:13

对你所有的人来说,我已经阅读了有关IP Block Designs的手册和培训材料,并成功地生成了AXI LITE BRAM IP设计,以及之前在USER社区中为您提供的一些帮助。我所坚持

2020-03-20 08:52:30

你好,我现在正在学习如何使用Vivado。现在我在Vivado中“实现”并点击“Open Implementation Design”后获得一个网表。这是我的网表图片。我可以知道ZYNQ芯片上的确

2018-10-19 14:38:09

亲爱的Xilinx社区,因为我的应用需要3个SPI控制器,而且我已经在Zynq中使用了现有的2个SPI控制器。我知道在生成比特流后如何在linux内核中完成此操作但是,因为我是vivado的新手,你

2020-05-21 09:13:54

案例的使用说明,适用开发环境: Windows 7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4

2023-01-01 23:52:54

案例的使用说明,适用开发环境: Windows 7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4

2023-08-24 14:40:42

Vivado设计套件用户指南:嵌入式处理器硬件设计 讨论使用Vivado™IP集成器和Xilinx软件开发套件(SDK),使用Zynq®-7000 All Programmable(AP)SoC

2017-11-15 10:34:10

前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 09:38:32

xilinx.notification@entitlenow.com with the ‘get license’ links. The installation steps require Vivado Design Suite\Vivado

2018-12-19 11:21:19

xczu3eg-sfvc784-1-e ,点击Next,点击Finish。新建的vivado工程,如下图所示Step2 新建Block Design点击导航栏的Create Block Design,出现Create

2019-08-07 15:05:33

License_Type:Design_Linking; ipman,jesd204,ip,permanent,_0_0_0,文件名为/opt/Xilinx/Vivado/2013.4/data/ip

2018-12-10 10:39:23

of the original Vivado design.Changing the Zynq processor is out of the question since we are designing

2019-03-28 15:25:25

亲爱的Xilinx,是否有可能更新ug873 zynq ctt的vivado版本?谢谢。伟

2020-03-27 09:41:17

Vivado 2016.1中的Block Design终止未使用的双向信号的正确方法是什么?以上来自于谷歌翻译以下为原文I have a Zynq based design that brings out

2018-10-26 15:07:26

I'm using Xilinx Vivado. My current design is in 2015.3 (some parts are already in 2015.4) and I

2018-12-19 11:07:18

求xilinx_Zynq7000的学习资料,相关的xilinx学习资料也可以,本人有Altera的资料,有需要的请讲

2019-01-29 06:35:20

Vivado的主视图中,出现了如图所示的Block Design界面。在Diagram中,点击中央的小加号,准备添加zynq的处理器IP核。如图所示,在弹出IP列表的Search后面,我们输入

2019-09-30 12:57:32

嗨,你能告诉我在闪存存储器MT29F1G08ABADAWP-IT:D的vivado工具中设置的设置,来自制造商Micron与Xilinx Zynq Soc XC7Z020-2CLG400I一起

2019-03-27 10:14:33

对基于Xilinx的开发很新?我还假设版本2015.2也会受到支持吗?链接如下。请检查本页末尾公布的许可证,如果合适,请告知我们。http://www.xilinx.com/products/design-tools/vivado.html#buy谢谢,Satrajit

2020-05-06 07:58:17

嗨,我的设计在合成中使用141.5 BRAM瓦片。但是,在Zynq中可以使用140 BRAM瓦片。实施后,这个数量下降到133瓦。我的问题是vivado如何减少这一数量?实施?这点可以导致未来

2018-10-31 16:17:40

描述PMP9335专为使用 TPS84A20 和 TPS84320 的 Xilinx Zynq FPGA 应用而设计。此设计使用外部计时器将开关频率同步到 300 kHz。它还采用受控的加电和断电

2022-09-19 07:37:25

Abstract: This reference design explains how to power the Xilinx Zynq Extensible Processing

2012-08-23 17:19:43 36

36 硬件平台:ZedBoard 软件平台:vivado2013.3 本示例通过综合、实现,生成比特流,发送到SDK实现。 启动vivado并且创建一个项目 根据提示操作一步步创建新项目的时候记得选择

2017-02-07 20:42:29 432

432

Xilinx 的客户们分享了各种 Zynq SoC 的成功应用。这些成功案例详细描述了挑战、解决方案和所取得的成果。如欲了解其他 Xilinx 客户如何利用 Zynq SoC

2017-02-09 03:35:13 217

217 2014.4; 在官方网站下载微型嵌入式实时操作系统SmallRTOS的最新版,在压缩包中找到\Platform\SmallRTOS_Zynq_Vivado_v1.00a文件夹,该文件夹里面的文件即是官方提供的移植代码

2017-02-09 05:07:11 379

379

。该更新仅用来满足 UltraScale 器件用户的需求。 敬请查看版本说明,了解所有最新版本信息。 最大化地利用 Vivado Design Suite ! 立刻使用 Vivado Design

2017-02-09 09:06:11 295

295 Block Design 作为VIVADO的一大新神器,给用户设计带来了极大的方便,能够根据用户的定制需求自动选择、组合以及连接不同的IP。然而,其中不可控的Bug也给用户带来了一定的烦恼

2017-02-09 09:44:06 7802

7802

通过前面的PL DMA设计,在SDK中运行,很正常的没有运行起来(block design与source desing都是自己手敲,明显的错误已经改正,能够生成bit文件启动SDK调试)。 首先在

2017-11-28 15:46:26 6787

6787 Xilinx Zynq™-7000

2018-06-04 13:47:00 3392

3392 本文档的主要内容详细介绍的是MicroBlaze(Vivado版)设置说明详细资料免费下载开始IP综合设计(步骤)

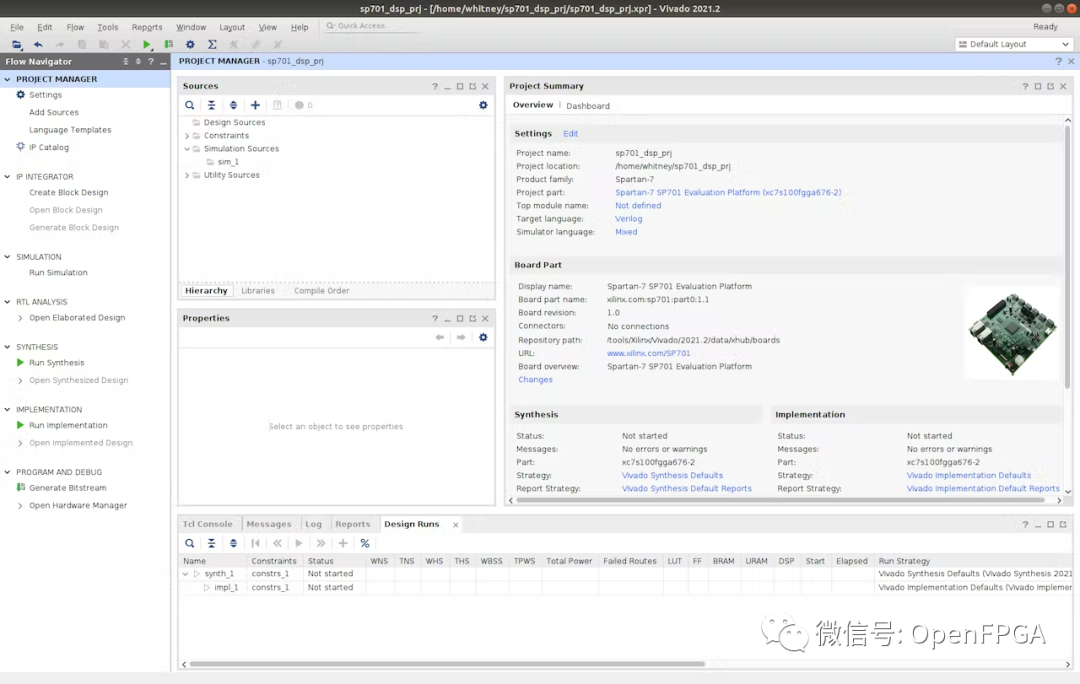

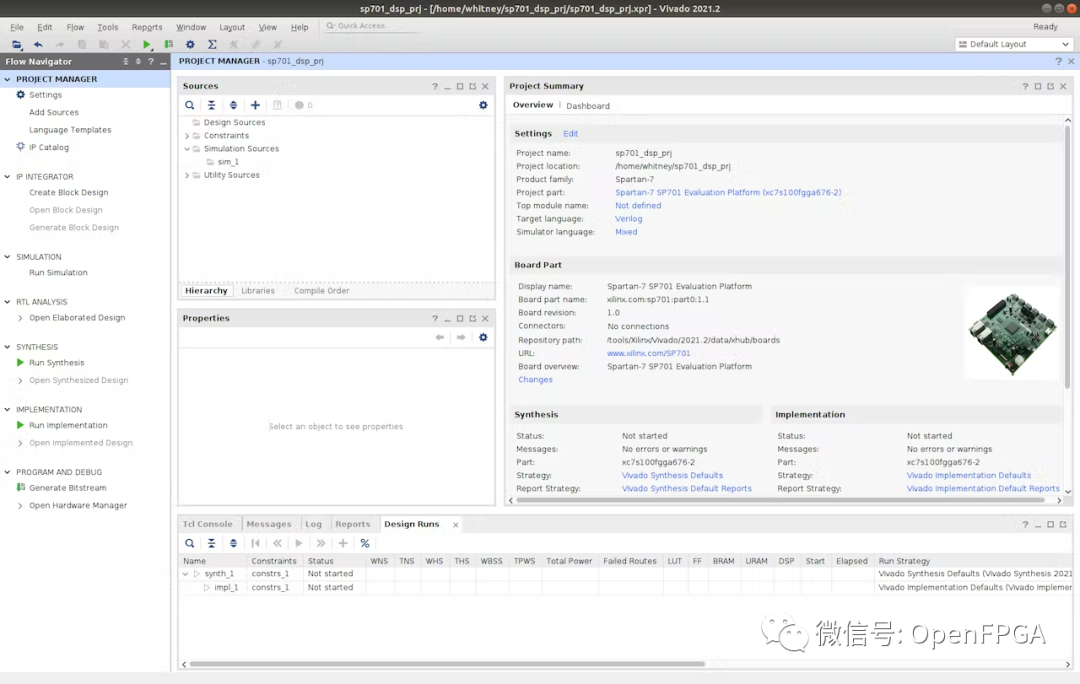

1、在工作流导向面板中的IP Integrator中,点击Create

2018-09-05 08:00:00 0

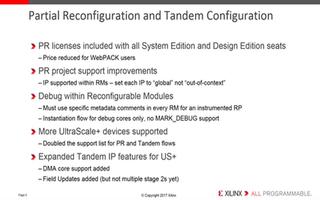

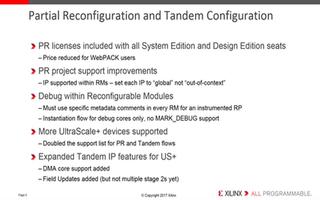

0 新的器件支持包括:Kintex®UltraScale+™,Zynq®UltraScale+ MPSoC和所有Vivado HLx版本的单核Zynq-7000S All Programmable SoC器件,包括WebPACK™,基于IEEE 17350的IP加密的公共访问支持。

2018-11-20 06:50:00 2594

2594 了解Vivado Design Suite 2016中的新功能。

我们将回顾新的UltraFast方法检查,HDL模块参考流程和用于IPI设计的SmartConnect IP,语言模板增强,Xilinx参数化宏(XPM),GUI改进

2018-11-20 06:22:00 2247

2247 此视频重点介绍了新的Vivado Design Suite 2017.1版本的增强功能,包括操作系统和设备支持,新外观,部分重新配置广泛可用性等等......

2018-11-30 06:20:00 2537

2537

Xilinx合作伙伴和客户展示了他们如何使用Zynq仿真平台。

2019-01-03 13:14:43 4329

4329 了解如何使用Vivado设计套件的电路板感知功能快速配置和实施针对Xilinx评估板的设计。

2018-11-26 06:03:00 3062

3062 了解Xilinx FSBL如何操作以启动Zynq器件。

包括程序执行概述,调试技巧以及有关特定引导设备的信息。

还包括FSBL角度的启动安全性简要概述。

2018-11-23 06:32:00 4237

4237 了解如何使用Xilinx SDK创建Zynq引导映像。

我们将在通过Xilinx SDK创建Zynq引导映像时查看可以选择/添加的引导参数和分区。

2018-11-23 06:24:00 3601

3601 在Vivado Design Suite中,Vivado综合能够合成多种类型的属性。在大多数情况下,这些属性具有相同的语法和相同的行为。

2019-05-02 10:13:00 3750

3750 Zynq-7000所有可编程SoC应用程序开发都从Zynq硬件平台开始。该硬件平台定义了如何配置ARM处理系统(PS),并为可编程逻辑(PL)提供实际的硬件设计。该硬件平台必须在vivado中配置

2019-02-13 17:49:46 21

21 Xilinx_Vivado_zynq7000入门笔记说明。

2021-04-08 11:48:02 70

70 Simulink或者System Generator,对此应该不会陌生,毕竟都是向设计中添加“Block”,故IPI设计的文件后缀为.bd。 这种方式最大的好处是直观,同时简化了互连操作

2021-11-09 09:43:17 3253

3253 电子发烧友网站提供《Xilinx Zynq上FreeRTOS的Tracealyzer.zip》资料免费下载

2022-12-07 14:59:27 3

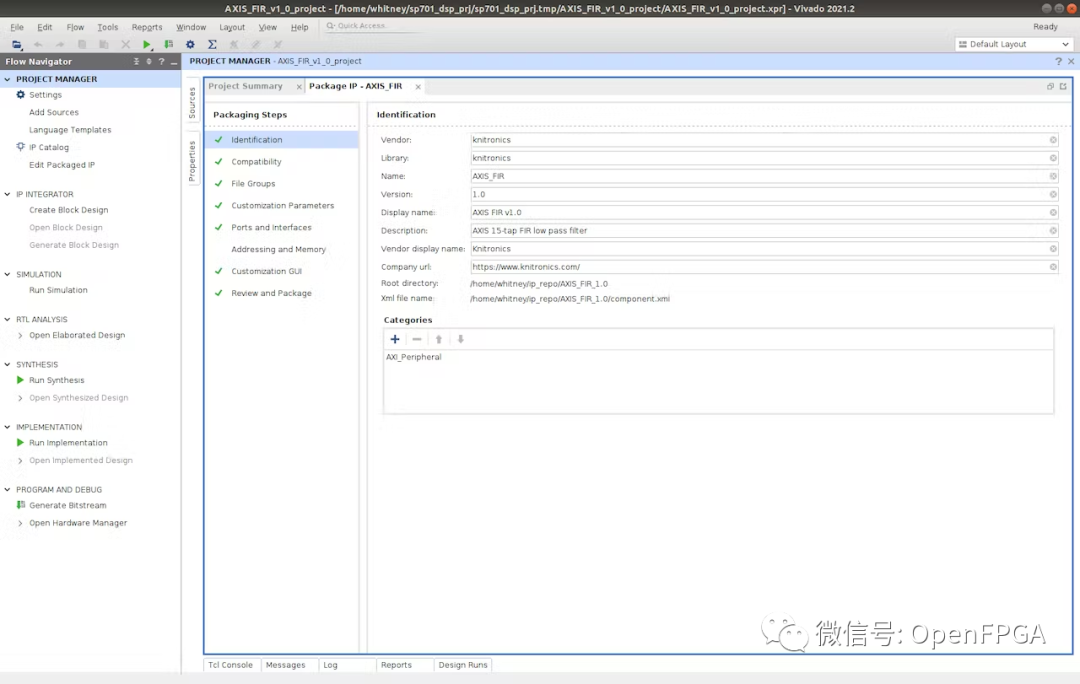

3 AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程。Vivado 中的block design是使用RTL IP形式

2023-02-10 14:50:57 747

747

AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程。Vivado 中的block design是使用RTL IP形式

2023-02-10 14:51:14 1581

1581

AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程。Vivado 中的block design是使用RTL IP形式

2023-02-10 14:51:19 735

735

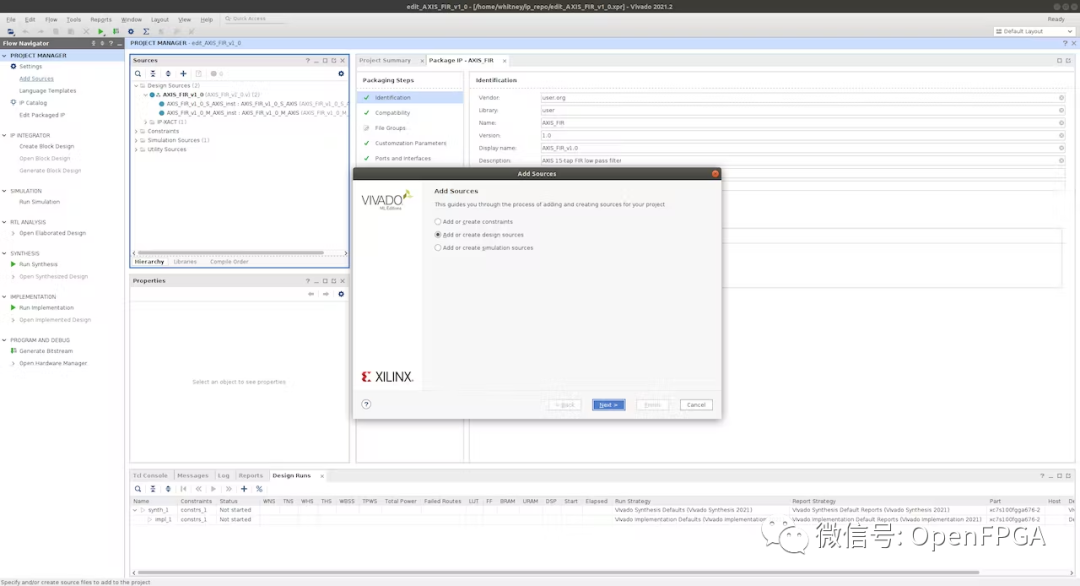

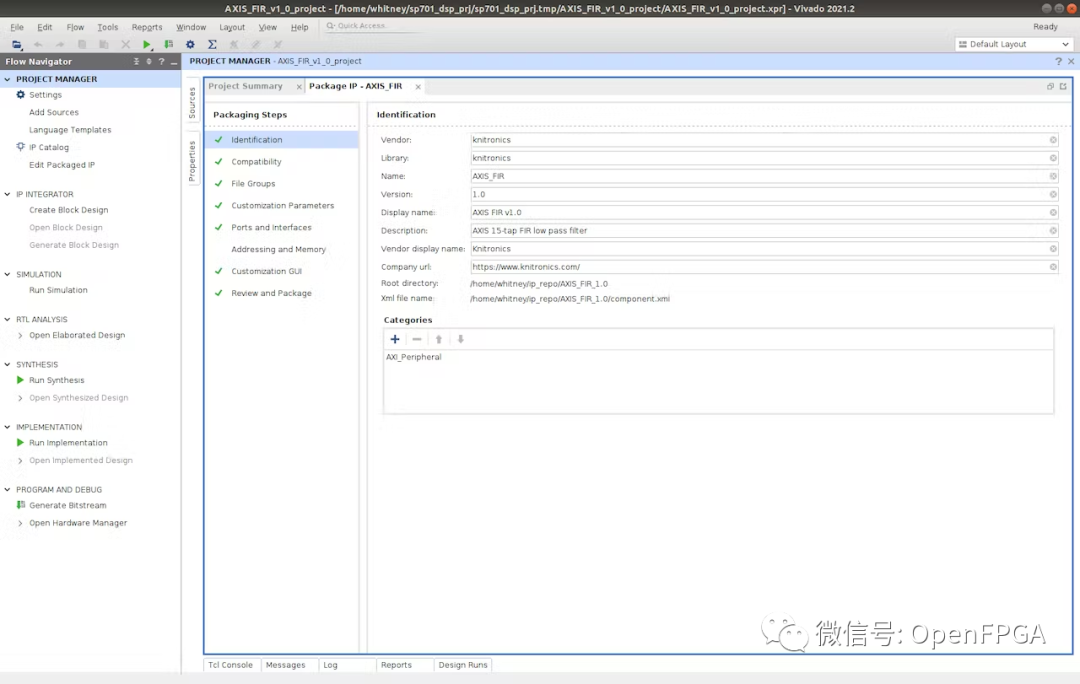

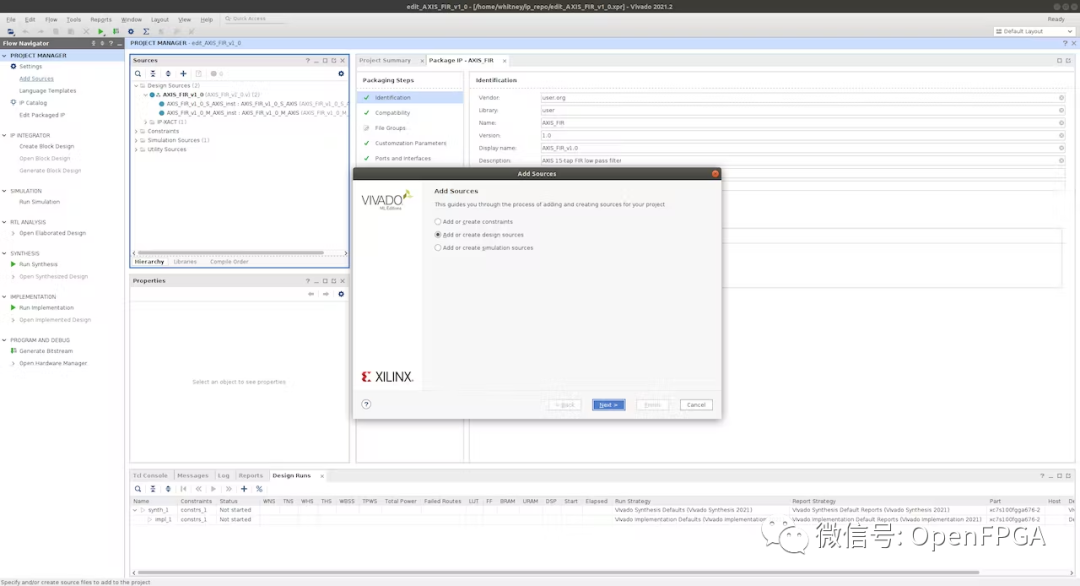

使用Vivado Block Design设计解决了项目继承性问题,但是还有个问题,不知道大家有没有遇到,就是新设计的自定义 RTL 文件无法快速的添加到Block Design中

2023-02-13 11:02:35 1963

1963 电子发烧友网站提供《为EBAZ4205创建Xilinx Vivado板文件.zip》资料免费下载

2023-06-16 11:41:02 1

1 本文介绍广州星嵌DSP C6657+Xilinx Zynq7035平台下Xilinx Zynq7035算力指标。

2023-07-07 14:15:01 682

682

电子发烧友网站提供《Vivado Design Suite用户指南:版本说明、安装和许可.pdf》资料免费下载

2023-09-13 09:16:38 0

0

电子发烧友App

电子发烧友App

评论