摘 要: 毛刺现象在FPGA 设计中非常普遍, 而毛刺的出现往往导致系统结果的错误。本文从FPGA 的原理结构的角度深入探讨了毛刺产生的原因及产生的条件, 总结了多种不同的解决方法, 并结合具体的应用对解决方案进行深入地分析。

FPGA (F ield P rogrammable Gate A rray) 以其容量大、功能强以及可靠性高等特点, 在现代数字通信系统中得到广泛的应用。采用FPGA 设计数字电路已经成为数字电路系统领域的主要设计方式之一[ 1 ]。在FPGA 的设计中, 毛刺现象是长期困扰电子设计工程师的设计问题之一, 是影响工程师设计效率和数字系统设计有效性和可靠性的主要因素。由于信号在FPGA 的内部走线和通过逻辑单元时造成的延迟, 在多路信号变化的瞬间, 组合逻辑的输出常常产生一些小的尖峰, 即毛刺信号, 这是由FPGA内部结构特性决定的。毛刺现象在FPGA 的设计中是不可避免的, 有时任何一点毛刺就可以导致系统出错, 尤其是对尖峰脉冲或脉冲边沿敏感的电路更是如此。因此, 克服和解决毛刺问题对现代数字系统设计尤为重要。本文从FPGA 的原理结构的角度探讨了产生毛刺的原因及产生的条件, 在此基础上, 总结了多种不同的消除方法, 在最后结合具体的应用对解决方案进行深入的分析。

1 毛刺产生的原因

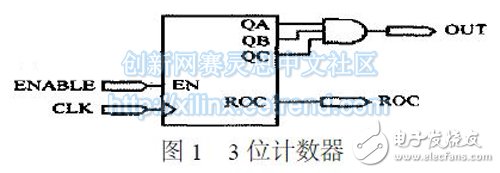

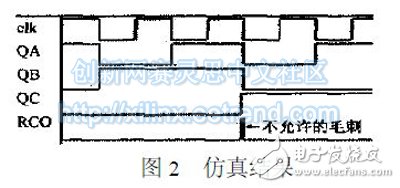

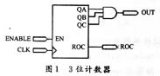

以图1 的例子分析毛刺产生的起因: 图1 是一个3 位同步加法计数器, 当使能端为高电平时, 在每个时钟上升沿时刻, QA , QB, QC 从000 逐步变到111, 进入到全1状态后, 进位输出端输出半个时钟脉冲宽度的高电平, 但从图2 仿真结果中可以看到在011 变化到100 时刻ROC出现了尖脉冲, 即毛刺。

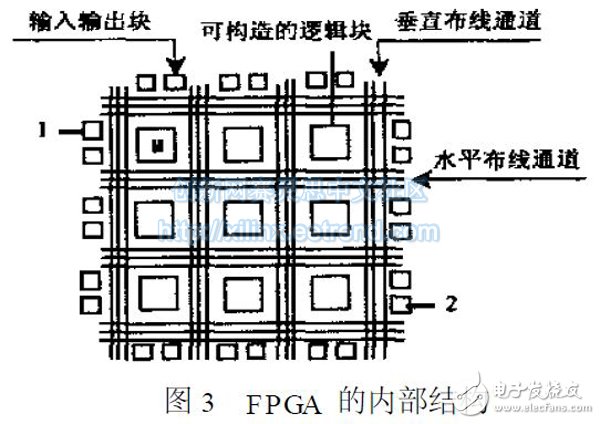

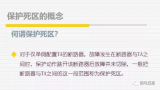

以Xilinx 的FPGA 为例分析其内部结构, 如图3 所示。

FPGA 芯片是由可构造的输入输出块( Input/ OutputBlock, IOB)、可构造逻辑块(Cinfigurable Logic Block, CLB ) 和可编程连线资源( Programmable Interconnect Array, PIA ) 3 种可构造单元构成的。IOB 位于芯片内部四周, 在内部逻辑阵列与外部芯片封装引脚之间提供一个可编程接口, 他主要由逻辑门、触发器和控制单元组成。CLB 组成了FPGA 的核心阵列, 能完成用户指定的逻辑功能; 每个CLB 主要有一个组合逻辑、几个触发器、若干个多选一电路和控制单元组成; PIA 位于芯片内部的逻辑块之间, 经编程后形成连线网络, 用于芯片内部逻辑间的相互连接, 并在他们之间传递信息。从图3 中可以看出,对于不同的输入1、2, 到逻辑块(M ) 的走线可能是不同的,这就造成了输入信号的延迟, 假设1、2 同时变化, 由于延迟的存在, 到达M 时就有先有后(这种现象称为竞争) , 在逻辑输出端就可能会有险象(也称冒险) , 即产生了毛刺。在上述例子中的011 状态, 假设QA 与QB 同时从1 变化到0, 而QC 提前了2 ns 从0 变到1 , 产生一个2 ns 的高电平,这就是毛刺。也就是说, 在FPGA 设计中, 毛刺产生的根本原因是信号在芯片内部走线时产生的延迟。

2 毛刺产生的条件

借助同样的例子来分析毛刺产生的条件。QA , QB,QC 在每一个时钟上升沿同时发生翻转, 但实际中由于延迟的存在, 并不能保证QA , QB, QC 到D 触发器的布线长短一致。如果QC 比QA , QB 提前了2 ns, 这就形成了2 ns 的全1 状态, 称为“假象全1”, 进而导致进位输出产生一个尖脉冲。值得注意的是, 在3 变到4 即011 到100时, 3 位中有2 位同时发生翻转, 即在同一时刻有大于一个的信号发生改变。由于延迟的作用, 多个信号到达终点的时间有先有后, 形成了竞争, 由竞争产生的错误输出就是毛刺。所以, 毛刺发生的条件就是在同一时刻有多个信号输入发生改变。

3 消除毛刺的方法

知道了毛刺产生的条件, 就可以通过改变设计, 破坏其条件来减少毛刺的发生。例如, 利用格雷码计数器每次输出只有一位跳变的特性, 代替普通的二进制计数器, 避免了毛刺的产生[ 3 ]。还可以对电路进行改进, 以消除毛刺对系统的影响。下面对各种方法做分别介绍:

3、1 利用冗余项法

利用冗余项消除毛刺有2 种方法: 代数法和卡诺图法, 两者都是通过增加冗余项来消除险象, 只是前者针对于函数表达式而后者针对于真值表。以卡诺图为例, 若两个卡诺圆相切, 其对应的电路就可能产生险象。因此, 修改卡诺图, 在卡诺图的两圆相切处增加一个圆, 以增加多余项来消除逻辑冒险。但该法对于计数器型产生的毛刺是无法消除的。

电子发烧友App

电子发烧友App

评论