FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低。目前许多终端市场对可编程逻辑器件设计的低功耗要求越来越苛刻。

2011-11-28 11:45:56 1117

1117 本文主要是Lattice公司市场总监Shakeel Peera给大家谈面对竞争激烈的FPGA市场,Lattice公司将持续优化FPGA成本和功耗。

2012-08-14 14:12:55 783

783

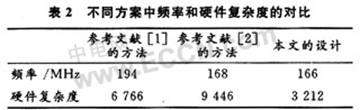

TypeC协议的UHF RFID标签基带处理器的的优化和实现。##降低功耗主要方法##RTL阶段手工加时钟门控##综合阶段工具插于集成门控单元##时钟树综合阶段优化功耗及结论

2014-03-24 14:36:30 3743

3743 的技巧。本文提出的方法用于架构设计和前段设计的初期,如功耗估计、低功耗架构优化和时钟门控等。##功耗的估算##功耗的优化##架构考虑及RAM的功耗优化##时钟树单元/连线##时序分析##测试结果

2014-03-25 09:58:50 14624

14624 以下是笔者一些关于FPGA功耗估计和如何进行低功耗设计的知识。##关于FPGA低功耗设计,可从两方面着手:1)算法优化;2)FPGA资源使用效率优化。

2014-12-17 09:27:28 9177

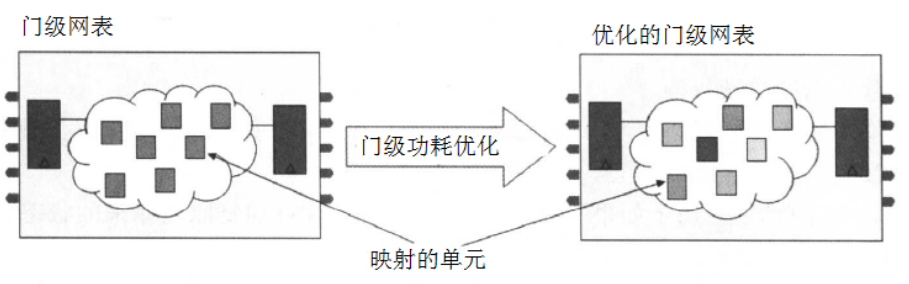

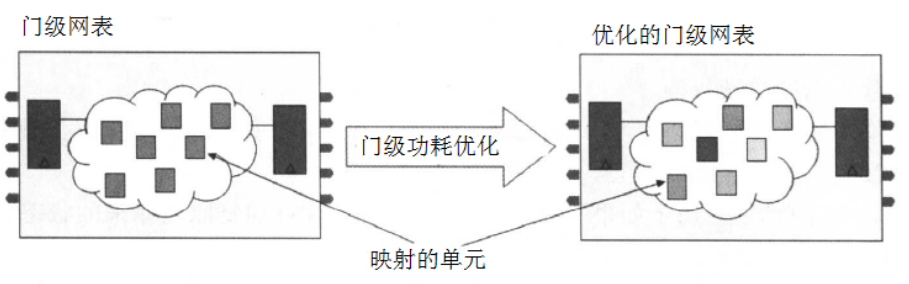

9177 门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化以满足功耗的约束,同时设计保持其性能,即满足设计规则和时序的要求。

2020-07-02 16:28:31 4945

4945

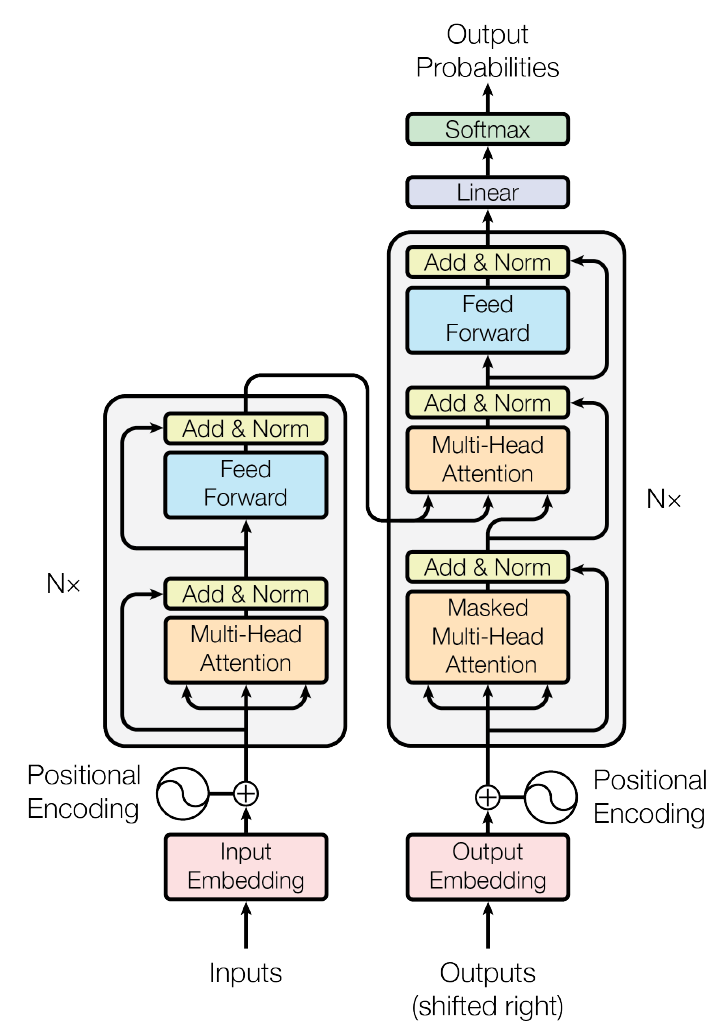

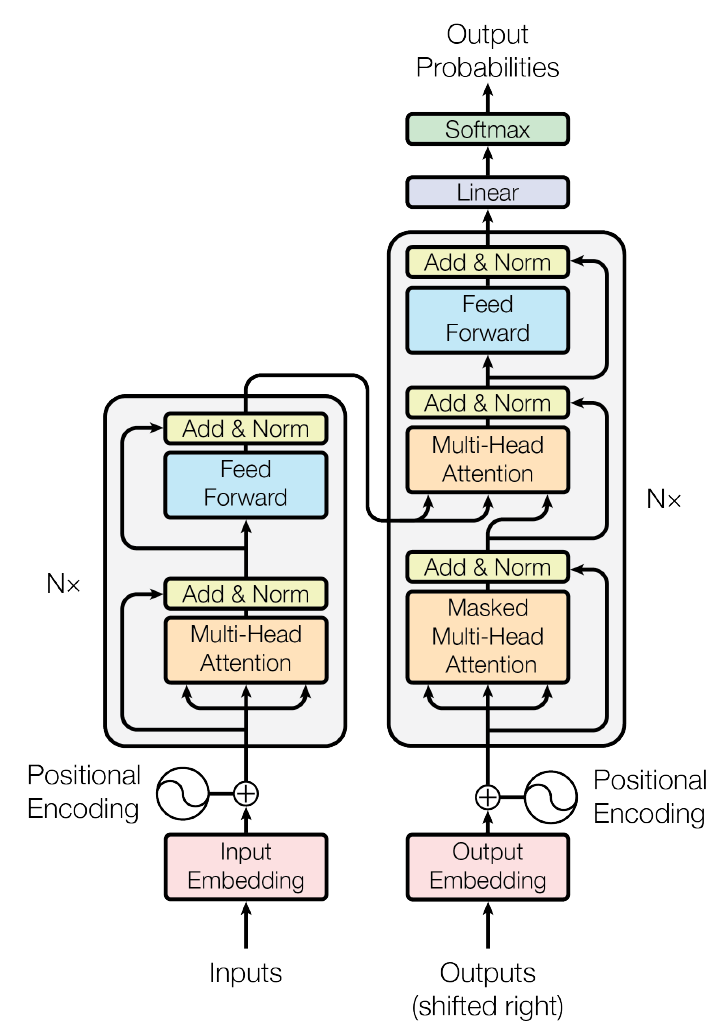

前言 AI芯片(这里只谈FPGA芯片用于神经网络加速)的优化主要有三个方面:算法优化,编译器优化以及硬件优化。算法优化减少的是神经网络的算力,它确定了神经网络部署实现效率的上限。编译器优化和硬件优化

2020-09-29 11:36:09 4383

4383

整个FPGA设计的总功耗由三部分功耗组成:1. 芯片静态功耗;2. 设计静态功耗;3. 设计动态功耗。

2022-11-24 20:46:41 1028

1028 从工艺选择到设计直至投产,设计人员关注的重点是以尽可能低的功耗获得最佳性能。Altera在功耗和性能上的不断创新,那其28nm高端FPGA如何实现功耗和性能的平衡?具体有何优势?

2013-05-17 10:26:11 2980

2980 FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能够做到如此低的功耗是因为什么?

2021-04-30 06:08:49

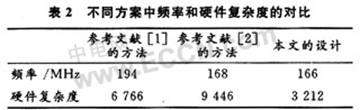

FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法介绍了利用现场可编程逻辑门阵列FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化方法。重点介绍了DDS技术在FPGA中的实现

2012-08-11 18:10:11

FPGA已经被广泛用于实现大规模的数字电路和系统,随着CMOS工艺发展到深亚微米,芯片的静态功耗已成为关键挑战之一。文章首先对FPGA的结构和静态功耗在FPGA中的分布进行了介绍。接下来提出了晶体管

2020-04-28 08:00:00

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本

2015-02-09 14:58:01

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-11-05 07:54:43

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-08-29 07:52:29

FPGA的时序优化高级研修班通知通过设立四大专题,帮助工程师更加深入理解FPGA时序,并掌握时序约束和优化的方法。1.FPGA静态时序分析2.FPGA异步电路处理方法3.FPGA时序约束方法4.FPGA时序优化方法

2013-03-27 15:20:27

的Enpirion的ED8101P0xQI单相数字控制器,可实现对FPGA的多种远程监视和低功耗特性。 5.提前规划电源树,整体布局优化系统功耗 系统硬件设计会影响设计的复杂程度、周期和成本,因此,尽早规划

2018-10-23 16:33:09

FPGA 设计优化主要分为编码风格、设计规划和时序收敛三大部分,这 些因素直接决定了 FPGA 设计的成败。 编码风格直接影响 FPGA 设计的实现并最终影响设计的性能。尽管综合 工具集成

2022-09-29 06:12:02

EDA技术具有什么特征?FPGA是什么原理?FPGA设计应用及优化策略基于VHDL的FPGA系统行为级设计

2021-04-15 06:33:58

消费电子领域,OEM希望采用FPGA的设计能够实现与ASIC相匹敌的低功耗。尽管基于90nm工艺的FPGA的功耗已低于先前的130nm产品,但它仍然是整个系统功耗的主要载体。此外,如今的终端产品设计大多

2019-07-15 08:16:56

`FPGA面积优化1.对于速度要求不是很高的情况下,我们可以把流水线设计成迭代的形式,从而重复利用FPGA功能相同的资源。2.对于控制逻辑小于共享逻辑时,控制逻辑资源可以用来复用,例如FIR滤波器

2014-12-04 13:52:40

Actel公司的ILGOO系列器件是低功耗FPGA产品,是在便携式产品设计中替代ASIC和CPLD的最佳方案。它在Flash*Freeze模式时的静态功耗最低可达到2µW,电池寿命是采用主流PLD

2020-05-13 08:00:00

无论从微观到宏观、从延长电池寿命到减少全球变暖的温室效应等等,各种不同因素都在迅速推动系统设计人员关注节能问题。一项有关设计优先考虑事项的最新调查指出,大部分工程师已把功耗排在首位,或者是将其紧跟在性能、密度和成本之后。在功耗方面,FPGA带来了独特的挑战。为什么要设计优化FPGA功耗?

2019-08-08 07:39:45

从Xilinx公司推出FPGA二十多年来,研发工作大大提高了FPGA的速度和面积效率,缩小了FPGA与ASIC之间的差距,使FPGA成为实现数字电路的优选平台。今天,功耗日益成为FPGA供应商及其

2019-09-20 06:33:32

本文阐述了Spartan-3 FPGA针对DSP而优化的特性,并通过实现示例分析了它们在性能和成本上的优势。

2019-10-18 07:11:35

芯片设计解决方案供应公司微捷码(Magma)设计自动化有限公司近日宣布,已和专为消费性应用提供超低功耗65纳米FPGA(现场可编程门阵列)技术的先驱者SiliconBlue科技公司正式签定技术合作

2019-07-26 07:29:40

你想不想知道在应用中如何实现低功耗Wi-Fi®?我们的SimpleLink™ Wi-Fi 器件系列提供易于使用且高效的方法来优化应用功耗,从而实现更长的产品使用寿命。请继续往下读,看看我们是如何实现

2018-09-04 14:48:22

对基于数字信号处理器(DSP)的系统而言,优化功耗是一项重要但往往难以实现的设计目标。现在,基于DSP的设备常常把以往各自独立的多个应用结合起来,每一个应用都可能有多个工作模式。要得到这样一个设备

2019-08-30 07:24:15

如何使用优化的数据包软件降低网络功耗?

2021-05-25 06:45:33

从工艺选择到设计直至投产,设计人员关注的重点是以尽可能低的功耗获得最佳性能。Altera在功耗和性能上的不断创新,那其28nm高端FPGA如何实现功耗和性能的平衡?具体有何优势?

2019-09-17 08:18:19

复杂器件专业技术相结合,将为系统供应商提供低功耗的芯片方案,供他们在此基础上持续提高带宽容量,并完成更智能的处理。此外,TPACK提供的芯片解决方案可以导入到最新的FPGA中,进一步降低功耗。最终实现

2019-07-31 07:13:26

如何利用Freeze技术的FPGA实现低功耗设计?

2021-04-29 06:27:52

如何才能实现降低FPGA设计的功耗?

2021-04-29 06:47:38

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-08-15 08:28:42

对基于数字信号处理器(DSP)的系统而言,优化功耗是一项重要但往往难以实现的设计目标。现在,基于DSP的设备常常把以往各自独立的多个应用结合起来,每一个应用都可能有多个工作模式。要得到这样一个设备

2019-06-24 06:05:32

常用的软件功耗优化方法有哪几种类型μC/OS-II的源码级功耗怎么优化?

2021-04-28 06:49:44

对基于数字信号处理器(DSP)的系统而言,优化功耗是一项重要但往往难以实现的设计目标。现在,基于DSP的设备常常把以往各自独立的多个应用结合起来,每一个应用都可能有多个工作模式。要得到这样一个

2019-10-08 13:59:36

怎么实现基于LFSR优化的BIST低功耗设计?

2021-05-13 06:21:01

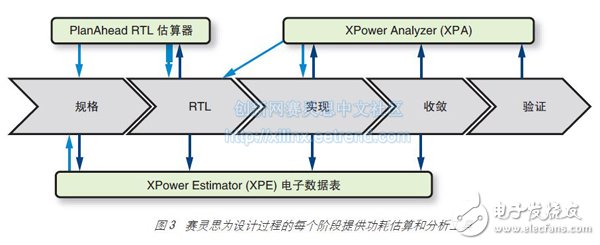

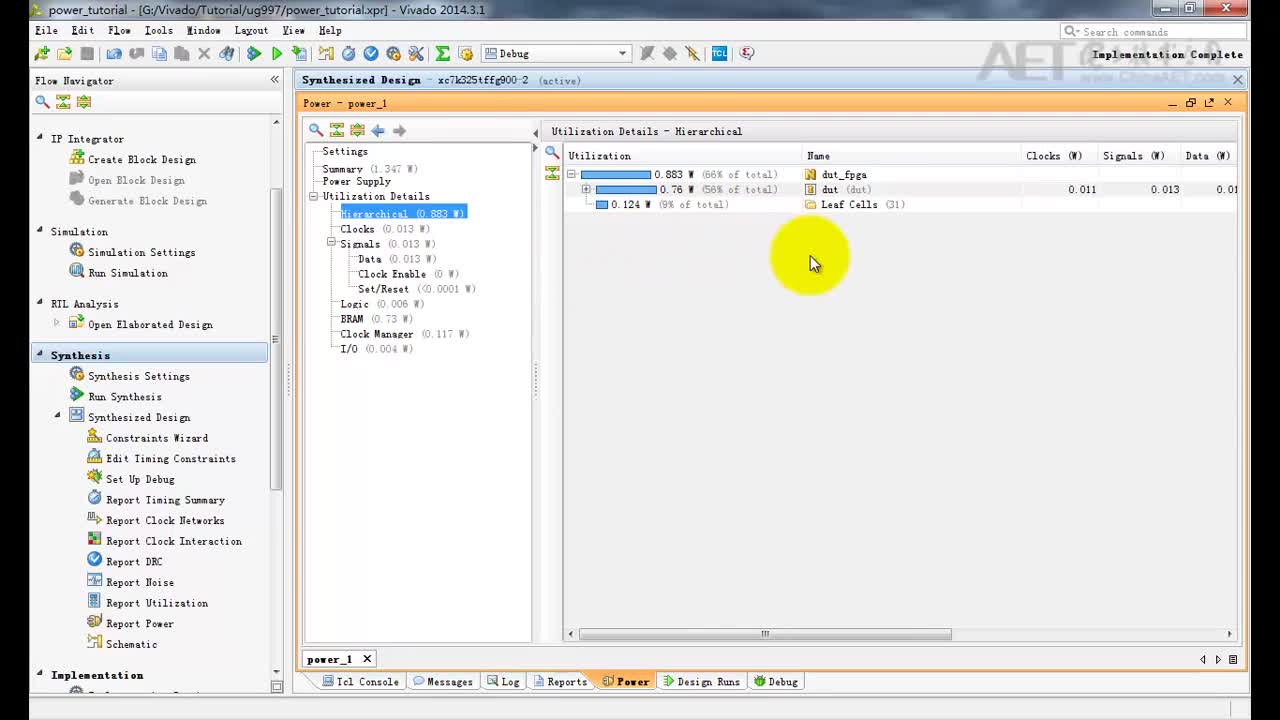

的功耗分析工具进行精确计算功耗。打开综合实现后的设计,点击report power即可得到功耗分析的结果,如图3,4所示。图3图43.低功耗设计关于FPGA低功耗设计,可从两方面着手:1). 算法优化

2014-08-21 15:31:23

ADuCM360/1是针对低功耗的应用,能否详细介绍一下在实际设计时如何进行功耗优化?

2019-03-11 15:41:39

本帖最后由 曾12345 于 2018-5-23 15:49 编辑

全新的毫瓦级功耗FPGA解决方案为机器学习推理在大众市场物联网应用中实现快速部署创造机遇。1. 将AI加速部署到快速增长

2018-05-23 15:31:04

FPGA怎么选择?针对功耗和I/O而优化的FPGA介绍

2021-05-06 09:20:34

(1)门级电路的功耗优化综述 门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化以满足功耗的约束,同时

2021-11-12 06:14:26

设计技巧为什么能够节省功耗?降低FPGA功耗的设计技巧有哪些?

2021-04-30 06:04:19

主要讲解了fpga设计、方法和实现。这本书略去了不太必要的理论、推测未来的技术、过时工艺的细节,用简明、扼要的方式描述fpga中的关键技术。主要内容包括:设计速度高、体积小、功耗低的体系结构方法

2012-03-01 14:59:23

高级FPGA设计、结构、实现与优化(Advanced FPGA Design Architecture, Implementation,and Optimization)

2013-12-10 14:16:25

一种FPGA时钟网络中锁相环的实现方案:摘 要:本文阐述了用于FPGA 的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探

2009-08-08 09:07:22 25

25 微捷码与SiliconBlue合作为超低功耗FPGA技术进行优化

芯片设计解决方案供应公司微捷码(Magma)设计自动化有限公司近日宣布,已和专为消费性应用提供超低功耗65纳米FPGA(现

2008-12-01 08:03:41 606

606 具有低功耗意识的FPGA设计方法

ILGOO系列低功耗FPGA产品

Actel公司的ILGOO系列器件是低功耗FPGA产品,是在便携式产品设计中替代ASIC和CPLD的最

2009-11-26 09:41:19 676

676

AES算法中S-box和列混合单元的优化及FPGA技术实现

由于其较高的保密级别,AES算法被用来替代DES和3-DES,以适应更为严苛的数

2010-04-23 09:34:22 2692

2692

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标

2010-07-01 11:08:43 465

465 本文将介绍FPGA的功耗、流行的低功耗功能件以及影响功耗的用户选择方案,并探讨近期的低功耗研究,以洞察高功率效率FPGA的未来趋势。

功耗的组成部分

2010-08-27 10:57:21 1637

1637

自从Xilinx推出FPGA二十多年来,研发工作大大提高了FPGA的速度和面积效率,缩小了FPGA与ASIC之间的差距,使FPGA成为实现数字电路的优选平台。今天,功耗日益成为FPGA供应商及其客户关注的问题。降低FPGA功耗是缩减封装和散热成本、提高器件可靠性以及打开移

2011-03-15 14:58:34 31

31 功耗意识的设计越来越重要。将业界领先的低功耗FPGA与创新的功耗优化工具相结合,能够大幅降低在芯片和系统层面的功耗

2011-04-15 15:52:40 0

0 高级FPGA设计结构、实现和优化 作者:(美)克里兹著,孟宪元译;出版社:机械工程出版社 学FPGA不一定需要开发板,自己学会modelsim仿真、写testbench,用PC机仿真就能有不少长进。这

2012-11-28 14:03:22 0

0 白皮书 :采用低成本FPGA实现高效的低功耗PCIe接口 了解一个基于DDR3存储器控制器的真实PCI Express (PCIe) Gen1x4参考设计演示高效的Cyclone V FPGA怎样降低系统总成本,同时实现性能和功耗

2013-02-26 10:04:25 72

72 基于FPGA的SM3算法优化设计与实现的论文

2015-10-29 17:16:51 4

4 DSP功耗与优化,有需要的可以下来看看。

2016-01-15 17:42:22 4

4 SVPWM算法优化及其FPGA_CPLD实现

2016-04-13 15:42:35 18

18 高级FPGA设计 结构、实现和优化,适合于FPGA的进阶学习。

2016-05-11 16:40:55 15

15 高级FPGA设计 结构、实现和优化,适合于学习FPGA的进阶学习。

2016-05-11 16:40:55 14

14 利用FPGA实现信号处理算法是一个难度颇高的应用,不仅涉及到对信号处理算法、FPGA芯片和开发工具的学习,还意味着要改变传统利用软件在DSP上实现算法的习惯,从面向硬件实现的算法设计、硬件实现、结构优化和算法验证等多个方面进行深入学习。

2016-12-26 17:26:41 12

12 基于FPGA的可堆叠存储阵列设计与优化

2017-01-07 21:28:58 0

0 参加 FPGA 功率优化班,将帮助您创建更高电源效率的 FPGA 设计。通过本课程的学习,将有助于您的设计满足更小型化的 FPGA 器件,降低 FPGA 功耗,或在更低的温度下运行

2017-02-09 06:24:11 167

167 资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。Xilinx新一代开发工具Vivado针对功耗方面有一套完备的方法和策略,本文将介绍如何利用Vivado进行功耗分析和优化。

2017-11-18 03:11:50 4873

4873 现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 2951

2951 设计者通过优化自己的设计和注意某些具体情况,可以在FPGA设计中实现低功耗。通过一款具体的FPGA产品了解其低功耗的解决方式,为设计提供了指导。FPGA均可在相应的操作环境下进行仿真,从而了解功耗

2017-11-23 10:37:23 1248

1248 本文首先与实测系统功耗进行对比,验证了Xilinx公司ISE软件包中FPGA功耗估算工具XPower的准确性。然后对FPGA设计中影响系统功耗的几个相互关联的参数进行取样,通过软件估算不同样点下的系统功耗,找到功耗最低的取样点,得到最佳设计参数,从而达到优化系统设计的目的。

2017-11-25 09:26:44 1551

1551 估计得到为20w左右,有点过高了,功耗过高则会造成发热量增大,温度高最常见的问题就是系统重启,另外对FPGA内部的时序也不利,导致可靠性下降。其它硬件电路的功耗是固定的,只有FPGA的功耗有优化的余地,因此硬件团队则极力要求笔者所在的FPGA团队尽量多做些低功

2018-09-07 14:58:01 381

381 高层次的设计可以让设计以更简洁的方法捕捉,从而让错误更少,调试更轻松。然而,这种方法最受诟病的是对性能的牺牲。在复杂的 FPGA 设计上实现高性能,往往需要手动优化 RTL 代码,这也意味着

2018-12-16 11:19:28 1435

1435

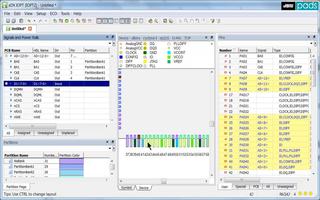

与 FPGA 软件工具进行自动双向信息交换可提供由供应商规则驱动的“设计即正确”的 I/O 分配,从而实现快速、无误的优化流程。其包括了最新的器件支持,并且可提前访问尚未发布的 FPGA 供应商器件。

2019-05-16 06:13:00 3380

3380

应用能够有更高的性能,您需要熟悉如下介绍的硬件。另外,将会介绍编译优化选项,有助于将您的 OpenCL 应用更好的实现 RTL 的转换和映射,并部署到 FPGA 上执行。

2020-07-16 17:58:28 6015

6015

的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低。目前许多终端市场对可编程逻辑器件设计的低功耗要求越来越苛刻。在消费电子领域,OEM希望采用FPGA的设计能够实现与ASIC相匹敌的低功耗。 尽管基于90nm工艺的FPGA的功耗已低

2020-10-28 15:02:13 2498

2498 的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低。目前许多终端市场对可编程逻辑器件设计的低功耗要求越来越苛刻。在消费电子领域,OEM希望采用FPGA的设计能够实现与ASIC相匹敌的低功耗。 尽管基于90nm工艺的FPGA的功耗已低

2020-10-26 18:51:16 2583

2583 本文档的主要内容详细介绍的是如何使用Xilinx的FPGA对高速PCB信号实现优化设计。

2021-01-13 17:00:59 25

25 功耗是我们关注的设计焦点之一,优秀的器件设计往往具备低功耗特点。在前两篇文章中,小编对基于Freez技术的低功耗设计以及FPGA低功耗设计有所介绍。为增进大家对低功耗的了解,以及方便大家更好的实现低功耗设计,本文将对FPGA具备的功耗加以详细阐述。如果你对低功耗具有兴趣,不妨继续往下阅读哦。

2021-02-14 17:50:00 6072

6072 在选取较优化的指纹识别预处理算法的基础上,根据算法的结构选取具有并行处理、低功耗、速度快等特点的FPGA作为实现算法的基本器件。由于用FPGA实现复杂算法较传统器件从思考角度和实现方向上都有很大区别,所以本次设计从新的方向来完成传统的指纹处理的设计。实际结果表明FPGA基本达到了设计的最初要求。

2021-02-03 15:53:00 11

11 (1)门级电路的功耗优化综述 门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化以满足功耗的约束,同时

2021-11-07 11:05:59 19

19 对于FPGA来说,设计人员可以充分利用其可编程能力以及相关的工具来准确估算功耗,然后再通过优化技术来使FPGA和相应的硬件设计满足其功耗方面的要求。

2022-12-29 14:46:14 928

928 与现有的中端FPGA相比,得益于专为低功耗设计的可编程结构、功耗优化的嵌入式存储器和DSP、低功耗高性能SERDES与I/O设计、内置协议逻辑等全方位优化措施,Avant系列产品的功耗比同类竞品器件低2.5倍。

2023-01-04 11:32:11 342

342 点击上方 蓝字 关注我们 FPGA 高级设计之实现功耗优化 与ASICs(Application Specific Integrated Circuits)比较,相似的逻辑功能,用FPGA来实现

2023-05-19 13:50:02 815

815 本文介绍用于在低功耗信号链应用中实现优化能效比的精密低功耗信号链解决方案和技术。

2023-07-08 11:13:04 368

368

正在加载...

电子发烧友App

电子发烧友App

评论