自电子交易问世以来,对速度的追逐无止境,时刻要求搭建速度最快、最智能的交易平台。智能和高速就意味着金钱。能够率先发现交易机会并在其上完成交易的交易平台将占上风。响应时间已经从“秒”一路降低到“毫秒”、“微秒”。要实现微秒和亚微秒响应时间,凭借传统的软件架构或简单的硬件架构几无可能,正是这一事实促使在超低时延系统中引入 FPGA 技术。但是,FPGA 编程要求使用 HDL机器语言开发交易策略并将现有交易策略(主要用 C 语言和 C++ 语言编写)移植到 HDL 机器语言中。这与使用标准的 C 和 C++ 编程在技能上有根本的不同,同时需要增加人员、工具和时间。

有现成的 C-to-HDL 编辑器工具可用,可将现有的 C 代码移植到硬件描述语言 (HDL),比用 HDL 从头开发代码速度快。但是,负责移植代码工作的人员必须熟悉硬件编程,或者必须遵循具体指南,才能生成可接受的代码。即便这样,生成的代码仍然可能会比用 HDL 直接开发的代码晦涩低效。

为了降低在 FPGA 以太网卡上直接开发 HDL 代码所带来的风险,同时节省开发时间,AdvancedIO 公司率先尝试将 FPGA 框架用于 10G 以太网 (10GE) 通信。我们的expressXG 开发框架工具套件为保证金融业务的快速部署提供了必要的基础设施, 可无缝移植到最新一代FPGA 卡上。该工具套件可集成并优化应用开发所需的所有必要的核心功能,能够最大程度地降低第三方许可成本,让开发周期缩短数月。开发团队可随后将 C-to-HDL 编译器工具集成在框架中,从而为开发应用的不同部分提供多重选择。

实际上两种方法都在项目中有一席之地。在优先考虑效率和代码紧凑度,或组件在多个项目中使用的情况下,最好使用 expressXG 框架直接开发 HDL 组件。如果着重考虑产品上市时间和定制化,或者要求以 C 语言编写代码的情况下,最好使用 C-to-HDL编译器。这种方法可以克服众多金融从业人员对 FPGA 的畏惧,同时不会影响性能。

算法交易概览

说到证券、衍生品、期货及其它金融工具的交易,总会让人联想起塞满几百人,叫嚷声此起彼伏的交易大厅。人们或漫无目的地转悠,或紧盯计算机屏幕。现实是,当今美国有 70% 以上的交易是由运行在计算机服务器上的算法完成的。在金融业,速度就是一切。哪家公司能够率先发现机遇并把握机遇,就能够赢得丰厚的利润。对某些交易策略而言,率先进入队列就能赢得交易。这也就毫不奇怪众多公司竭尽所能地确保自身相对竞争对手的优势,哪怕是仅仅 1 微秒。

在算法交易系统 (ATS) 中,由运行在高性能计算机上的算法处理交易,制定决策。这种系统运用多种技术来最大程度的降低时延,赢得竞争优势。具体包括与各个交易所共址、使用最短路径网络,以及使用 10G E 来降低时延这一日益风靡的做法。为在竞争中赢得优势,主要的交易公司同时采用上述所有技术。

证券市场上的交易仅限于经纪人-交易员和属于交易所成员的市场庄家机构之间。部分这类机构为其他交易公司提供服务,使他们能够通过他们的帐户使用“电子式专属线路下单(DMA)”给交易所下订单。提供“电子式专属线路下单”的机构必须建立交易前风险控制制度,以限制财务风险,满足合规性要求。因此,他们必须采用配备有软件的服务器,检查所有经手他们的账户的交易。这种检查必须以线速进行,因为任何延迟都会让他们及其客户处于不利境地。现有的基于软件的交易前风险管理平台需要数十微秒才能完成金融交易上要求的策略检查。很明显这对当今的交易员来说速度不能满足要求。

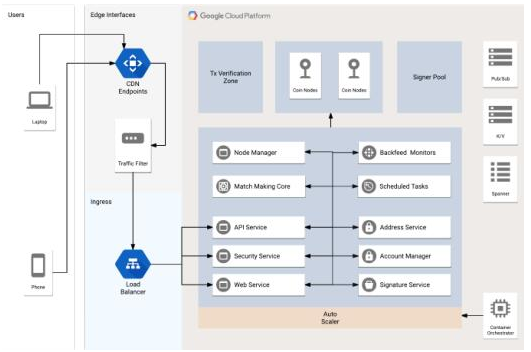

图 1 显示了简化交易系统的各个组件。实际上,ATS 可以更多的组件,比如用于执行更复杂算法的服务器或计算云,这里我们不作讨论。交易系统可以直接连接到交易所,也可以通过一个或多个交易所接口服务器、电子通信网络或其它方式连接到交易所。另外,对稳健可靠的交易基础设施而言,防火墙和入侵检测系统也是关键的组件。

基于软件的解决方案的局限性

ATS 必须能够接收多种市场馈入,解码使用的不同协议(如 FIXFAST、ITCH 和 OUCH 等多种名字各异的协议),过滤需要的交易代码并将其发送到预定义的“篮子”中,供交易算法 (TA) 分析。一旦交易算法判定必须执行某项交易, 就向订单管理系统(OMS) 发出交易请求,由订单管理系统与交易所接口服务器或交易所本身通信,下订单、接收交易确认。ATS服务器还能用极其精确的时戳给输入的数据加戳,然后将数据送去存档。加盖时戳和市场数据采集既可在同一服务器(让数据经内部网络进入数据服务器)完成,也可两个独立的服务器上执行。

ATS 能够以超过 6Gbps 的总突发数据速率从多个交易所接收数据。近期纳斯达克 (Nasdaq) 宣称已准备为自己的数据中心客户提供 40Gbps 的连接,正等待监管部门的批准。数据速率的快速攀升给系统处理器带来了巨大压力,同时也从重要的交易数据分析和决策任务上分散了处理能力。根据使用商用 10GE 网络接口卡对文件服务器测试的结果可以看出,在通过服务器自身的本地堆栈进行 TCP 传输时,仅处理 IP 协议就几乎完全占用了2.2GHz 的处理器,且实现的数据速率不足 5Gbps。为应对这种困局,出现了一种使用一个称为 TCP 卸载引擎(TOE) 的硬件为网络协议栈提速的方法。该方法能在一定程度上改善响应时间。

即便在网卡上采用了 TOE,到达主处理器的数据量仍然相当庞大,足以导致不可接受的延迟。为降低时延,有必要先在网卡上过滤相关数据,然后再传输给主系统处理器。虽然所有的工作负荷都在 FPGA 层面完成,但响应时间明显加快。另外 FPGA 可提供与负荷水平无关的相同响应时间。这对常规的处理器是无法实现的。在处理器轻载时,响应时间可以预测,但在重载时,响应时间会延长,直至无法预测。

目前处理器和以太网卡之间通过PCI Express® 总线来通信。理论上 8信道的 PCI Express Gen 2 总线能提供4Gbps 的峰值吞吐量。但 PCI Express受器件驱动程序和操作系统中断处理内在的时延的牵制。避免通过 PCI Express 总线与主机处理器相连,在网卡上执行金融计算,有着明显优势。

FPGA 技术是金融应用的理想选择,因为它能够实时处理海量数据,且时延低、一致性好。简言之,FPGA 能够提供并行处理能力,这是通用处理器无法匹敌的。由于 FPGA 能够给交易系统带来更强劲的性能和极快的速度,设计人员都在努力将尽可能多的功能(比如与交易所通信的 OMS 和部分算法)集成到 FPGA 中,以降低响应时间。图 2 对基于 FPGA 和 CPU 的系统的响应时间进行了比较。FPGA 不仅速度明显提高,而且性能随负荷的增加保持稳定,相比之下基于 CPU 的解决方案响应时间随负荷增大明显延长。

FPGA 技术的优势

FPGA 技术能够提供最佳解决方案,轻松应对高带宽、实时、高计算强度金融交易应用所面临的各种难题,这是其他技术无法匹敌的。由 FPGA 在以太网卡上执行交易的解决方案具有多重优势:

在贴近网络物理接口的 FPGA 上执行交易可避免主机总线、主机处理器和操作系统带来的时延。这样可以显著改善交易的响应时间。

FPGA 提供线速性能,能够瞬时执行算法中用于发现并把握交易机会的部分,不给他人察觉机遇的机会。

FPGA 在运行过程中可重新编程,便于修改参数、更新算法,保持领先于竞争对手。

FPGA 特别擅长并行处理,能够同时执行多个交易。

超低时延金融应用难以实现的原因在于它们必须在极高带宽下以线速运行,必须执行复杂的算法。要实现卓越的高性能,必须针对应用设计专门的架构。这就必须考虑如何在高计算强度的算法和满足交易的极快响应速度要求之间进行取舍,实现最佳平衡。设计人员必须想尽一切办法消除瓶颈,最大限度地降低通信时延和处理时延。为避免与主机系统总线有关的时延,应选用功能强大的 FPGA 来实现交易算法的关键部分,同时匹配大量的 SRAM 和 SDRAM 存储器端口和低时延通信端口。

与为单核或多核处理器开发软件相比, 使用线程的硬件模块编程FPGA 一般情况下工作量更大,而且要求具备专业技能。另外,还需要投入大量精力和资金学习实现 FPGA 解决方案的有案可循和无案可循的微妙之处,尤其对极高速解决方案而言更是如此。这些特点可能会增大 FPGA的认知风险,延长设计时间,导致部分项目经理和开发团队趋利避害,转而寻求次优的软件实现方案。另外现有的交易算法几乎都是清一色用 C 和C++ 编写,将它们移植到 HDL 代码中不是一件能一蹴而就的小事。

目前已有多种简化 FPGA 编程工作的方法,比如嵌入式硬核、软件内核和将 C 代码移植到 HDL 语言中的各种工具等。虽然每种方法都有自己定位,存在一定的性能缺陷,但每种方案都能加快应用的部署。C-to-HDL工具已成为简化 FPGA 应用开发的明确选择。但是这些工具生成的代码相当晦涩,难以优化。简言之,在目前没有什么能够取代直接 HDL 编程。

直接 HDL 编程与 C-TO-HDL 工具的对比

乔治华盛顿大学开展了一项研究[1,2],对高性能可重配置计算机中用于为FPGA 生成 HDL 代码的高级语言(HLL) 工具进行了评估,并制定了相应标准用于衡量各种工具相对于直接HDL 编程的效率和生产率。研究人员选择了四种工作负荷,并邀请拥有不同经验水平的用户使用各种工具来实现代码。结果显示,各种 HLL-to-HDL工具无一例外地缩短了开发时间,其中有的工具使开发时间缩短了高达61%。但结果也显示得到的代码无一例外地比直接用 HDL 开发的代码低效,占用面积增加了 36% 之多,频率下降达 50%。另外研究还发现在使用部分工具时,吞吐量显著下降。[2]而且这些工具生成的代码相当晦涩,难以进行 HDL 层面的调试。

不过这里应该说明的是测试中使用的四种设计相对简单。某些金融算法和应用要复杂得多,用 HDL 直接编程方法来实现也更艰难。我们预计随着更复杂的算法用 FPGA 来实现,使用 HLL-to-HDL 工具应该能够进一步节省时间。已有现成的 C 语言算法,需要移植到 HDL 中的情况尤为如此,但需要先在 C 语言中编写,然后移植的情况却并非如此。

需要注意的是,C 语言和 HDL 有着根本性的差异,不是用 C 语言编写的一切内容都能够正确无误地转换为HDL。表1 所示的是厂商目前使用的几种 C 语言变体或子集,现在正在尝试在OpenGL 上实现标准化。OpenGL 是一种用于新型处理器跨平台并行编程的开放标准,目前已在 FPGA 上使用。[3]

用 HDL 编写的 FPGA 开发框架

另一种简化 FPGA 开发工作并缩短开发周期的方法是使用用 HDL 直接编写的、对时延和性能进行了高度优化的框架(如图 3 和图 4 所示)。这种框架是以太网协议与接口、存储器控制器以及主机架构接口的深度抽象,故能减少实际人员为实现定制算法付出的精力和时间。这样开发人员能够集中精力进行应用开发和集成,不必担心如何让各种外部接口在 FPGA 卡上工作。合适的开发框架应保证应用在 FPGA 器件系列直接的可移植性以及在同一系列FPGA 卡之间的可移植性。这样可以显著降低未来移植或升级的成本。

我们已在 AdvancedIO Systems 公司提供的各系列高性能 10GE 卡上实现并验证了我们的开发框架。这些 10GE卡广泛用于国防、金融和电信行业等多种市场应用领域。

V5022 卡是专为金融交易优化的产品, 采用赛灵思 Virtex®-6 HXTFPGA,拥有能够实现大容量、超低时延交易解决方案的应用架构所需的全部必要组件。Virtex-6 HXT 系列可为实现复杂算法提供大量逻辑资源。它拥有 2个高达 8GB 的独立 Bank、533MHz DDR3 SDRAM 和 4 个高达144Mb 的独立 Bank、350MHz QDRII+SRAM,是需要缓冲或超高速查找表的高级算法的理想选择。V5022 卡有四个 10GE端口,能够大幅降低从光缆到 FPGA 器件内部的 MAC 接口(L2)的时延。

V5022 支持 PCI Express Gen2 主机接口,采用卡间高速端口确保系统中各卡之间的超高速通信,无需使用主机系统总线,可进一步降低时延。这为实现更加复杂的交易算法提供了更强大的高速处理能力。

该开发框架提供的主要功能必须集成在开发板上,才能保障一切工作正常。说采集、集成和优化这样的功能的逻辑是一件既费时又费钱的工作,应该不算过分。因此这种开发框架为项目经理带来了巨大的价值,有助于加速产品上市进程。

AdvancedIP 投入了大量的精力,以确保其框架经优化后能够提供最优异的性能,空间占用小,运行效率高。这样可以让 FPGA 的大部分资源用于应用开发。比如,当 V5022 使用赛灵思Virtex-6 HX565T 时, 该框架占用FPGA 的资源不足 7.5%。这其中包括PCIe® 接口,四个 10GE 接口、两个SDRAM 控制器和四个 SRAM 控制器。

该开发框架提供了一个“沙盒”供编程人员开发自己的应用。它有数个易于理解的对外接口,便于在 FPGA 卡上迅速集成应用。另提供示例代码和示例,展示如何开箱即用地运用接口,布置系统数据流,从而增强开发人员的信心。

节省数月时间

为降低在 FPGA 器件上开发 HDL 代码涉及的风险,缩短开发时间,我们的FPGA 开发框架集成并优化了在 FPGA卡上开发应用所需的全部控制器。这至少可以缩短项目数月的开发时间。我们还建议将 C-to-HDL 编译器工具集成在开发框架中,因为研究结果表明,虽然工具生成的代码效率低于 HDL 直接编码,但它能够显著缩短开发时间。

在现实情况中,不存在一种能够适应各种情况的万灵丹式的方法。在权衡开发方法时,设计小组应有许多工具和选项可供使用和选择。在要求效率或紧凑代码时,或者在组件用于多个项目中时,最佳方法是使用 FPGA开发框架开发 HDL 组件。若优先考虑产品上市时间,以及已经有 C 语言代码可用的情况下, 最佳方法是使用C-to-HDL 编译器工具。最好是使用FPGA 开发框架在 HDL 中开发 TCP/IP 和 UDP/IP堆栈等固定功能的模块,同时需要经常修改的算法可以使用赛灵思 AutoESL [4] 或 Impulse[5] 高层次综合工具等高级语言工具来开发。

金融交易系统的应用

图 7 是需要在很高水平上实现的算法交易系统的不同组成部分。ATS 必须具备读取一个或多个市场数据馈入,过滤数据并发送到不同“篮子”中用于分析,制定交易决策以及与一个或者多个交易所通信的能力。

交易逻辑和策略组件会经常变动,且不同的交易机构有自己的一套做法。他们最好是使用 C-to-HDL 编译器来实现,以满足产品上市时间要求,而且如果市场要求,可以在后期转为使用效率更高的实现方式(使用 FPGA 开发框架)。另一方面,网络协议和金融协议不会经常发生变化,用高效的方法实现这些协议会严重影响系统性能。因此我们建议使用 expressXG 开发框架在 HDL 直接实现这些协议。

速度、响应性和预测性

金融交易行业,在速度和超低时延的推动下,FPGA 技术不断得到推广和普及。这个行业的用户面临着诸多挑战,包括不熟悉 FPGA 设计、技能要求不同、有庞大的高级语言代码库等。我们的 expressXG FPGA 开发平台能够简化在基于 FPGA 的高性能以太网PCI Express 卡上进行的应用开发工作,并缩短应用开发时间。为便于移植现有的 C 语言代码,或者在产品上市速度压倒一切的情况下,我们建议将一个 C-to-HDL 编译器集成在该框架中。

我们认为集成有 C-to-HDL 编译器的 expressXG 有助于 FPGA 技术的采用,提高交易系统的速度、响应能力和预测能力。

电子发烧友App

电子发烧友App

![表 1 - 从 HLL-to-HDL 工具与直接用 HDL 开发的对比可以看出,虽然显著节省了时间,但得到的代码比用 HDL 直接创建的低效。[1]](/uploads/allimg/171122/1G92TJ0-2.png)

评论