电子发烧友网核心提示: 根据ALTERA官方FAE(现场应用工程师)的强烈建议,请注意不要随意带电插拔JTAG下载接口,否则会损坏FPGA芯片的JTAG口信号管脚。 现象: 在排除了下载线的问题

2012-09-05 09:00:42 12784

12784 Flash读写硬件实现方案,该方案利用硬件对SPI Flash进行控制,能够非常方便地完成Flash的读写、擦除、刷新及预充电等操作,同时编写的SPI Flash控制器IP核能够进行移植和复用,作为SOC芯片的功能模块。

2013-09-24 09:12:37 5517

5517

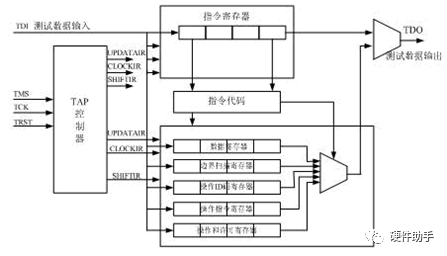

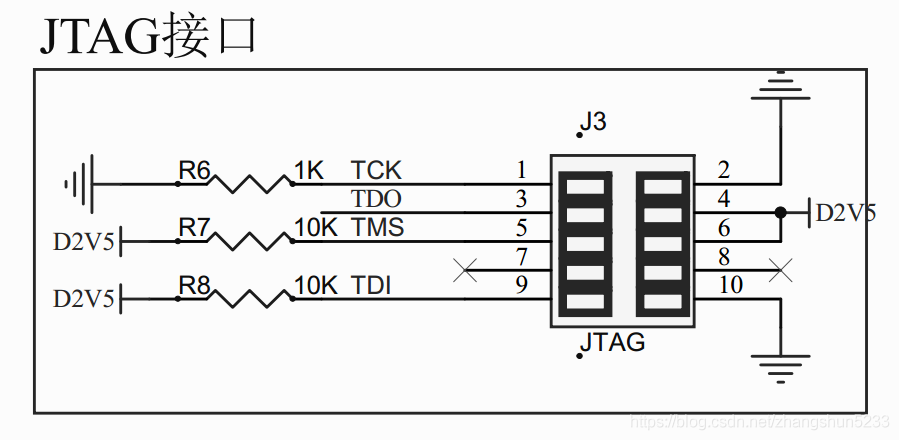

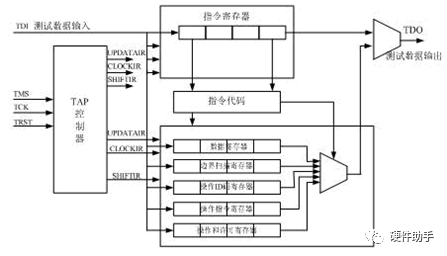

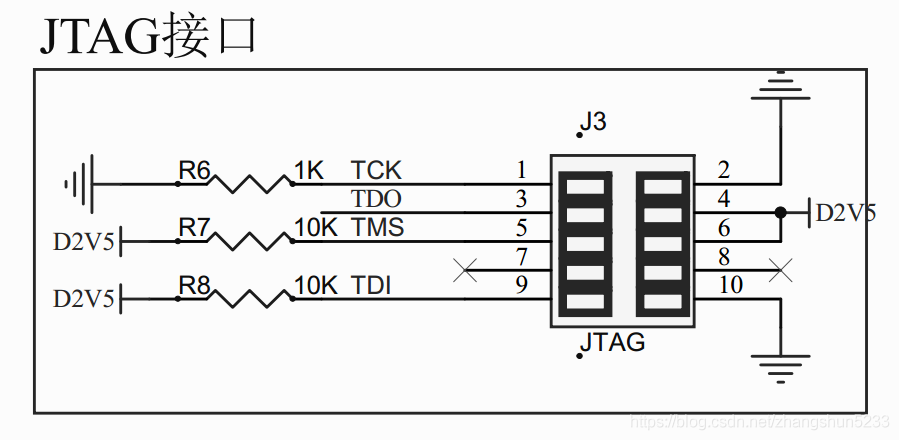

JTAG接口主要包括以下四个引脚:TMS TCK TDI和TCO及一个可选配的引脚TRST,用于驱动电路模块和控制执行规定的操作。

2014-09-15 12:44:31 22903

22903

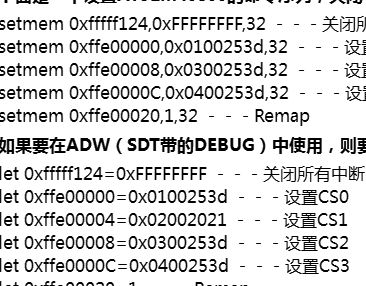

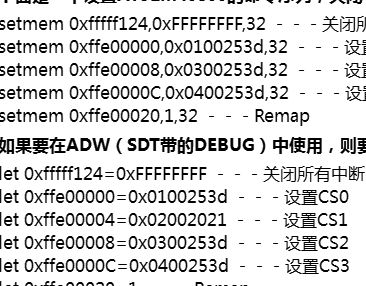

时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers

2018-05-29 09:41:16 5925

5925 时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers

2018-06-12 09:38:04 7732

7732

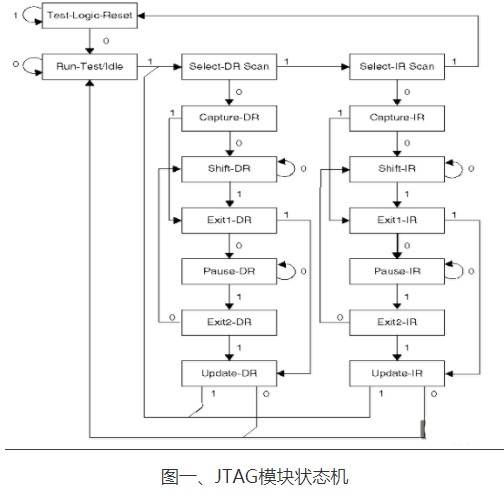

本文主要介绍JTAG总线的引脚定义、接口标准、边界扫描和TAP控制器。 JTAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容

2020-11-27 14:13:28 13488

13488

先说明一下我的配置,板子是自制的,片子TMS320C6713,XP系统,裸机开发,仿真器SEED-XDS510plus现象:在我修改代码之前,JTAG没问题。我使用指针向EMIF接口FLASH存入

2019-01-16 11:16:06

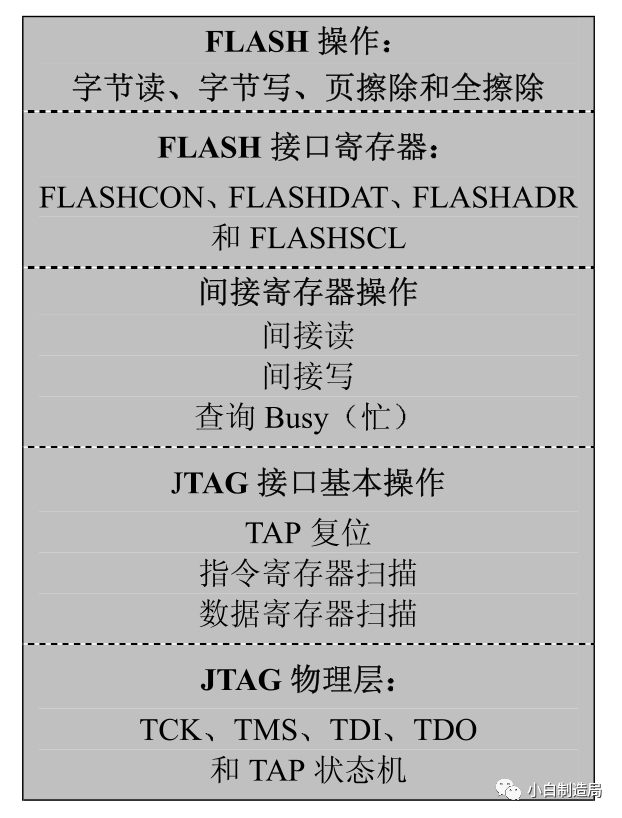

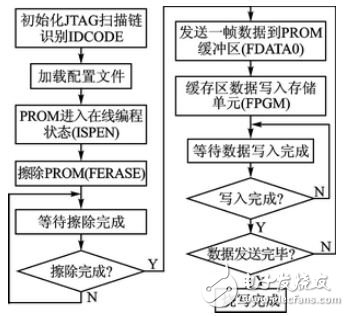

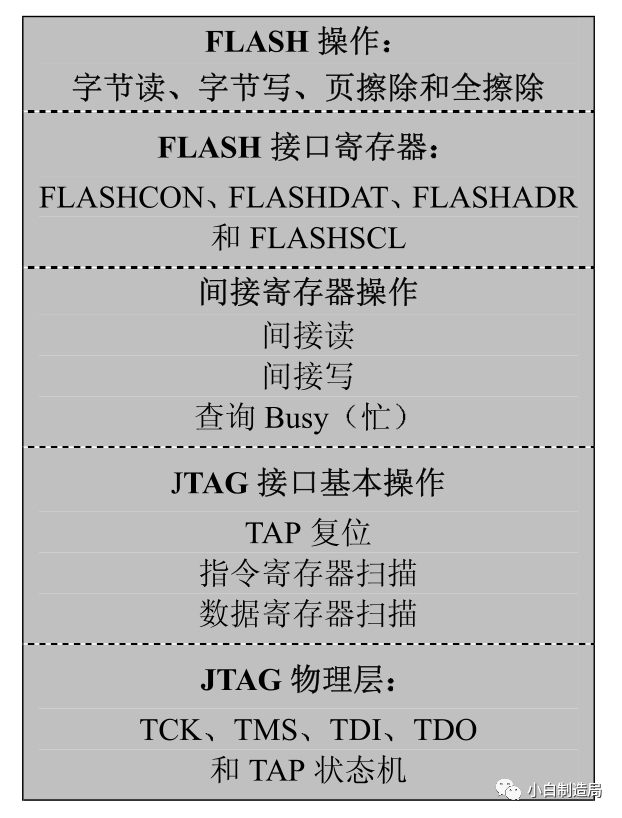

用写缓冲的编程方式来烧写一帧配置码流的时间要小于等待时间,因此必须选用写缓冲的编程方式来烧写Flash存储器。JTAG接口与Flash控制器间的命令和数据翻译由反向兼容JTAG控制器中的烧写控制模块

2019-06-10 05:00:08

FPGA的JTAG接口和ARM的JTAG接口线是否可以共用同一线呢?是否可以用同usb转JTAG线给ARM和FPGA以及dsp调试程序呢?

2022-08-10 14:54:43

Flash控制器的主要的工作任务Flash控制器的两种策略和方式

2021-02-23 07:31:10

JTAG 作为一个通用的标准器件功能测试接口, 具有灵活高效、易于实现等优点, 是微控制器、微处理器、DSP、SoC 等器件的重要外部接口。它不但可以用来测试内部功能模块状态, 而且可以实现在线调试

2019-08-27 06:18:54

CYCLONE IV FPGA 想用JTAG口编程FLASH,MSEL所在BANK被用于DDR,IO电压为1.8V,手册的配置方案表中AS模式的配置电压标准没有1.8V。是否可以理解成在JTAG方式

2019-03-21 10:24:44

控制、看门狗、以太网10/100MAC控制器以及Fusion器件的模拟接口;在AHB总线上可接SRAM和Flash Memory控制器。

2019-07-26 07:46:51

基于SDRAM控制器实现FPGA模块化和通用性的解决方案设计

2020-12-22 07:58:55

设计按照上述4个状态进行Verilog设计,经过仿真和上板调试,效果很好,下面是状态机设计程序,仿真时序图如图3,图4所示。3、结语本文设计的LBS控制器应用在PEX8311和FPGA接口中运行

2015-01-29 14:09:17

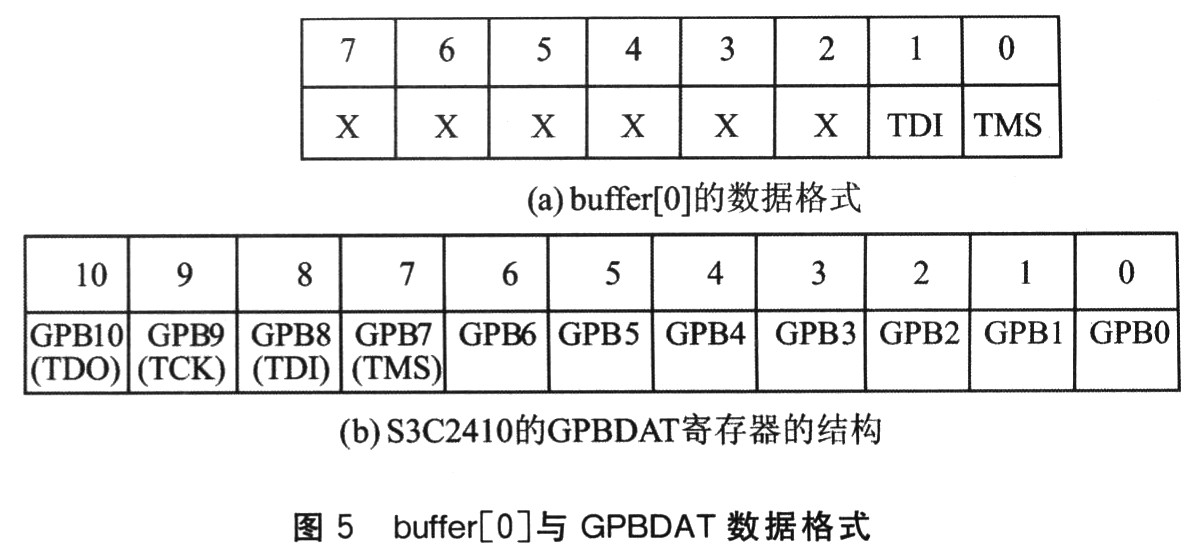

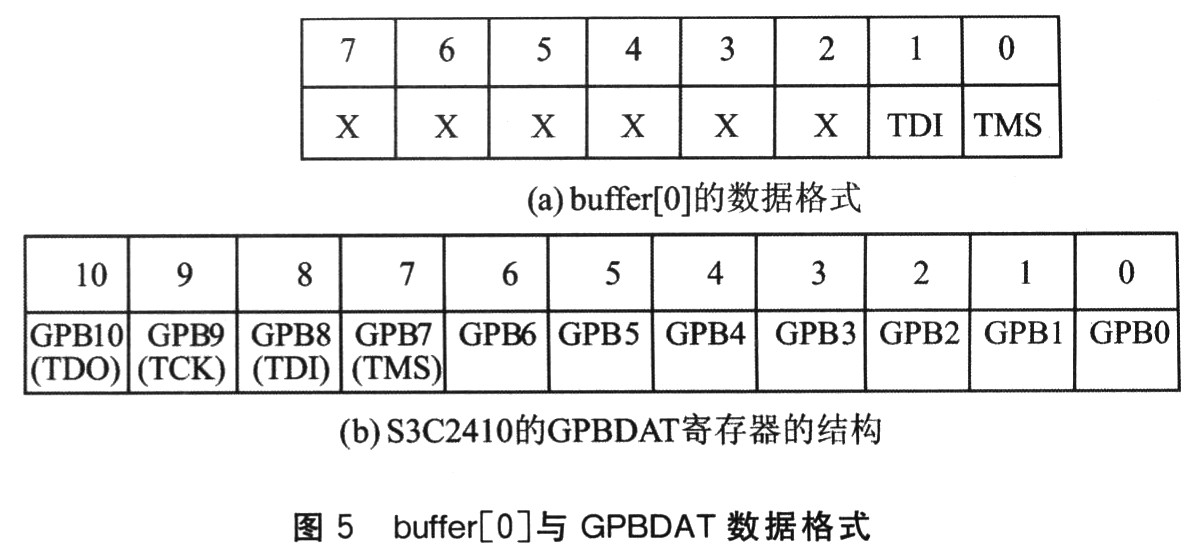

论文以Compaq、Microsoft 等公开的 USB 主机控制器接口规范为基础,遵循USB 主机的协议规范,开发了独立于操作系统的USB 主机底层驱动程序,并在S3C2410 平台上得到了验证。下面详细论述主机控制器接口规范及 驱动程序实现。

2020-03-31 06:57:20

未连接 从简单讲JTAG原理是TAP控制器控制输入输出;连接方式各个引脚的定义如下。Test Clock Input (TCK) TCK在IEEE 1149.1标准里是强制要求

2011-09-21 10:11:36

什么是NAND Flash?NAND Flash在嵌入式系统中的作用是什么?如何去使用NAND Flash控制器?

2021-06-21 06:56:22

时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,TImers

2017-09-12 10:20:03

你好,我有一块板子,JTAG接口仅连接到FLASH,不包括扫描链中的FPGA。当我将编程器连接到板上的JTAG接头时,电缆盒上的灯变为绿色,但是当我尝试使用IMPACT软件对FLASH进行编程时,我

2020-05-28 13:42:00

看完JTAG模式下在线配置FPGA和烧录配置芯片的原理,我们再了解一下FPGA上电初始的配置过程。FPGA上电后,内部的控制器首先工作,确认当前的配置模式,如果是外部配置芯片启动,则通过和外部配置芯片的接口

2016-08-10 17:03:57

本文介绍一种通用SDRAM控制器的FPGA模块化解决方案。

2021-05-07 06:42:49

求大佬介绍一种通用SDRAM控制器的FPGA模块化解决方案

2021-04-08 06:40:34

过程。FPGA上电后,内部的控制器首先工作,确认当前的配置模式,如果是外部配置芯片启动,则通过和外部配置芯片的接口(如我们的SPI接口)将配置芯片的数据加载到FPGA的RAM中,配置完成后开始正式运行

2018-03-05 16:30:35

目前伺服控制器的设计多以DSP或MCU为控制核心,但DSP的灵活性不如FPGA,且在某些环境比较恶劣的条件如高温高压下DSP的应用效果会大打折扣,因此以FPGA为控制核心,对应用于机载三轴伺服控制平台的控制器进行了设计与优化。

2019-07-16 07:41:04

基于FPGA的图形式AMLCD控制器该如何去设计?怎样去设计一种VGA视频接口电路?

2021-06-08 06:57:57

基于JTAG接口实现ARM的FPGA在线配置设计

2012-08-19 23:17:24

。运动控制器采用DSP与FPGA芯片作为主控芯片,主要包括DSP模块、FPGA模块、FPGA外围电路模块和数字量输入输出接口模块。 采用基于DSP与FPGA的运动控制器,能够实时完成复杂的轨迹运算

2009-09-19 09:43:00

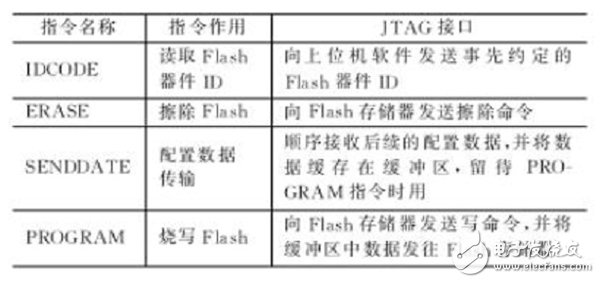

寄存器(IR-InstruetionRegister)和数据寄存器(DR-DataRegister)中。JTAG接口模块在接收到上位机软件发送的指令后,相应的解释如表1所列。2FIash控制器和FPGA

2019-06-06 05:00:38

有iMPACT的情况下通过JTAG对ISF进行编程的好选择?如何使用JTAG从微控制器重新编程FPGA的ISF?FPGA启用了“内部主SPI闪存模式”。使用的JTAG TCK频率为990KHZ。读取IDCODE与SWF文件一起正常工作。如果需要更多信息,请与我们联系。谢谢,萨德什

2019-08-05 07:18:55

本文提出了一种基于FPGA的SDRAM控制器的设计方法,并用Verilog给于实现,仿真结果表明通过该方法设计实现的控制器可以在FPGA芯片内组成如图1所示的SDRAM接口,从而使得系统用户对SDRAM的操作非常方便。

2021-04-15 06:46:56

晚上好,如何将微控制器与FPGA连接?如何使用微控制器配置FPGA?如何使用微控制器或软件程序为FPGA创建.bit文件以使用微控制器配置FPGA?任何人都可以告诉发送与这些排队相关的文件....提前致谢问候Vimala

2020-03-25 09:22:18

JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers,GPIO等等的寄存器。上面说

2017-10-11 14:37:20

正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers

2017-08-21 14:59:30

我想知道是否有人能指出一份文件,该文件为Xilinx FPGA中的JTAG操作提供了深入的技术细节。我正在考虑将自己的TAP控制器构建到JTAG程序/更新FPGA。我还想了解Xilinx特定JTAG

2019-01-24 09:36:40

FMC模块上有一个带有SPI FLASH的Xilinx FPGA进行配置。我们可以通过载板JTAG编程FMC模块上的SPI FLASH吗?问候塔朗金达尔

2020-04-15 10:16:00

我想通过JTAG在我的设计中内部访问寄存器。1)如何挂钩fpga JTAG链?2)是否有JTAG控制器IP?我看了,没看到一个。谢谢,弗雷德

2020-05-29 06:13:24

NAND FLASH Controller IP Core标准NAND FLASH Controller标准NAND FLASH控制器 我是一位在职者(北京),专业从事FPGA接口设计,有较多的空余

2012-02-17 11:11:16

NAND FLASH Controller IP Core标准NAND FLASH Controller标准NAND FLASH控制器我是一位在职者(北京),专业从事FPGA接口设计,有较多的空余

2014-03-01 18:49:08

求大佬分享一种基于FPGA的NAND FLASH控制器的设计方法?

2021-05-08 07:46:27

如果我在所有2.5V电源(所有VCCIO-s,VCCAUX)下运行SPARTAN 6,那么DS_FT2232D USB控制器的JTAG接口是否有效? JTAG使用'A'端口的四条线。 “A”端口

2019-08-02 08:26:56

基于FPGA的MCU设计有两种基本实现方式如何实现微控制器与FPGA的接口设计

2021-05-06 10:05:17

XAPP1251说明显示,可以在Zynq ARM处理器上运行XVC服务器来控制FPGA中的JTAG端口。但是,我不清楚,是否可以在同一个FPGA中控制PL JTAG?可以使用运行在设备PS部分上

2020-07-30 13:51:19

模块在接收到上位机软件发送的指令后,相应的解释如表1所列。表1 JTAG指令解释2 Flash控制器和FPGA器件配置模块设计2.1 Flash控制器设计烧写Flash存储器和利用Flash存储器配置

2019-05-30 05:00:05

:TMS(模式选择)、TCK(时钟)、TDI(数据输入)、TDO(数据输出线)。本文利用JTAG标准协议设计一种针对同类FPGA进行动态重构配置的重构控制器。

2019-10-17 07:50:32

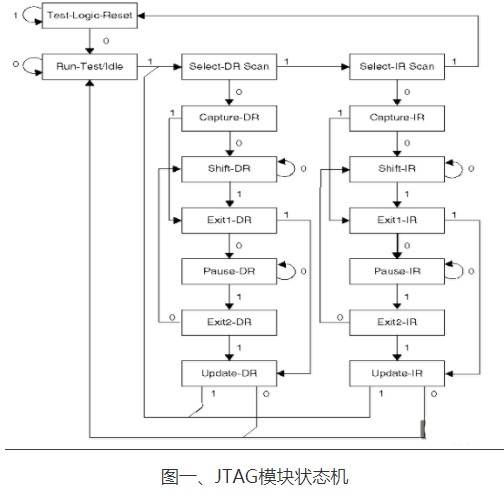

通过JTAG 实现对Flash 在线编程。首先, 介绍JTAG 的定义、结构及引脚的定义, 并阐述JTAG 状态机的工作原理。然后,介绍JTAG口的边界扫描寄存器,给出实现JTAG在线写Flash的电路, 和

2009-04-16 10:00:04 59

59 对Flash 编程是许多嵌入式系统开发中必要的一环,传统的开发工具通常支持的是并口或串口,而随着计算机接口的单一化,即插即用的USB 接口得到了广泛的应用。本文介绍了JTAG

2009-06-23 13:24:34 62

62 本文分析了航天相机控制器的构成与功能,并利用FPGA 设计实现了相机控制器的外围接口,包括异步串行通讯接口、计时器接口、步进电机控制器接口,并给出了仿真结果。程序

2009-12-19 15:47:05 18

18 设计了一种能使FPGA的主状态机直接管理Flash的控制器,该控制器具有自己的指令集和中断管理方式。用户可以根据FPGA的系统时钟对控制器进行操作,无需关心Flash对指令和数据的时

2010-09-30 16:43:54 48

48 什么是jtag接口

JTAG(Joint Test Action Group ,联合测试行动小组 ) 是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试, J

2007-12-20 13:40:08 47060

47060

摘要:本应用笔记讨论串口转JTAG接口板能够接收的命令。该接口板用于实现与MAXQ微控制器的接口。此处描述的命令可帮助开发人员读写MAXQ存储器(代码和数据),读写寄存器,以及使

2009-04-23 17:28:05 995

995 基于JTAG边界扫描方式的重构控制器的设计

引言

JTAG(联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),目前主要用于芯片内部测试。现在多数的

2010-02-06 10:48:07 1166

1166 基于JTAG接口实现ARM的FPGA在线配置设计

引 言 为了解决不同标准间无线接口技术的互通和兼容,人们提出了软件无线电(Software Defined Radio,SDR)技术

2010-02-09 10:56:10 3142

3142

本文档是配置MCF521x微控制器的FLASH模块的一个快速参考。通过对该模块基本的功能描述和配置选项的解释,能更好地理解flash模块是如何工作的。本应用笔记还提供了一个实例,示范了

2011-09-19 14:11:23 51

51 FLASH存储器接口电路图(Altera FPGA开发板)

2012-08-15 14:36:31 6269

6269

设计了一种基于DSP与FPGA的运动控制器。该控制器以DSP为控制核心,用FPGA构建运动控制器与传感器以及电机驱动器的接口电路。充分发挥了DSP强大的运算能力和FPGA的并行处理能力。具有

2012-10-26 15:21:51 93

93 IAR+H_JTAG调试FLASH说明及例程。

2016-02-18 15:11:44 4

4 基于FPGA的LED屏控制器设计基于FPGA的LED屏控制器设计

2016-06-21 17:56:39 50

50 Xilinx的JTAG电缆可以通过FPGA“直接”烧写SPI/BPI。很多对xilinx开发环境不熟悉的用户,如果第一次接触这种烧写模式可能会有疑惑,FPGA是如何做到JTAG和Flash之间

2017-02-08 02:40:11 6513

6513

本文档介绍了MSP430F2单片机的Flash存储控制器的操作。MSP430的Flash存储器是可位、字节、字寻址和编程的存储器。该模块由一个集成控制器来控制编程和擦除的操作。控制器包括三个寄存器,一个时序发生器及一个提供编程、擦除电压的电压发生器。

2017-09-21 15:14:11 6

6 时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers

2017-10-13 19:28:04 3

3 时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,TImers

2017-10-13 20:47:11 7

7 4.4 实验内容使用JTAG烧写Nand Flash 1.实验目的 通过使用JTAG烧写Flash的实验,了解嵌入式硬件环境,熟悉JTAG的使用,为今后的进一步学习打下良好的基础。本书

2017-10-18 17:03:48 6

6 实现了一种适用于航天设备的大容量存储方案。给出一个基于FPGA实现的Flash控制器设计,该控制器可以完成航天应用的大容量数据存取工作。其中存储操作中设计了流水编程机制,实现了叠装芯片内部的流水编程

2017-11-13 16:56:50 3

3 时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers,GPIO等等的寄存器。

2017-11-15 13:06:30 2561

2561 , FPGA)进行远端升级,本文提出了一种基于XVC (Xilinx visual cable)协议,通过以太网,利用ARM 微控制器控制FPGA 的JTAG 接口对其进行远程更新与调试的方法。该方案附加电路少,易于拓展,同时也提高了更新可靠性。

2017-11-16 20:13:02 12514

12514

设计方案。通过FPGA完成CAN总线控制器、FlexRay总线控制器、RapidIO总线接口等模块功能,实现高速接口的控制和扩展,并使模块接口具备可配置能力。测试结果表明,CAN接口及FlexRay接口在指定的波特率下均工作正常,满足项目要求的各项性能指标。

2017-11-18 07:25:44 9023

9023

中[1] 。它比起传统的并行总线接口Flash 来说节省了很多的I/ O 口资源,从而为系统功能的扩展提供了更多的可能。为此提出了一种基于FPGA 的SPI Flash 控制器的设计方法,并用

2017-11-22 08:47:39 12558

12558

随着存储技术的不断进步,Flash Memory的存储容量越来越大,读写数度越来越快。本文实现的NAND Flash控制器放置在CPU和NANF Flash器件之间,实现了NAND Flash

2017-11-23 14:15:35 2812

2812 Hercules系列微控制器使用教程选择JTAG仿真器

2018-08-13 02:37:00 3750

3750 指纹识别模块的硬件设计采用 SOPC的设计思路[1],在FPGA内部实现指纹读取 UART接口、FLASH存储器接口、SDRAM控制器、PIO控制的键盘和 LCD显示接口。

2018-08-18 09:45:12 750

750

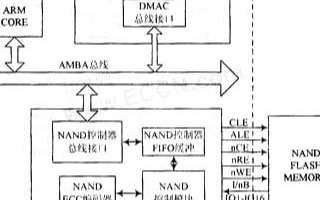

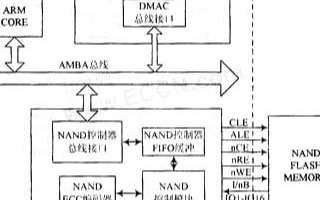

本文所讨论的NAND FLASH控制器是针对一款基于ARM7TDMI的SoC芯片,该控制器在芯片中的位置如图1所示,作为AMBA总线上的一个从设备集成于AHB上。主要模块包括总线接口模块、FIFO缓冲模块、ECC编码模块以及逻辑控制模块。

2020-05-20 08:00:00 1735

1735

JTAG接口主要由4根信号线组成:TCK、TDI、TDO、TMS,不同的公司还添加几根辅助信号线,例如:NTRST、VERF、GND等信号。TCK是JTAG模块外部输入时钟;TDI是JTAG模块外部数据输入信号;TDO是JTAG模块外部输出信号;TMS是JTAG模块的模式选择信号;

2019-07-16 08:20:00 3649

3649

本视频介绍了可用于构建7系列FPGA内存控制器的软IP。

这些模块讨论了如何使用Xilinx存储器接口生成器构建存储器控制器以及MIG如何构建存储器控制器。

2018-11-22 06:05:00 4269

4269 JTAG(联合测试工作组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

2019-03-27 14:54:26 29344

29344 同志们,根据ALTERA官方FAE(现场应用工程师)的强烈建议,请注意不要随意带电插拔你的JTAG下载接口,否则会损坏FPGA芯片的JTAG口信号管脚。

2019-07-31 17:35:00 0

0 与传统ASIC相比,FPGA和结构化ASIC的优势在于重用灵活性高、上市时间快、性能佳而成本低。FPGA和专用的IP模块可用于现有的商用AdvancedTCA平台,可用来开发可扩展的交换接口控制器(FIC),以加快产品开发的设计并使线卡方案具有鲁棒性和成本效益。

2019-08-24 09:43:06 841

841

则费时费力且还需拆结构。若在FPGA内部通过逻辑代码搭建一Flash控制器实现对Flash器件的读写操作,即可并行实现系统内每片FPGA对配置文件的在线更新,大大缩短程序固化时间。本文依托于Xilinx

2020-01-27 16:17:00 2747

2747

随着USB接口的越来越普及,现在几乎所有的接口都可以转换成USB接口,本文主要介绍一下Xilinx FPGA的JTAG接口转换成USB接口的方案。

2020-01-24 17:34:00 15016

15016 赛灵思公司的FPGA芯片具有IEEE 1149.1/1532协议所规定的JTAG接口,只要FPGA上电,不论模式选择管脚M[1:0] 的电平,都可用采用该配置模式。JTAG模式不需要额外的掉电

2020-12-31 17:30:55 13

13 NAND Flash主机接口控制器技术研究(嵌入式开发入门 csdn)-该文档为NAND Flash主机接口控制器技术研究总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 12:23:31 12

12 时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers

2021-09-12 16:11:34 5543

5543 FPGA MCU通信——异步接口(仿NAND Flash)FPGA MCU通信——异步接口MCU侧开发注意事项FPGA侧注意事项FPGA MCU通信——异步接口之前很早就听说了FSMC

2021-10-26 11:51:03 27

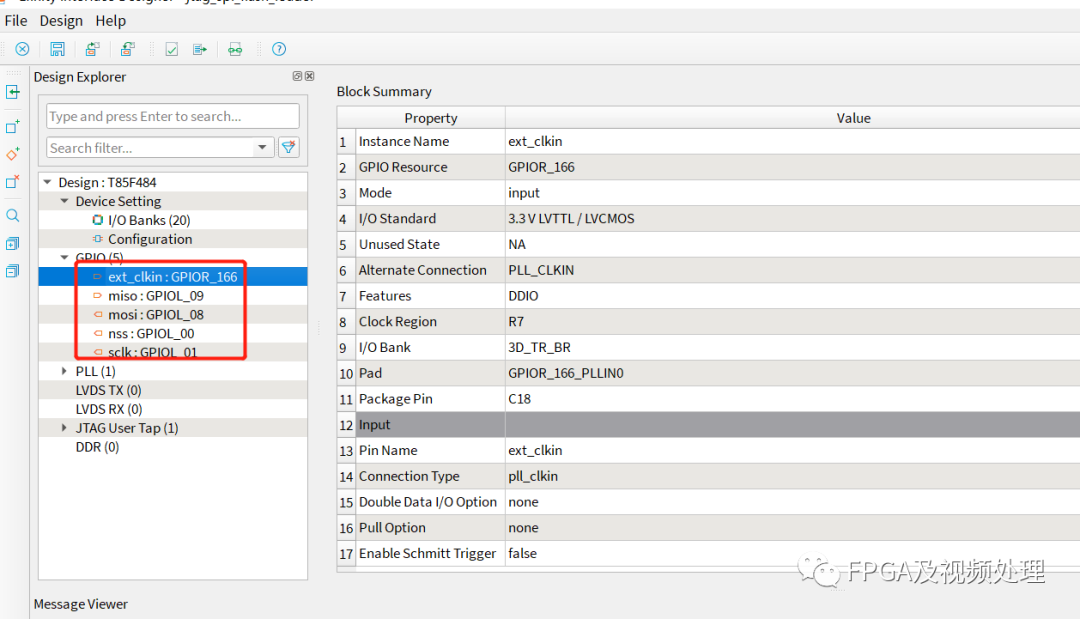

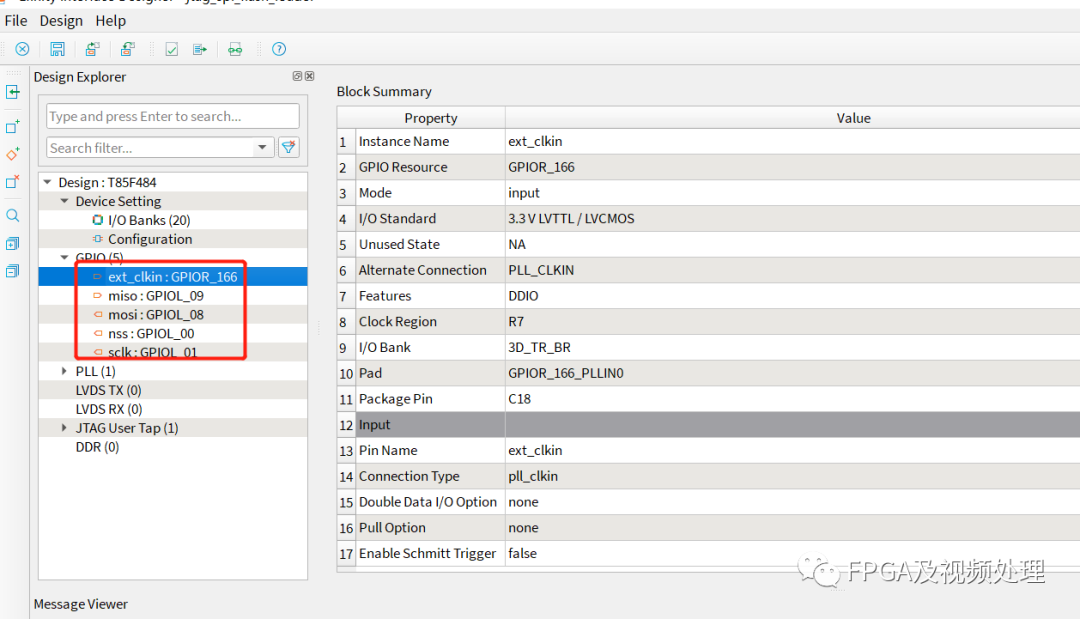

27 易灵思在通过JTAG写入Flash时,需要手动创建一个打通JTAG到Flash的bridge,这里我们来介绍下工程创建过程和烧写操作。

2022-03-09 16:04:58 4007

4007

通常在嵌入式应用中,微控制器上的每一个端口引脚都需要,没有多余的端口引脚。大多数具有可重写内部程序存储器(如闪存或EEPROM)的MAXQ®微控制器支持标准化的JTAG/TAP接口(也称为调试端口),外部主机使用该接口访问在线调试或在线编程(引导加载程序)功能。

2023-01-10 11:34:33 742

742 通过JTAG接口为FPGA下载程序时遇到了速度很慢甚至ISE上配置TCK时钟最小的为250kHz时,依然无法保证下载成功。

2023-06-25 16:06:58 1130

1130

一个基于FPGA的SPI Flash读写硬件实现方案,该方案利用硬件对SPI Flash进行控制,能够非常方便地完成Flash的读写、擦除、刷新及预充电等操作,同时编写的SPI Flash控制器IP

2023-07-15 16:55:01 1181

1181

首先,我们来看看JTAG烧录FLASH的层次结构

2023-10-19 11:35:18 665

665

jtag接口和swd接口区别 JTAG (Joint Test Action Group) 接口和 SWD (Serial Wire Debug) 接口是两种用于调试和烧录嵌入式设备的常见接口。虽然

2023-12-07 15:29:41 2779

2779

电子发烧友App

电子发烧友App

评论