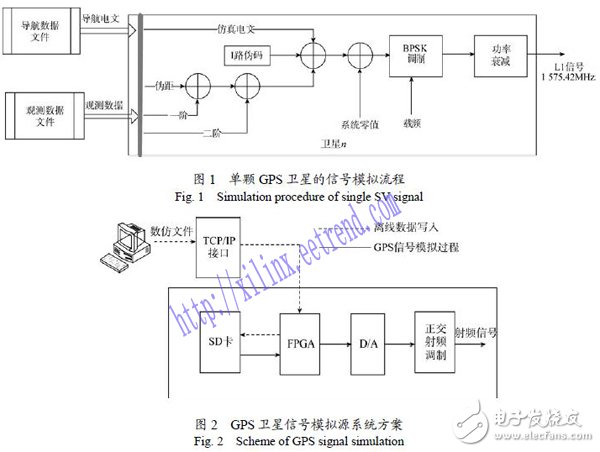

真实的多颗 GPS 卫星信号在空间合成, 而模拟的GPS 卫星信号在数字域实现叠加合成。采用地址发生器产生12 颗卫星的特征码, 分别与对应的导航电文进行叠加, 合成的基带信号通过正交射频调制,调制为L1 频点1.575 GHz 的射频信号。

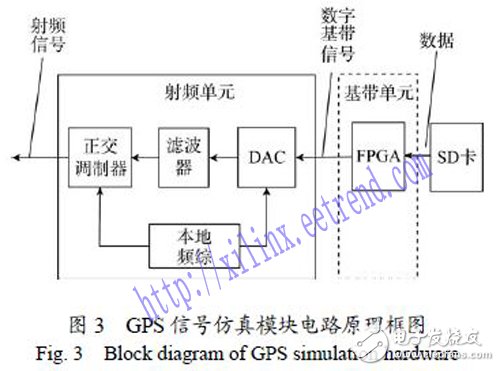

而 GPS 卫星信号模拟源采用图2 所示方案。采用SD 卡存储导航电文和观测数据文件。在系统工作时, FPGA 读取SD 卡的数据, 按图1 所示的流程产生卫星的基带信号, 多颗星的基带信号经数字合成后,送至DA 变为模拟信号, 再进行正交射频调制获得L1 频点的射频信号。

当系统需要更新数仿文件时, 则通过TCP/IP 接口对SD 卡进行读写操作, 实现SD 卡中的文件更新。

数据文件格式

GPS 信号模拟的目的是使GPS 接收机通过接收模拟的信号正常工作, 实现定位解算。而GPS 信号是由多颗不断运行的GPS 卫星实时发射产生的。为了实现GPS 信号模拟, 首先需要设定用户轨迹、建立GPS 卫星轨道模型和信号传输模型, 运算量较大。因此采用离线运算的方法, 先在高性能计算机上进行仿真计算, 再将计算得到文件保存下来。GPS 模拟器通过读取该文件, 实现GPS 信号的仿真。这种方法的好处在于为模拟器节省了大量的资源, 有利于降低成本和体积。

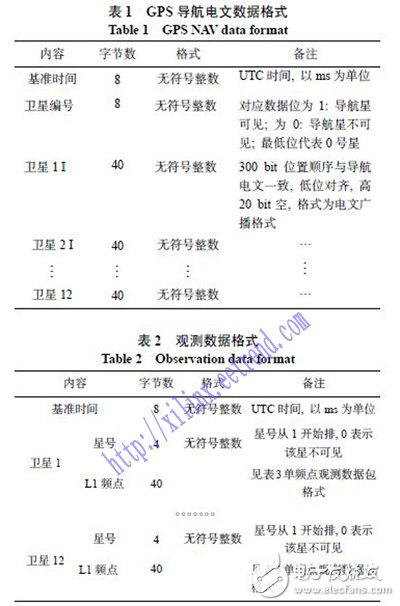

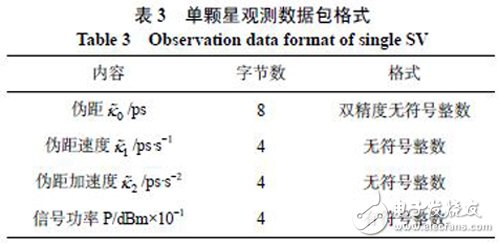

为了让接收机实现定位, 必须要提供4 颗以上的GPS 卫星信号; 仿真了12 颗GPS 卫星的数据, 仿真数据主要包括导航电文和观测数据。导航电文格式为300 bit, 占40 字节, 剩余20 bit 空; 观测数据则根据设定的位置和卫星星历产生, 模拟固定位置接收机产生的伪距变换, 20 ms 更新一次, 为了实现伪距的连续变化, 观测数据中还包含伪距速度和加速度, 便于信号产生过程中的插值。

GPS 导航电文速率为50 bps, 300 bit 为一子帧, 一子帧为6 s。一帧包含5 子帧, 共1 500 bit, 历时30 s。一超帧则包含25 帧, 37.5 k, 历时12.5 min。由于GPS 电文每两小时更新一次, 则2 h 需存储的导航电文约为 375 k; 12 颗星的导航电文为4.5 M。

观测数据则为20 ms 更新一次, 单颗星的观测数据为40 个字节, 一个观测数据包有12 颗星, 共4 288 bit; 则2 h 的数据量为4 288×50×7 200=1 543680 000 bit, 约1.5 G。因此, 采用2 G 的SD 卡可完成上述数据容量的要求。

硬件设计

GPS 信号模拟源的设计采用高速基带数字合成技术和正交中频、射频调制技术。多颗卫星信号以数字形式在高性能软件无线电处理平台上计算并合成, 有效提高系统通道间的一致性, 消除了卫星通道间的误差, 也消除了内部时间误差, 确保了高精度。该方案与射频合成方案相比增加了软件无线电数字部分设计的难度, 使得伪距控制精度、多普勒变化和幅度等均在数字部分计算, 简化了射频设计,避免了由射频群时延不一致产生的通道间误差和卫星间的钟差, 且数值计算、钟差可控, 有效保证了系统的设计指标。信号模拟源方案原理如图4 所示。GPS信号模拟源采用基带加射频的单元模块化结构设计。

GPS 信号模拟算法对数据处理率有较高的要求,然而通过分析延时算法, 这样庞大的计算量实际上只是简单的乘累加(MAC) 的流水操作, 其算法结构中并无复杂的数学运算(如正余弦、指数、对数等) ,可以说其运算结构是相对比较简单的, 所以考虑采用FPGA 芯片。而目前FPGA 的功能也日益增强, 内嵌于FPGA 的硬核与基本逻辑构建的软核也不断增强了FPGA 作为通用信号处理芯片的能力。通过综合考虑, 最终选择了用XILINX 公司的XC4VSX35作为主处理芯片。该芯片是XILINX 公司2005 推出的一款专门为数字信号处理而设计的高端FPGA, 其可编程数字信号处理模块XtremeDSP48 在−12 的速度等级上最高性能为500 MHz。

基带单元设计采用1 片Xilinx 高性能FPGAXC4VSX35 来完成。XC4VSX35 主要完成以下任务:1) 从SD 卡读入导航电文和观测数据; 2) 多星数据的分配; 3) 多星信号的精密延迟和动态特性控制;4) 多星信号的数字合成。设计上可完成12 颗星I 路的导航信号产生。

电子发烧友App

电子发烧友App

评论