138译码器的设置目的是为了实现IO复用,单片机上IO资源紧张,挂载的外设较多,为了解决这一矛盾,引入了138译码器单个138译码器能够利用3个IO实现8路选择(在逻辑上相当于扩展了5个IO),比赛

2022-01-12 07:25:11

74LS138译码器是什么?74LS138译码器的扩展方法是什么?

2022-01-19 07:14:36

(PIO46-PIO40),键8、键7、键6和键5四位控制输入数据,对译码器的工作性能进行硬件测试。(4)实验报告1. 给出实验Ⅰ的完整程序,说明程序中各语句的含义及其整体功能。2. 给出实验Ⅰ的时序仿真波形报告及其分析说明。3. 给出实验Ⅱ的硬件测试过程及结果的说明。

2009-10-11 09:22:08

关于138译码器位运算简化代码的思路分享

2022-02-25 07:43:15

第一次发帖,自己仿真的一个译码器,谢谢大家!

2016-03-22 13:34:35

译码器及其应用实验

2017-03-21 13:36:44

译码器1. 译码器定义译码器是一种用以检测输入位(码)的特定组合是否存在,并以特定的输出电平来指示这种特定码的存在的数字电路。——《数字电子技术基础系统方法》译码器的功能是将具有特定含义的二进制码

2021-12-07 09:37:27

这是译码器的一些资料。

2014-07-13 11:59:08

。TTL、CMOS又没有现成译码器可用。故而用二极管搭建此特殊译码器,简单、可靠低成本与现有系统亲和度高。我的高一级的产品显示部分用的是人机界面。

2016-11-17 09:40:39

MATLAB卷积编译码源代码

2012-04-10 20:38:14

,OFF,ON1D7点亮 ONON,ON,OFF1D8点亮 ONON,ON,ON1D9点亮注:X表示ON或OFF,即任意状态。 2 板级调试下载sp6.bit文件到FPGA中,可以如图视频一样操作拨码开关,实现3-8译码器的功能。 `

2015-11-02 13:17:03

芯片,这种数字芯片由简单的输入逻辑来控制输出逻辑,比如 74HC138这个三八译码器,图 3-15 是 74HC138 在我们原理图上的一个应用。从这个名字来分析,三八译码器,就是把 3 种输入状态...

2021-07-19 09:08:52

将译码器的使能端看做输入端、译码器的输入端看做地址端,则全译码器可作什么使用

2015-05-18 11:41:06

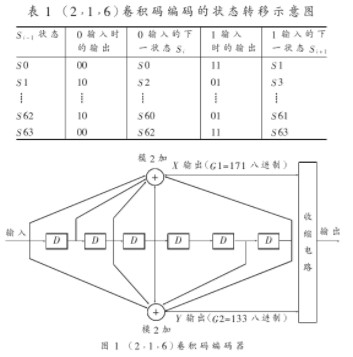

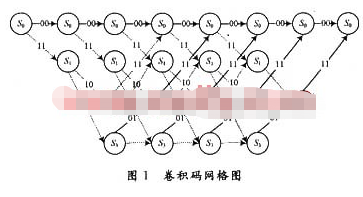

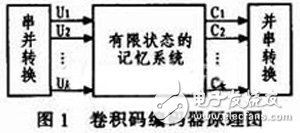

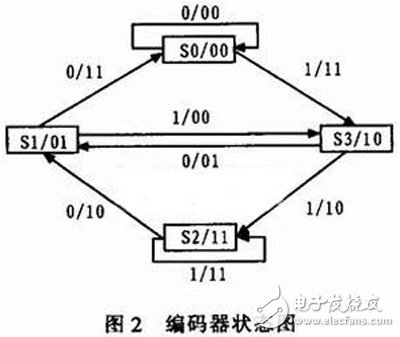

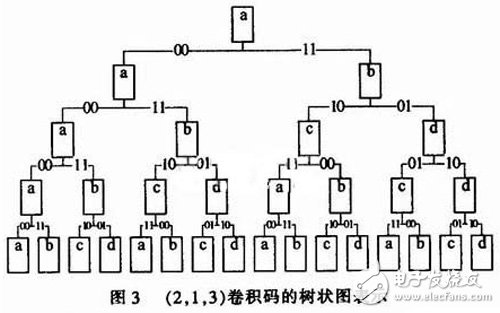

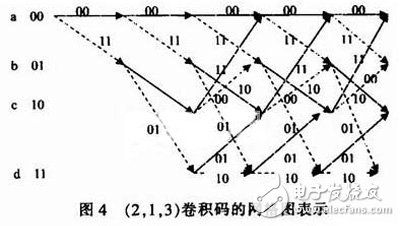

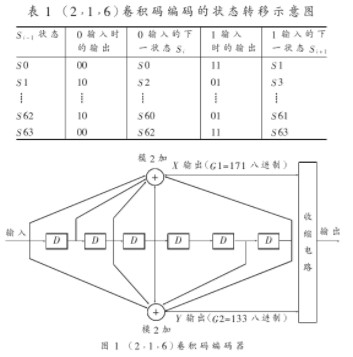

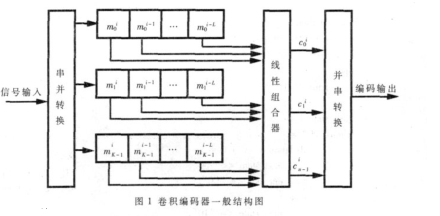

由于卷积码优良的性能,被广泛应用于深空通信、卫星通信和2G、3G移动通信中。卷积码有三种译码方法:门限译码、概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法,是卷积码的最佳译码方式,具有效率高、速度快等优点。

2019-11-01 08:05:38

译码器有哪些功能?Viterbi译码器是由哪几部分组成的?

2021-05-07 07:28:33

的?还有这篇文章是2010年发表的了,如今汉明码译码器的FPGA实现是否有更好的实现方法呢?有大神可以给我提供一个思路吗?or2万分感谢

2020-02-26 23:29:41

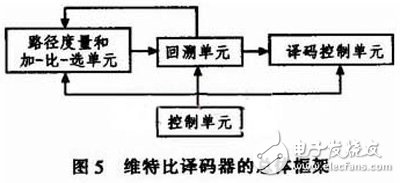

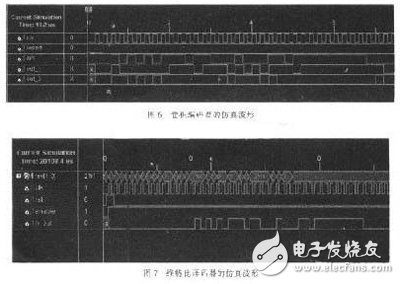

【摘要】:Viterbi译码器在通信系统中应用非常普遍,针对采用DSP只能进行相对较低速率的Vit-erbi译码的问题,人们开始采用FPGA实现高速率Viterbi译码。本文首先简单描述了

2010-04-26 16:08:39

对不同的设计方法进行分析和比较,选择优化的设计方法,利用VHDL分别设计(15,7)BCH码的编码器和译码器,并能够对两部分进行单独仿真调试,实现其相应的功能。

2012-05-10 11:36:06

在DIY的时候,有多元的选择是最好的。不同品种,不同的厂家,可必免断供,不同的型号可避免涨价打消制作的想法。在CPU或MCU中译码器器至关重要,多位译码器可使用74138多片联级,4位译码器可选

2022-10-02 16:40:44

显示译码器是什么?如何准确设计出符合功能要求的显示译码器?

2021-06-01 06:58:12

集成电路编码器和译码器的工作原理即逻辑功能是什么?如何利用逻辑门去实现一种集成电路编码器呢?如何利用译码器进行组合逻辑电路的设计呢?

2021-11-03 06:55:24

如何利用VHDL实现线性分组码编译码器的设计?

2021-04-28 06:41:40

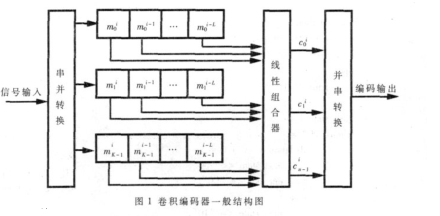

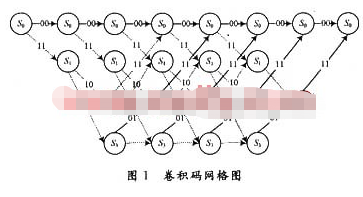

由于卷积码具有较好的纠错性能,因而在通信系统中被广泛使用。采用硬件描述语言VerilogHDL或VHDL和FPGA(FieldProgrammableGateArray——现场可编程门阵列)进行数字通信系统设计,可在集成度、可靠性和灵活性等方面达到比较满意的效果。

2019-10-14 06:02:23

一种在FPGA中实现的基于软判决的Viterbi译码算法,并以一个(2,1,2)、回溯深度为10的软判决Viterbi译码算法为例验证该算法,在Xilinx的XC3S500E芯片上实现了该译码器,最后对其性能做了分析。 关键词: OFDM;Viterbi译码;软判决;FPGA

2009-09-19 09:41:24

本文通过对长BCH码优化方法的研究与讨论,针对标准中二进制BCH码的特性,设计了实现该译码器的FPGA硬件结构。

2021-06-15 09:23:27

BCH码是目前最为常用的纠错码之一,我国的数字电视广播地面传输标准DTMB也使用了缩短的BCH码作为前向纠错编码的外码。针对该BCH码的特点,采用BM译码算法,设计了一种实时译码器。与其它设计方案

2021-05-25 07:04:32

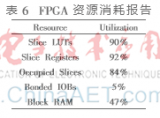

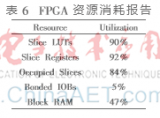

本文研究了RS码的实现方法,并基于Xilinx的FPGA芯片Spartan-6 XC6SLX45完成了RS编译码器的设计,同时对其进行了仿真和在线调试,并给出了功能仿真图和测试结果。时序仿真结果表明,该编译码器能实现预期功能。

2021-06-21 06:23:53

基于FPGA的Turbo码编译码器各模块实现的 VHDL或verilog HDL程序。急求啊谢谢大神啦!!

2015-06-08 22:45:24

截短Reed-Solomon码译码器的FPGA实现提出了一种改进的BM算法,并在此基础上提出了一种大量采用并行结构的截短RS码译码器的实现方式。验证表明,该算法能显著提高基于FPGA的RS译码器

2009-09-19 09:39:43

截短Reed_Solomon码译码器的FPGA实现提 出 了 一 种 改 进 的 算 法 并 在 此 基 础 上 提 出 了 一 种 大 量 采 用 并 行 结 构 的 截 短 码译 码 器 的 实

2012-08-11 15:50:06

求multisim数码显示译码器仿真!!!!译码器是CC4511。。。。。我的调不太通,希望看看大神做的成品,参考一下!!!!,很急!

2015-12-21 21:13:26

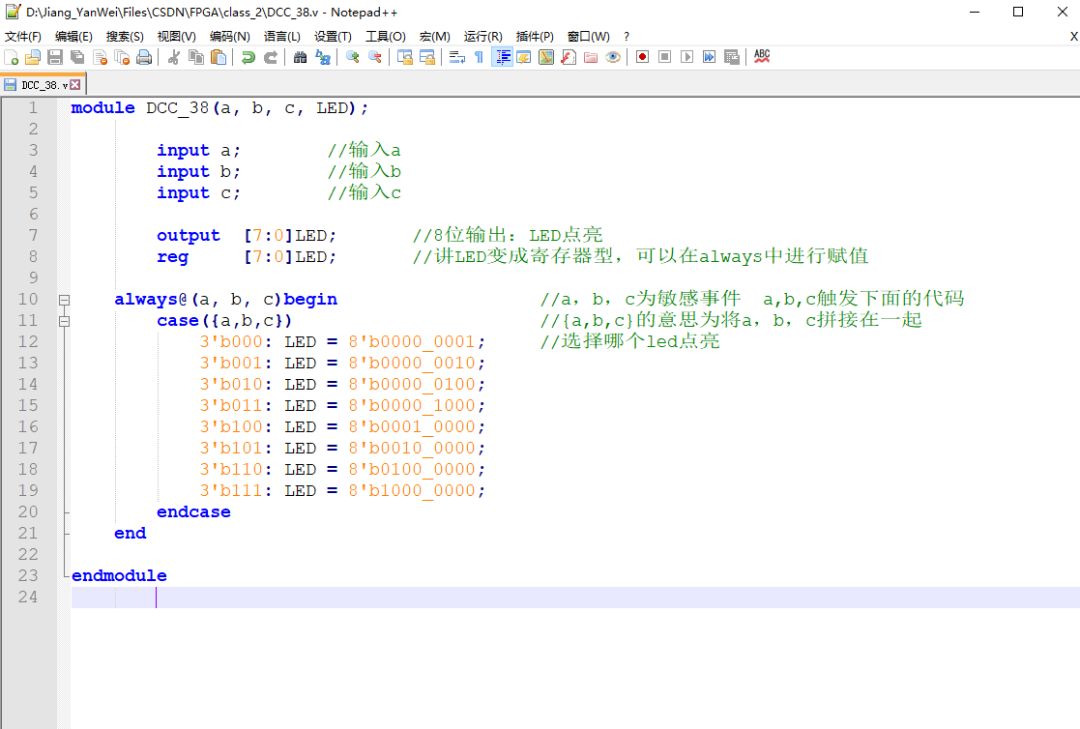

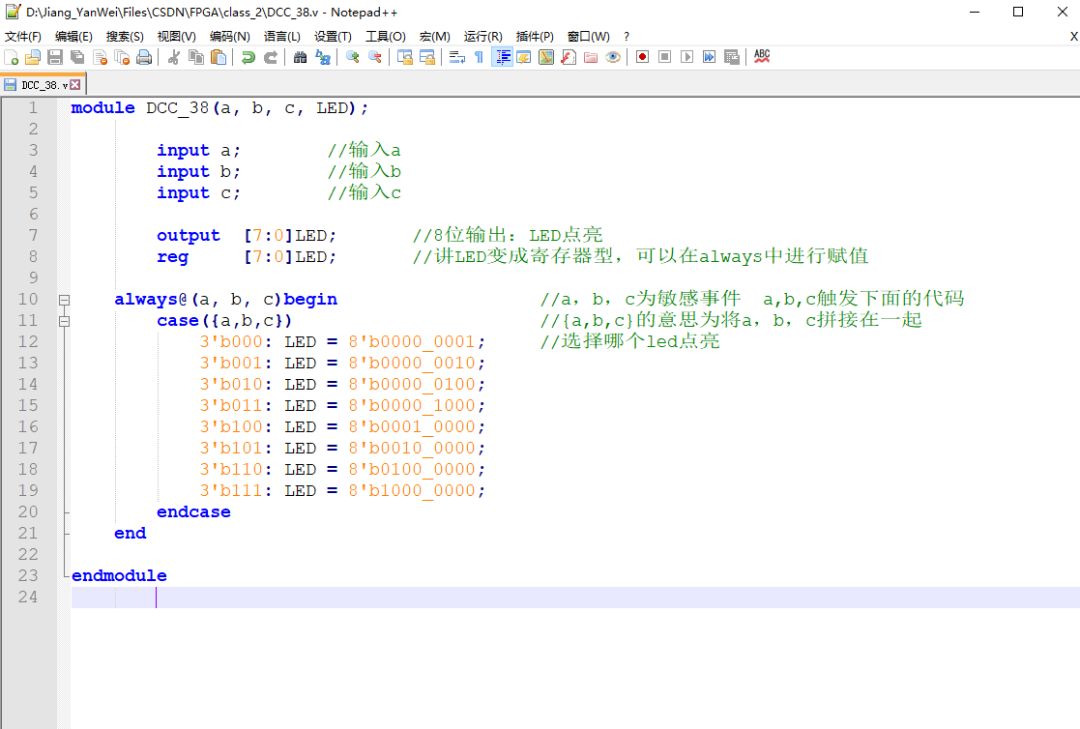

1、在FPGA中使用行为描述语句实现3-8译码器设计思路译码器电路有n个输入和2n个输出,每个输出都对应着一个可能的二进制输入。本实验设计实现一个3-8译码器,表3.1给出了该译码器的真值表。从

2022-07-01 15:26:26

Turbo码编码器的FPGA实现Turbo码译码器的FPGA实现Turbo码编译码器的性能有哪些?

2021-05-07 06:06:23

组合逻辑电路设计之译码器课程目标: 1. 再次熟悉Quartus II工程的建立以及完整的FPGA开发流程 2. 以译码器为例学会简单组合逻辑电路设计实验平台:无实验原理:组合逻辑,其任一时刻的稳态

2016-12-20 18:54:10

本帖最后由 芯航线跑堂 于 2016-12-23 21:02 编辑

组合逻辑电路设计之译码器课程目标: 1. 再次熟悉Quartus II工程的建立以及完整的FPGA开发流程 2. 以译码器为

2016-12-20 18:45:04

设计一个虚拟3-8译码器,实现138译码器的功能

2012-05-15 15:16:39

设计一个虚拟3-8译码器,实现138译码器的功能!急急急{:soso_e183:}

2012-05-15 15:12:44

PCM编译码器是数字通信中必不可少的部件,MT896X系列编译码器性能满足CCIT T 和ATT规范要求、且还有环回、测试等各种附加功能,片上还集成了4/5个独立的驱动器,可简化交换机用户环路

2009-04-23 14:22:40 20

20 主要介绍卷积编码器和Vertibi 译码器的基本原理。对用TMS320C54X DSP 来实现Vertibi译码器中的两个主要环节——度量值更新和回溯, 作了详细说明, 并给出具体的实现程序。

2009-05-15 16:22:43 21

21 本文基于Altera的FPGA(StatixⅡ-EP2S30F484C3)架构,实现了码率为1/2,帧长为1008bits的规则(3,6)LDPC码译码器。所采用的最小-和算法相对于传统的和-积算法在不损失译码性能的前提下,

2009-06-06 14:12:20 31

31 面向IEEE 802.16e 中 LDPC 码,分析了各种译码算法的译码性能,归一化最小(NMS)算法具备较高译码性能和实现复杂度低的特点。提出一种基于部分并行方式的LDPC 译码器结构,可以满

2009-08-05 08:46:59 24

24 基于对传统Viterbi 译码器的分析和对改进的Viterbi 算法理论的修正,提出了一种新的Viterbi 译码器的实现方法。通过对路径度量值的深入分析和对回溯信息的重新编码,在不增加硬

2009-08-13 10:43:19 23

23 本文利用可编程逻辑的灵活性和Nios 的强大处理能力,将多种编译码模块和微处理器模块集成到一片FPGA 内部,方便地实现了通用编译码器的设计。由于采用了VHDL 语言,使系统具有可移

2009-11-30 14:27:56 22

22 本文探讨了无线通信中广泛涉及的差错控制问题,介绍了卷积码的编译码原理。提出了一种卷积码编码,及其高速Viterbi 译码的实现方案,对译码的各个组成部分作了分析,并在FP

2010-01-06 15:06:59 12

12 本文探讨了无线通信中广泛涉及的差错控制问题,介绍了卷积码的编译码原理。提出了一种卷积码编码,及其高速Viterbi译码的实现方案,对译码的各个组成部分作了分析,并在FPGA中实现

2010-07-21 17:20:04 22

22 针对固定码长Turbo码适应性差的缺点,以LTE为应用背景,提出了一种帧长可配置的Turbo编译码器的FPGA实现方案。该设计可以依据具体的信道环境和速率要求调节信息帧长,平衡译码性

2010-11-11 16:07:59 26

26 译码器

译码是编码的逆过程,即将某个二进制翻译成电路的某种状态。实现译码操作的电路称为译码器。

2008-09-27 12:59:06 12538

12538

数码译码器的应用:译码器课件ppt

2008-12-17 14:31:20 1056

1056

基于BIST的编译码器IP核测

随着半导体工艺的发展,片上系统SOC已成为当今一种主流技术。基于IP复用的SOC设计是通过用户自定义逻辑(UDL)和连线将IP核整合

2008-12-27 09:25:39 794

794

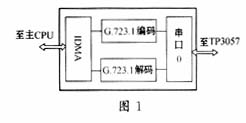

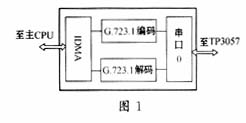

【摘 要】 介绍了ITU-TG.723.1标准语音编译码器的算法及其在ADSP-2181芯片上的实现 。软硬件结合实现了语音信号的采样和实时编译码,完全符合ITU-TG.723.1标准的定点算法

2009-05-10 19:54:11 1283

1283

译码器,译码器是什么意思

译码器是组合逻辑电路的一个重要的器件,其可以分为:变量译码和显示译码两类。 变量译码一

2010-03-08 16:32:18 5304

5304 译码器的工作原理及相关电路图分析

一般我们指的译码器是从一种数据表示形式转换为另一数据表示形式的器件。而指令的解析未必就是你说到的译码器可以解决

2010-03-08 16:40:17 23653

23653 Turbo码虽然具有优异的译码性能,但是由于其译码复杂度高,译码延时大等问题,严重制约了Turbo码在高速通信系统中的应用。因此,如何设计一个简单有效的译码器是目前Turb

2010-11-25 10:10:26 1772

1772

本文描述了一种可用于CDMA 2000 通信系统的通用高速维特比译码器基于FPGA的设计与实现。该维特比译码器具有通用性和高速性, 它支持可变码率、可变帧长的译码。同时它采用四个ACS 并

2011-05-14 15:18:14 33

33 该文介绍了两种Viterbi 译码器回溯译码算法,通过对这两种算法硬件实现结构上的优化,给出了这两种算法的FPGA 实现方法,比较了两种实现方法的优缺点。最后将其应用在实际的Viter

2011-05-28 15:18:48 33

33 本文设计实现了一种支持WIMAX标准的码长、码率可配置LDPC码译码器,通过设计一种基于串行工作模式的运算单元,实现了对该标准中所有码率的支持

2011-06-08 09:52:17 1766

1766

介绍了ITU-TG.723.1标准语音编译码器的算法及其在ADSP-2181芯片上的实现 。软硬件结合实现了语音信号的采样和实时编译码,完全符合ITU-TG.723.1标准的定点算法,通过了ITU-T的所

2011-07-06 09:49:07 1295

1295

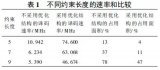

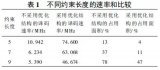

本文设计的译码器,利用Tail-biting卷积码的循环特性,采用固定延迟的算法与维特比算法结合,在FPGA上实现和验证,能达到135.78 MHz时钟

2011-08-05 11:57:37 4348

4348

卷积码是深度空间通信系统和无线通信系统中常用的一种差错控制编码。它克服了分组码由于以码块为单位编译码而使分组间的相关信息丢失的缺点。(2,1,8)卷积码在2G、3G通信系统

2011-10-12 15:05:59 1540

1540

本文介绍了 RS[ 255, 223 ]编译码器的 FPGA设计和基于线形反馈移位寄存器的编码器设计 , 以及由伴随式计算、关键方程求解、钱氏搜索、Forney算法等功能模块组成的译码器。为了实现简单

2012-05-22 10:43:40 45

45 介绍了符合CCSDS标准的RS(255,223)码译码器的硬件实现结构。译码器采用8位并行时域译码算法,主要包括了修正后的无逆BM迭代译码算法,钱搜索算法和Forney算法。采用了三级流水线结构实现

2013-01-25 16:43:46 68

68 动态显示-译码器片选实现【汇编版】动态显示-译码器片选实现【汇编版】动态显示-译码器片选实现【汇编版】

2015-12-29 15:51:29 0

0 动态显示-译码器片选实现【C语言】动态显示-译码器片选实现【C语言】动态显示-译码器片选实现【C语言】动态显示-译码器片选实现【C语言】

2015-12-29 15:51:36 0

0 截短Reed_Solomon码译码器的FPGA实现

2016-05-11 11:30:19 11

11 基于FPGA的3B4B编译码电路

2017-02-07 14:58:18 11

11 RS(ReedSolomon)编码是一种具有较强纠错能力的多进制BCH编码,其既可纠正随机错误,又可纠正突发错误。RS编译码器广泛应用于通信和存储系统,为解决高速存储器中数据可靠性的问题,文中

2017-10-17 11:21:32 46

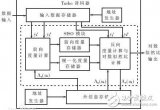

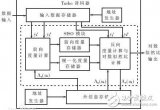

46 量化位数。然后基于该算法和这3个参数设计了一种全新的、高速部分并行的DSC译码器。该译码器最大限度地实现了译码效率、译码复杂度、FPGA资源利用率之间的平衡,并在Xilinx XC7VX485T芯片上实现了该译码器,其吞吐率可达197 Mb/s。

2017-11-16 12:59:01 2766

2766

该文通过对低密度校验(LDPC)码的编译码过程进行分析,提出了一种基于FPGA 的LDPC 码编译码器联合设计方法,该方法使编码器和译码器共用同一校验计算电路和复用相同的RAM 存储块,有效减少

2017-11-22 07:34:01 3928

3928

通过正确配置译码器的使能输入端,可以将译码器的位数进行扩展。例如,实验室现在只有3线- 8线译码器(如74138),要求我{ ]实现一个4线-16线的译码器。该如何设计呢?图1是其中的一种解决方案

2017-11-23 08:44:53 33058

33058

新一代移动通信系统目前主要采用多载波传输技术, 基带传输速率较3G 有很大提高, 一般要求业务速率能达到30 Mb/ s 以上。约束长度卷积码以及Viterbi译码器由于其性能和实现的优点

2019-10-06 10:16:00 2031

2031

本文首先介绍了译码器的定义与译码器的分类,其次介绍了译码器的作用和译码器的工作原理,最后介绍了译码器的逻辑功能。

2018-02-08 14:04:06 107559

107559

本文主要介绍了译码器的分类和应用。译码器指的是具有译码功能的逻辑电路,译码是编码的逆过程,它能将二进制代码翻译成代表某一特定含义的信号(即电路的某种状态),以表示其原来的含义。译码器可以分为:变量

2018-04-04 11:51:12 37755

37755

可编程逻辑技术的不断发展,其高密度、低功耗、使用灵活、设计快速、成本低廉、现场可编程和反复可编程等特性,使FPGA逐步成为Viterbi译码器设计的最佳方法。项目目的是用FPGA实现一个Viterbi译码器。

2019-04-24 08:29:00 2635

2635

信道的是二进制信号序列。为了充分利用信道输出信号的信息,提高传输系统译码的可靠性,首先把信道的输出信号量化,将Q电平量化序列输入Viterbi译码器,因此本文采用的VB译码算法为软判决译码算法。

2019-07-11 08:01:00 2822

2822

由网格图的输入支路特点分析可知,产生任意一个状态节点Si的输入条件mi是确定的,即mi=‘1’,i为偶数;mi=‘0’,i为奇数。输入条件mi表示译码器最终需要输出的比特信息。此外,译码器所要找的留选路径是不同状态的组合。

2018-10-02 01:07:16 5145

5145 本文档的主要内容详细介绍的是汉明码编译码器的数据手册免费下载。

2019-12-13 08:00:00 0

0 ,是卷积码的最佳译码方式,具有效率高、速度快等优点。从工程应用角度看,对Viterbi译码器的性能评价指标主要有译码速度、处理时延和资源占用等。本文通过对Viterbi译码算法及卷积码编码网格图特点的分析

2020-08-11 17:41:23 746

746

结构化LDPC码可进行相应扩展通过对编译码算法,优化编译码结构进行调整,降低了编译码嚣硬件实现中的关键路径迟延,并采用Xilinx公司的Virtex一4 VLX80 FPGA芯片实现了一个码长10 240,码率1/2的非正则结构化LDPC码编码器和译码器。实现结果表明:该编码器信息吞吐量为1.878 Gb/

2021-03-26 15:58:00 12

12 给出了跳频系统中 Turbo码译码器的FPGA( field programmable gate array)实现方案。译码器采用了MaxLog-map译码算法和模块化的设计方法,可以

2021-04-01 11:21:46 5

5 介绍并用VHDL语言实现了卷积编码和维特比译码。根据编码器特征设计了一种具有针对性的简洁的维特比译码器结构,

2021-05-12 15:22:41 2112

2112

基于FPGA的800Mbps准循环LDPC码译码器

2021-06-08 10:31:31 26

26 关于Actel 的FPGA的译码器的VHDL源代码(通信电源技术期刊2020年第14期)-关于Actel 的FPGA的译码器的VHDL源代码。适合感兴趣的学习者学习,可以提高自己的能力,大家可以多交流哈

2021-09-16 15:18:01 10

10 一听到三八译码器这个东西可能会感觉有点熟悉,其实在STC89C51系列单片机中,里面就有一个三八译码器,就是一开始的流水灯程序,LED0-7这八个LED!但是怎么在FPGA中实现三八译码器呢?其实很简单。

2023-04-26 15:38:21 1787

1787

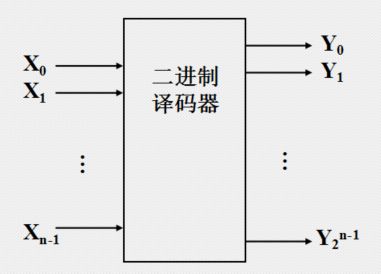

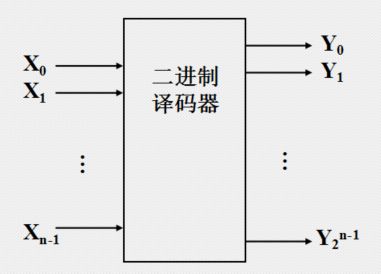

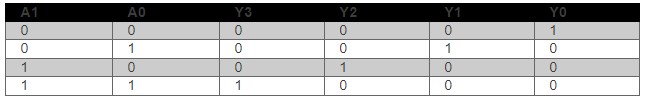

输入:二进制代码,有n个;

输出:2^n 个特定信息。

1.译码器电路结构

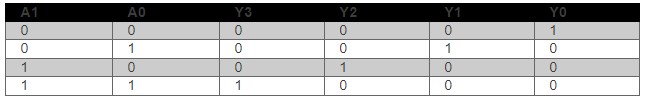

以2线— 4线译码器为例说明

2线— 4线译码器的真值表为:

2023-04-30 16:29:00 2335

2335

本次实验的任务是构建一个3-8译码器,且将译码结果通过小脚丫的LED灯显示。

2023-06-20 16:10:59 692

692

电子发烧友App

电子发烧友App

评论