觉得FIFO太贵了,对FPGA又一窍不通,能不能用74F系列的芯片做一个数据缓冲器之类的呢?麻烦各位前辈们给支个招儿

2014-05-10 17:19:09

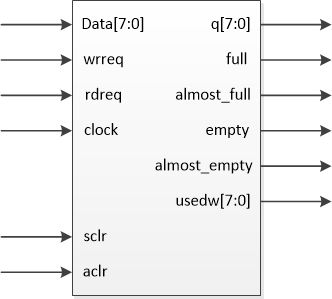

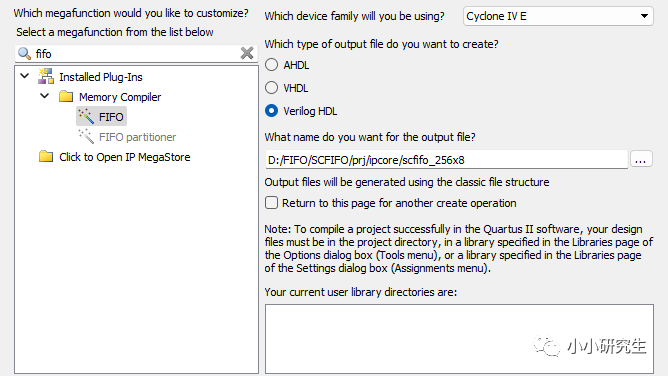

Verilog教程-郝旭帅团队 FIFO(first input first output或者first in first out),先入先出队列,是一种数字电路中常用的缓冲器,先进入的数据或者命令会

2023-03-15 16:19:35

基本知识:( 1 )数据缓冲器( SBUF )接受或发送的数据都要先送到 SBUF 缓存。有两个,一个缓存,另一个接受,用同一直接地址 99H, 发送时用指令将数据送到 SBUF 即可启动发送;接收

2022-01-13 06:08:33

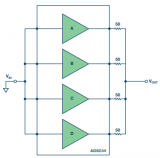

特征集成有源负载和1缓冲器增益;非常低的缓冲功耗;低至20兆瓦片上;利用GPO控制降低有功负载电流的节电特性;高速缓冲;400兆赫,-3分贝带宽;415V/μs转换速率;快速沉降时间为1%,2V步进

2020-10-14 16:51:55

(SLRD)读取不活跃,则缓冲器将是满的,并且不能写入更多的数据。一旦从奴隶FIFO开始读取,缓冲器将干净并准备好下一次传输。我的理解正确吗?我还想用I2S传送短命令到FPGA,但是我找不到这样的固件例子

2019-04-29 07:36:44

IT66318: HDMI2.0(6.0 Gbps)重定时缓冲器,用来为HDMI优化信号,应用在intel 600系等PC主板上。

IT66318是一种单进单出的 HDM I 2.0重定时缓冲器

2023-06-08 22:12:40

大家好!我正在做一个关于PSoC 4和Flash外部En25F80的使用SCB SPI的项目我有一些问题:首先,我将数据缓冲区写入到En25F80的地址中,然后再次读取数据缓冲器,但数据缓冲器不正确。请告诉我,帮帮我。非常感谢。这是我的计划:En25F80SoS.RAR1.6兆字节

2019-09-06 07:28:30

VISA读取缓冲器有多大,能存放多大的数据?

2016-05-20 16:13:25

如果在串口中断函数中,正在读缓冲区的中的数据(还没有读完),这个时候,串口又接收到新的数据,接收的数据量已经超过了FIFO的长度,会不会造成数据丢失呀

2024-01-17 08:14:53

`请问什么是音频缓冲器?`

2019-08-23 16:27:28

:具有内部BUF802的复合环路精密放大器结语BUF802等集成式Hi-Z缓冲器有助于解决基于复合环路实施的复杂难题。BUF802的集成保护功能(如输入/输出钳位)有助于保护信号链中的后续级,减少过驱

2022-11-03 07:56:17

我在使用 UART FIFO 缓冲区时遇到了以下问题。

问题描述:

当通过两个 UART 通道使用完整的 UART FIFO 缓冲区并通过两个通道进行通信时,缓冲区中的数据有时会损坏,例如,UART

2024-03-06 06:59:31

使用多缓冲器配置的DMA方式可以实现高速数据通信吗?

2021-12-08 06:06:14

高速、低功耗数据缓冲器为DDR5 DRAM及存储类内存模块提升速度与带宽

2020-11-24 06:58:15

刚刚接触KSZ8851以太网,在编程中发现 需要像发送缓冲器写入数据,然后以太网芯片将缓冲器中的数据发出,可是在资料中没有写发送缓冲寄存器地址,因此不知道如何进行写入。求指点

2016-10-26 09:22:03

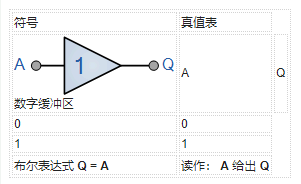

多个数字设备通过使用I / O信号和地址解码在同一数据总线上输入和输出数据。三态缓冲器可以单向和双向形式集成为四,六进制或八进制缓冲器/驱动器,如图所示,其中更常见的是TTL 74240,TTL 74244

2021-01-26 09:16:58

描述吉他缓冲器Guitar Buffer消除了长吉他电缆造成的信号损失,这是任何踏板的必备品。

2022-07-26 07:14:58

糟糕,只要在空标志不置位时不读取即可。Double Buffer我师傅让我考虑使用双端口block-ram 作为双缓冲器。就像 FIFO 一样,类似具有如下行为的读取器和写入器:写入器:将数据写入

2022-09-21 17:00:12

介绍了一种基于现场可编程门阵列(FPGA)和第二代双倍数据率同步动态随机存取记忆体(DDR2)的高速模数转换(ADC)采样数据缓冲器设计方法,论述了在Xilinx V5 FPGA中如何实现高速同步

2010-04-26 16:12:39

数据进入FPGA的速率高于传出的速率,持续的传输会造成数据的溢出,断续的传输可能会造成数据不连续。使用基于LabVIEW FPGA的DMA FIFO作为主控计算机和FPGA之间的缓存,若DMAFIFO深度设置的合适,FIFO不会溢出和读空,那么就能实现数据输出FPGA是连续的。

2019-10-12 09:05:54

如何去设计MP3播放器视频的输出部分?如何去解决超低功耗缓冲器应用的问题?

2021-04-20 06:02:33

如何去设计轨到轨CMOS模拟缓冲器?怎样对轨到轨CMOS模拟缓冲器进行仿真?

2021-04-23 06:35:57

fpga中提供的powerpc处理。所以现在我的自定义ip接管plb并通过dma事务它通过fifo从SDRAM获取数据,并根据从这个fifo状态机收到的信息将它分配给相应的引脚。我目前使用64 i / os

2020-07-20 07:07:12

中,一个时钟源要驱动多个器件,因此可使用时钟缓冲器(通常称为扇出缓冲器)来复制信号源,提供更高的激励电平。图 1. 使用扇出缓冲器创建大量单输入频率副本LMK00304 扇出缓冲器就是一个很好的例子

2022-11-21 07:25:28

。优势是显而易见的。由于BJT具有较高的电压额定值,泄露尖峰会高出几百伏特,不过仍然处于所要求的开关降额设计范围内。根据尖峰的幅度不同,常常有可能在不使开关过压的情况下完全移除缓冲器。移除缓冲器优点

2022-11-17 07:51:39

能否让低压放大器自举来获得高压缓冲器?

2021-03-16 14:31:58

见附件项目。我试图读取512字节的UART数据到一个带有DMA的缓冲区。没有DMA-手动将数据传输到缓冲器中,该设置工作良好,使用“中断”作为包启动的信号,但是DMA不将任何数据传送到缓冲器。知道我

2019-09-26 13:15:21

测量扇出缓冲器中的附加抖动怎么计算?

2021-05-06 07:02:23

应用于在旋转点需要减速的场合。 该类型的缓冲器具有免维护、装有集成限位挡块、安装即可使用的特点。加装偏心转接器配件可以允许有最高 25°的碰撞角。得益于其坚固的结构和长寿命,这类小型缓冲器有着广泛应用

2018-04-21 17:11:16

你好,我通过我的硬件流一些二进制数据,我想使最新的1000位可用的CPU在任何时间点按需。我想通过DMA不断填充缓冲来实现这一点。因此,我想要一个循环缓冲器或一个能够保持至少1000位的FIFO缓冲器(UIT8BUF(128)),是否可以在硬件中实现?有什么建议吗?

2019-09-11 12:58:18

很多大牛人见过不同的缓冲器,基于比较器的缓冲器,外部带有阻性纠错电路,它能增强高增益放大器的驱动能力,可以驱动像ADC前端电路中使用的开关电容负载。这种纠错机制使用了一个电阻,该电阻与充电路径和纠错

2021-04-02 07:32:16

嗨,当我们在FIFO或GPIF FIFO中讨论FIFO时,FIFO是终结点缓冲器吗?也就是说,如果使用奴隶FIFO,当外部CPU将一个字节写入从属FIFO时,CPU直接将字节写入端点缓冲器中,或者

2019-07-08 11:13:26

引脚置高后,输出就会保持现有的状态,直到把该引脚清0后才能继续变化。缓冲寄存器又称缓冲器,它分输入缓冲器和输出缓冲器两种。输入缓冲器的作用是将外设送来的数据暂时存放,以便处理器将它取走;输出缓冲器的作用

2022-03-01 07:00:42

与传统的时钟缓冲器相比,高速运算放大器有哪些优势?怎样去设计一个灵活的时钟缓冲器?

2021-04-14 06:35:37

大电流缓冲器

2019-10-31 09:11:09

描述贴片集成电路缓冲器

2022-06-28 06:31:00

`请问高速缓冲器是什么?`

2019-08-23 16:32:59

高性能专用集成电路供应商LOGIC Devices公司宣布已开始派送LF3312帧缓冲器/先进先出存储器(FIFO)的样品。该器件为设计者提供了灵活的存储器解决方案,以

2006-03-13 13:06:49 653

653

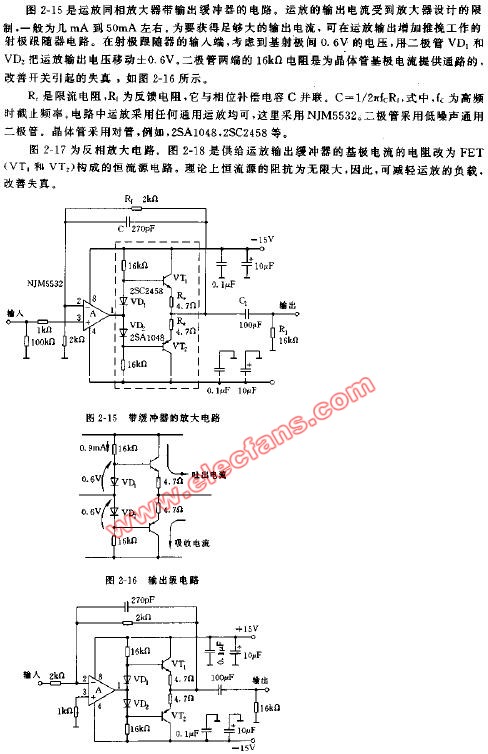

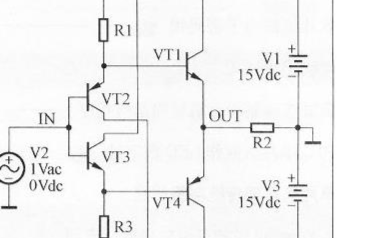

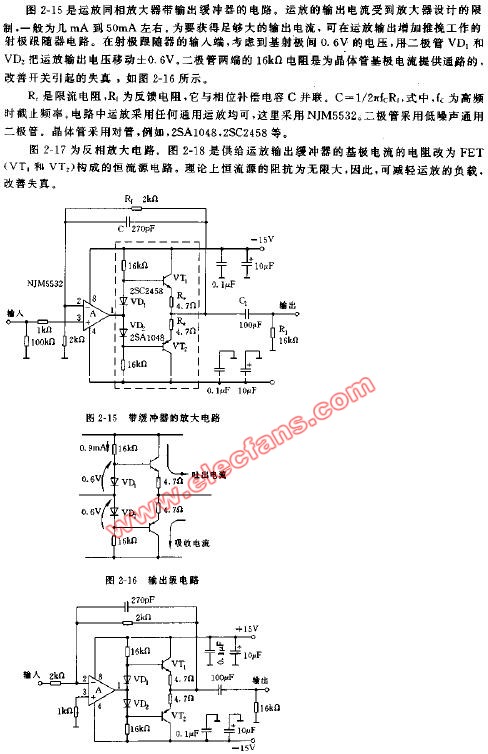

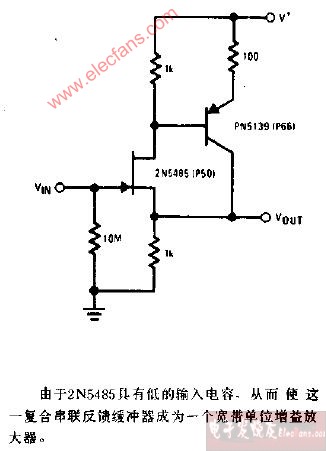

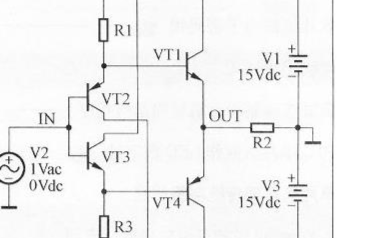

带缓冲器的放大电路

2008-12-17 01:42:14 957

957

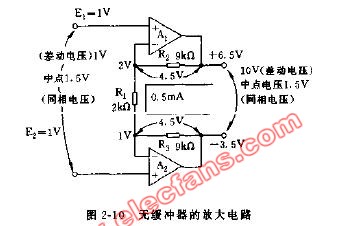

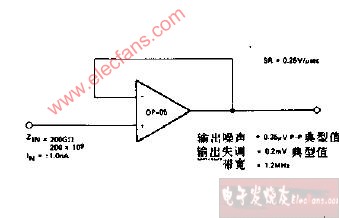

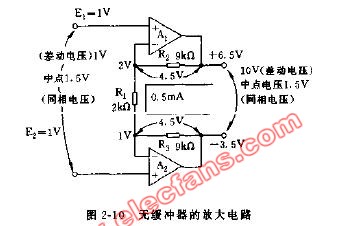

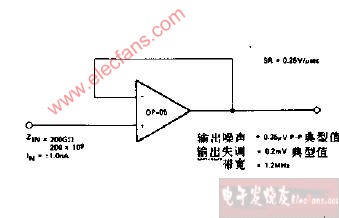

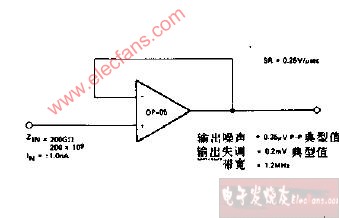

无缓冲器的放大电路图

2008-12-17 14:34:19 571

571

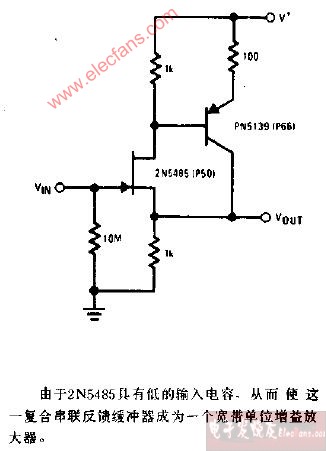

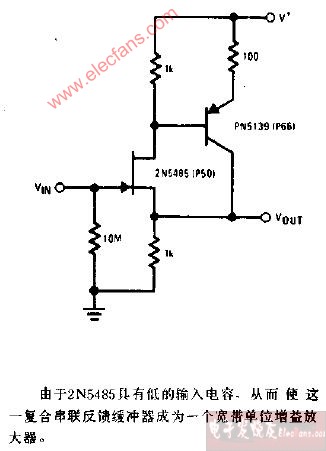

高阻宽带缓冲器电路图

2009-03-21 09:29:09 360

360

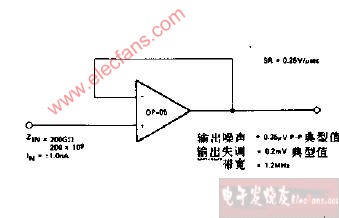

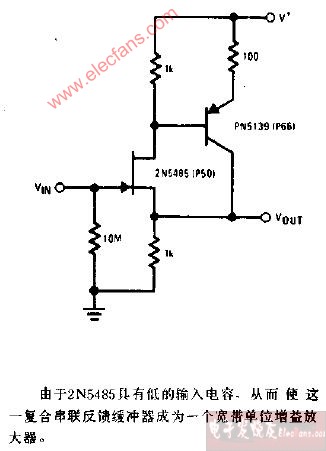

稳定的高阻缓冲器电路图

2009-03-21 09:30:27 824

824

高阻宽带缓冲器电路图

2009-03-24 09:57:22 751

751

稳定的高阻缓冲器电路图

2009-03-24 09:57:45 981

981

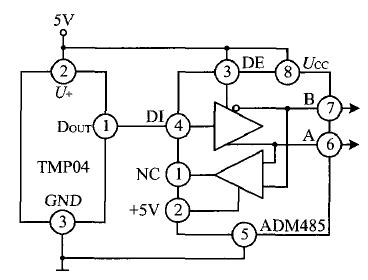

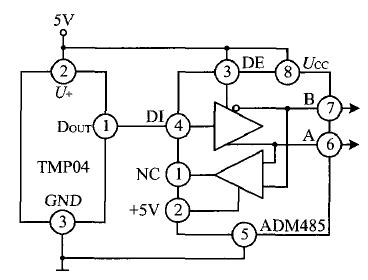

加外部缓冲器的远程测温电路

加外部缓冲器的远程测温电路由

2009-08-23 21:31:26 834

834

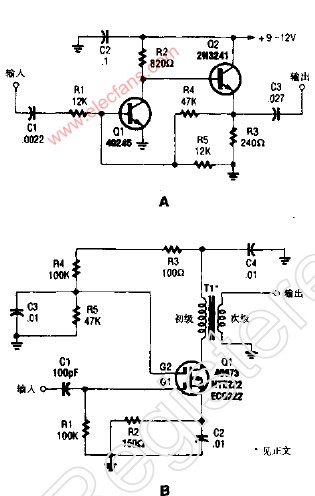

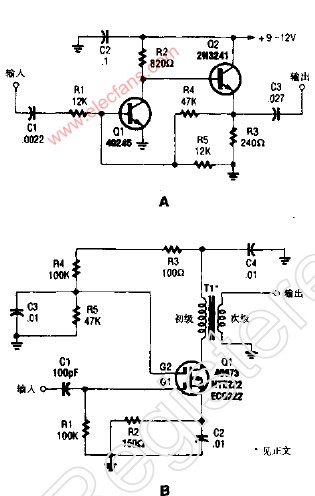

缓冲器/放大器

这里给出两中缓冲/

2009-09-11 10:44:22 1295

1295

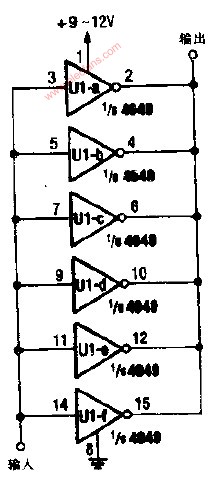

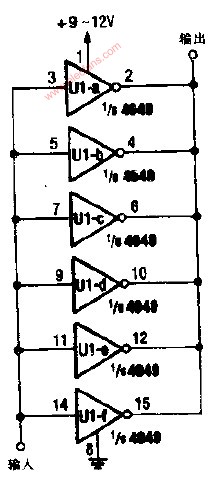

大电流缓冲器

通过4049非门

2009-09-11 10:47:50 3043

3043

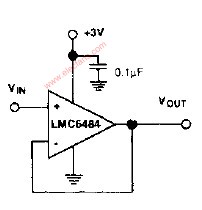

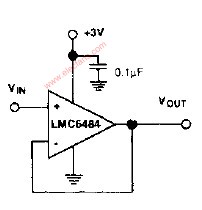

3V峰到峰单电源缓冲器

该

2009-09-11 10:58:27 694

694

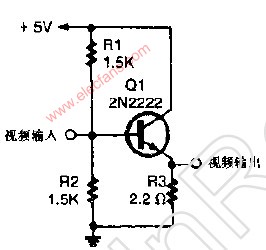

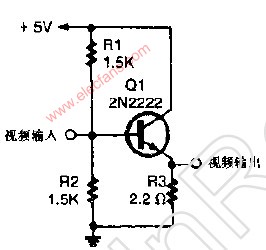

简易视频缓冲器

这是一以和发射极

2009-09-11 11:02:33 706

706

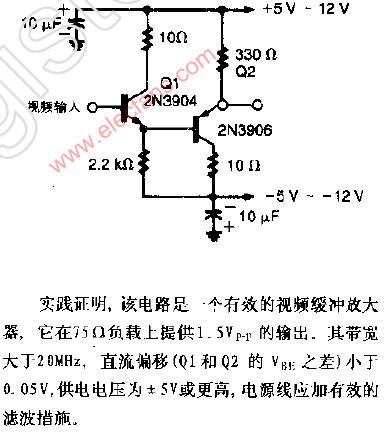

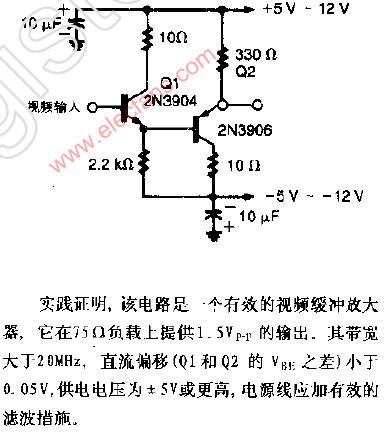

低偏移简易视频缓冲器

2009-09-11 11:05:37 487

487

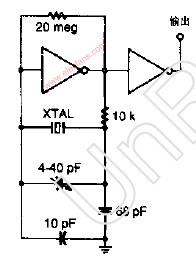

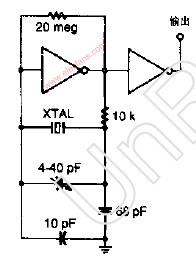

六缓冲器的晶体振荡器

4049集成块的以个单独部分是晶体

2009-09-14 11:20:37 620

620

缓冲器,缓冲器是什么?

buffer 中文译名: 缓冲,缓冲器,缓冲液 解释:1、 电信设备。在数据传输中,用来弥补不同数据处

2010-03-08 13:30:11 2253

2253 缓冲器,缓冲器基本原理是什么?

最基本线路构成的门电路存在着抗干扰性能差和不对称等缺点。为了克服这些缺点,可以在输出或输

2011-09-03 19:10:46 9258

9258 本文采用VHDL描述语言,充分利用Xilinx公司Spartan II FPGA的系统资源,设计实现了一种非对称同步FIFO,它不仅提供数据缓冲,而且能进行数据总线宽度的转换。

2011-01-13 11:33:43 1744

1744 摘要:介绍了一种基于现场可编程门阵列(FPGA) 和第二代双倍数据率同步动态随机存取记忆体(DDR2) 的高速模 数转换(ADC) 采样数据缓冲器设计方法,论述了在Xilinx V5 FPGA 中如何实现高速同步

2011-03-31 16:38:08 139

139 ADI数字加速度计中先进先出(FIFO)缓冲器的使用

2011-11-28 15:08:27 0

0 三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器

2015-11-16 11:59:30 0

0 许多电子电路需要利用一个器件来将不同的电路隔离或分离开。这种特殊器件称为缓冲器。缓冲器是单位增益放大器,具有极高输入电阻和极低输出电阻。

2017-09-18 17:14:37 7

7 三态数据缓冲器是数据输入/输出的通道,数据传输的方向取决于控制逻辑对三态门的控制。本文介绍三态缓冲器的逻辑符号。

2018-01-11 10:42:36 13971

13971

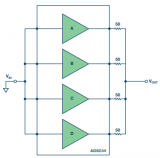

想要降低系统中增加的噪声,必须降低电压噪声。常用方法——并联放置多个缓冲器可降低电压噪声。但是,该方法会使偏置电流、电流噪声、输入电容,统统提高,这时,你需要一款4通道JFET缓冲放大器! 缓冲器是什么? 许多电子电路需要利用一个器件来将不同的电路隔离或分离开。

2018-05-27 05:13:00 14889

14889

本文开始介绍了缓冲器和集成电路的概念,其次阐述了集成电路在各方面的应用,最后对接口集成电路中的缓冲器和集成电路中缓冲器的作用进行了介绍。

2018-03-26 14:12:08 24270

24270 缓冲器安装在井道底坑内,要求其安装牢固可靠,承载冲击能力强,缓冲器应与地面垂直并正对轿厢(或对重)下侧的缓冲板。缓冲器是一种吸收、消耗运动轿厢或对重的能量,使其减速停止,并对其提供最后一道安全保护的电梯安全装置。

2018-11-29 17:22:40 39082

39082 起重机是一种重型机械,作业时产生的惯性也较大,容易产生意想不到的动作,所以,起重机缓冲器在这时候就起到作用了,起重机缓冲器是吸收起重机的运行动能,以减缓冲击的,起重机缓冲器作用及类型都十分广泛。

2018-12-04 15:45:15 10510

10510 液压缓冲器是一种安全缓冲装置,它能够对作用在它上面的物体进行减速缓冲直至停止,这样就会对作用的物体起到一定的保护作用。液压缓冲器性能优秀,在许多行业和产品里都有使用,比如运输、港口机械、电梯、冶金等行业。液压缓冲器有如下几个明显的优点。

2018-12-16 10:05:03 7626

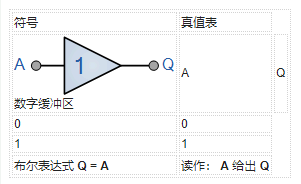

7626 数字缓冲器和三态缓冲器可在数字电路中提供电流放大,以驱动输出负载,与单输入,单输出逆变器或 NOT TTL 7404的门,它在输出上反转或补充其输入信号,“缓冲器”不执行反转或决策制作功能(如具有

2019-06-26 12:02:27 14103

14103

LTC4302: 可寻址双线式总线缓冲器 数据手册

2021-03-19 12:44:43 9

9 AN-1275: ADF7023上的滚动数据缓冲器

2021-03-19 13:28:01 3

3 AD8195:带均衡数据表的HDMI/DVI缓冲器

2021-04-14 10:03:24 1

1 集成缓冲器的18位八进制SAR ADC

2021-04-21 08:54:29 3

3 AN4-新型功率缓冲器的应用

2021-04-29 17:50:37 9

9 ADD8701:带VCOM缓冲器的12通道伽马缓冲器数据表

2021-05-08 12:28:26 3

3 ADD8702:带VCOM缓冲器的12通道伽马缓冲器数据表

2021-05-09 19:58:57 11

11 HMC6832:低噪声、2:8差分扇出缓冲器数据表

2021-05-25 09:34:37 4

4 带均衡数据表的AD8195 HDMIDVI缓冲器

2021-06-18 10:34:10 5

5 缓冲器分为输入缓冲器和输出缓冲器两种;输入缓冲器的作用是将外设送来的数据暂时存放,以便处理器将它取走,输出缓冲器的作用是用来暂时存放处理器送往外设的数据。 缓冲器的工作原理: 当液压缓冲器受到

2021-08-25 17:31:25 22729

22729 缓冲寄存器又称缓冲器,它分输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设的数据。有了数控缓冲器,就可以使高速工作的CPU

2021-08-31 17:37:53 9948

9948 FIFO是在FPGA设计中使用的非常频繁,也是影响FPGA设计代码稳定性以及效率等得关键因素。在数据连续读取时,为了能不间断的读出数据而又不导致FIFO为空后还错误的读出数据。可以将FIFO

2021-09-09 11:15:00 6293

6293 IDT 还提供另一个更简单的 CMOS 缓冲器系列,即5PB11xx系列,由五个时钟扇出缓冲器成员组成,其中最后两位数字代表输出数量。这些缓冲器是非常高性能、低抖动、低偏移和传播延迟、非常低功耗的直接 CMOS 扇出缓冲器。

2022-05-05 15:41:13 1500

1500

电子发烧友网站提供《贴片集成电路缓冲器.zip》资料免费下载

2022-07-04 10:21:44 2

2 什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析 什么是时钟缓冲器(Buffer)?我们先把这个概念搞清楚。 时钟缓冲器就是常说的Clock Buffer,通常是指基于非PLL

2022-10-18 18:36:54 18409

18409

buffer缓冲器电路图与buffer电路示意图 buffer缓冲器的作用 buffer译名为: 缓冲,缓冲器,缓冲液; buffer缓冲器的作用是什么? 比如在数据传输中,用来弥补不同数据处理速率

2022-10-18 19:01:54 27720

27720

设计 RC 缓冲器-AN11160

2023-02-07 19:00:18 4

4 低功耗单缓冲器;带漏极开路的单缓冲器-74AUP2G3407

2023-02-10 18:48:10 0

0 双电源单缓冲器和带漏极开路的单缓冲器-74AXP2T3407

2023-03-03 19:51:09 0

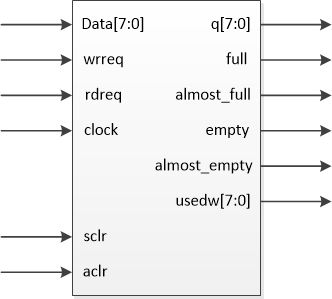

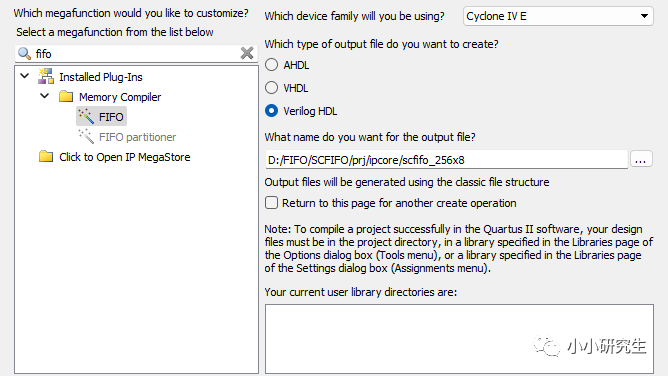

0 在FPGA中,FIFO一般是使用RAM存储器作为缓冲区,可以分为同步FIFO或异步FIO,一般用于数据缓冲,或者不同时钟域之间的数据传递。

2023-04-10 09:30:10 539

539 液压缓冲器强度是否能够调节,取决于液压缓冲器的种类,目前市面上较为常用的液压缓冲器包括可调液压缓冲器、不可调液压缓冲器,这两种缓冲器调节强度的实际效果是不一样的。

2023-04-24 16:12:01 2158

2158 时钟缓冲器选型目录

2021-11-19 16:38:53 789

789

FIFO,先进先出。在FPGA中使用的FIFO一般是指对数据的存储具有先进先出的缓冲器,FIFO与普通的存储器的不同在于它没有读写地址线。举个例子,当FPGA从外部传感器读取到一连串数据时,首先

2023-07-23 11:47:03 369

369

FIFO(First In First Out, 先入先出 ),是一种数据缓冲器,用来实现数据先入先出的读写方式。数据按顺序写入 FIFO,先被写入的数据同样在读取的时候先被读出,所以 FIFO存储器没有地址线,有一个写端口和一个读端口。

2023-09-07 18:30:11 821

821

三态输出的缓冲器有哪些用途? 三态输出缓冲器是一种电子元件,其主要作用是将一个输入信号转换成一个可以控制多个输出设备的信号。这种缓冲器可以被用于一系列的应用,包括数码电路、计算机、消费电子设备、通信

2023-09-21 15:55:36 1607

1607

电子发烧友App

电子发烧友App

评论