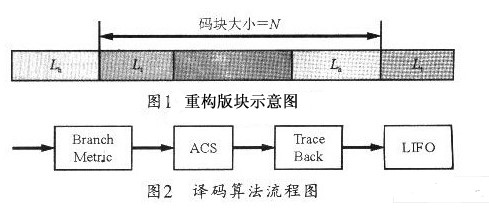

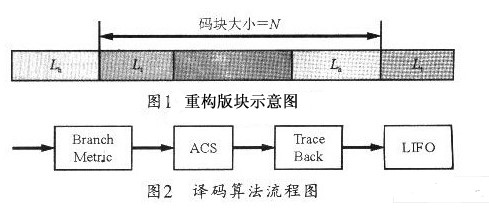

咬尾卷积码的原理是尾卷积码保证格形起始和终止于某个相同的状态。它具有不要求传输任何额外比特的优点。

2018-08-21 09:11:53 6663

6663

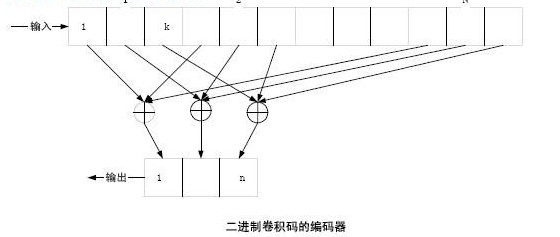

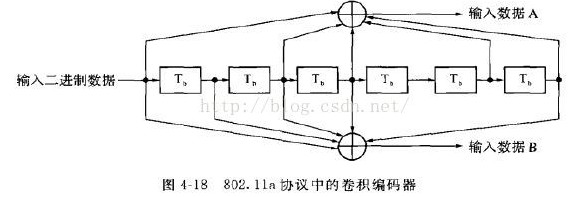

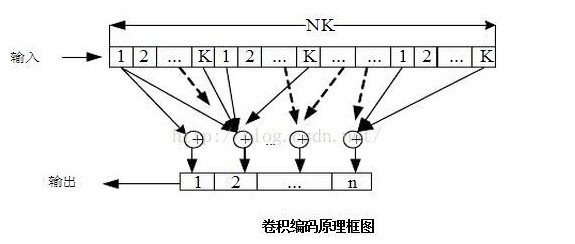

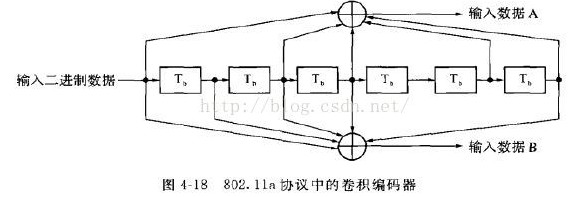

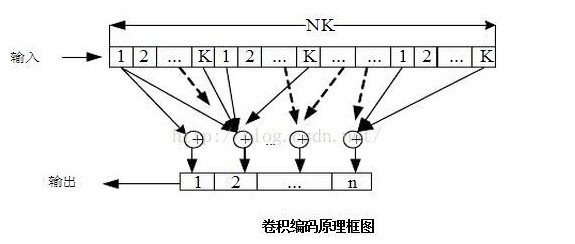

卷积码将k个信息比特编成n个比特,但k和n通常很小,特别适合以串行形式进行传输,时延小。

2018-08-21 09:36:40 13932

13932

800Mbps准循环LDPC码编码器的FPGA实现引言低密度校验码肠 ,码 由于其接近香农限的纠错性能,使得其成为当前信道编码的研究热点。 码面临的一个关键问题是其较高的编码复杂度和编码时延。 形耐

2012-08-11 11:44:45

请问各位大神,我想问一下用FPGA做卷积码有什么注意的地方?

2015-04-07 12:57:40

刚刚学习fpga方面的知识,fpga如何测量一个增量式编码器,消除抖动的话是否也是在上升沿和下降沿都进行计数处理,这样的话怎样设定可以保障计数器可以同时在两个always 下进行计数,可以给一下大概的例程最好

2016-01-11 18:27:47

的QPSK OFDM编码光信号,并成功地在标准单模光纤中传输了200 km,和没有采用卷积码的相比,系统的误码性能获得明显提高。在误码率10-3时,可节省1 dBm左右的光功率。实验结果表明,卷积码可应用

2010-04-23 11:30:18

前位置偏离原点的位置数据信息,是称绝对式,英文叫做Absoulute。比如,一款10 位BCD 码输出的编码器分辨率为360C/T,那么每个单位对应1°,如果轴偏离原点一个单位,也就是处在1°的位置

2012-02-24 22:03:25

每组代码具有一特定的含义(代表某个数字或控制信号)称为编码。具有编码功能的逻辑电路称为编码器。编码器有若干个输入,在某一时刻只有一个输入信号被转换成为二进制码。如果一个编码器有N个输入端和n个输出端,则

2019-10-13 08:00:00

编码器的原理是什么?编码器可分为哪几类?编码器是如何进行接线的?编码器软件四倍频技术是什么?

2021-08-04 06:08:39

编码器是什么?编码器工作原理是什么?

2021-10-19 09:59:08

型) 绝对编码器光码盘上有许多道光通道刻线,每道刻线依次以2线、4线、8线、16 线……编排,这样,在编码器的每一个位置,通过读取每道刻线的通、暗,获得一组从2的零次方到2的n-1次方的唯一的2进制编码

2017-11-24 19:00:47

)称为编码。具有编码功能的逻辑电路称为编码器。编码器有若干个输入,在某一时刻只有一个输入信号被转换成为二进制码。如果一个编码器有N个输入端和n个输出端,则输出端与输入端...

2021-09-03 06:35:59

最近公司项目用到了编码器选用的编码器 为360脉冲为了方便其一圈发360个脉冲 ,当然精度只有一度 ,如果为了高精度可以选用其他类型的首先简述一下编码器的工作原理编码器可按以下方式来分类。1、按码盘

2021-07-12 06:39:50

位(通常是码盘最外侧的码道表示最低位,最内侧的码道表示最高位)。 码道的数量决定了二进制编码的位数,一个绝对式编码器有N 条码道,则它输出二进制数的总个数是2的N次方个。 读取这些二进制码就能知道设备

2023-03-30 14:57:12

芯片为硬件平台,以Max+PlusⅡ为软件平台,以VHDL为开发工具,适合于CPLD实现的CMI编码器的设计方案。 1 CMI码的编码规则 CMI编码规则如表1所示。 在

2010-08-09 18:24:16

本文以战术军用通信系统的首选码RS(31,15)码为例,对生成多项式进行了优化,并采用查表法的原理极大地提高了编码器运算数据的能力,缩短了运算周期,最终利用VHDL语言编译,在FPGA中实现,得到了正确的RS编译码。

2021-05-06 09:27:33

。由此,大大节约了程序的存储空间,减少了程序的调试时间。文章将用VHDL设计八种常用的编码方式,并运用ALTERA公司的QUARTUSII设计软件进行仿真调试。QUARTUSII设计软件是一款开放

2015-01-29 14:11:42

成随机错误,为正确译码创造了更好的条件。从严格意义上说,交织不是编码,因为交织技术本身不产生冗余码元;但是如果把编码器和交织器看成一个整体,则新构成的“交织码”具有了更好的纠错性能。什么是分组交织

2008-05-30 16:13:49

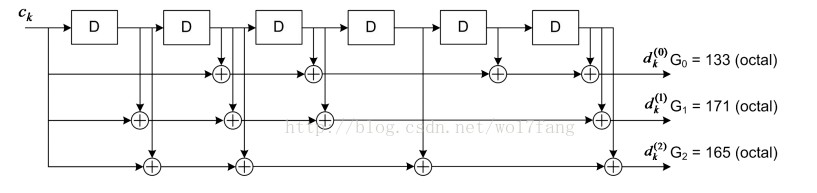

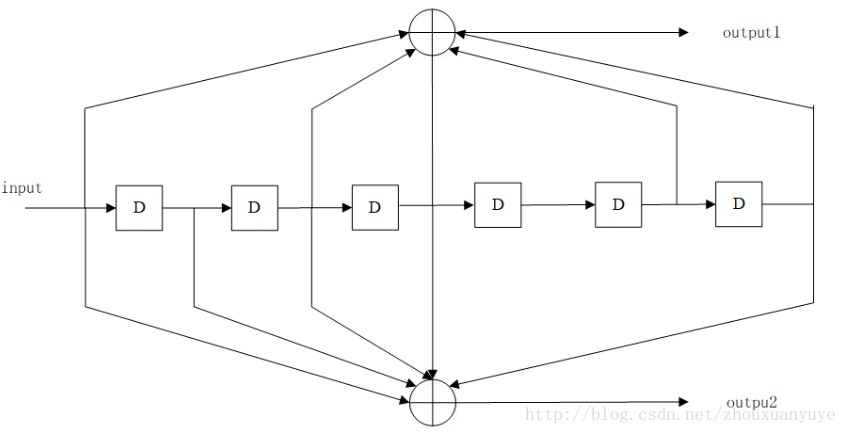

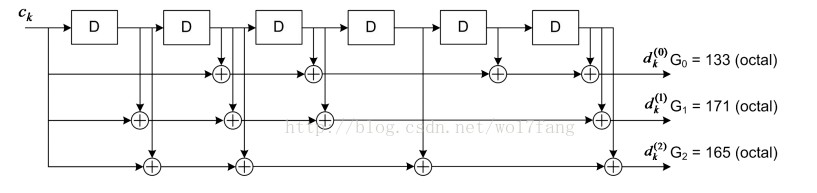

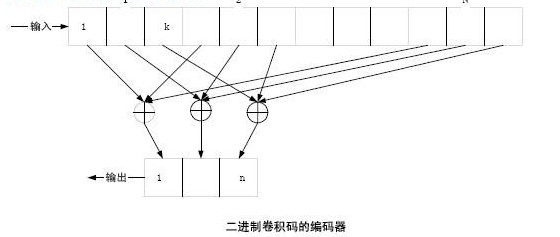

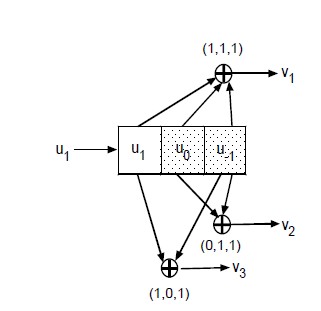

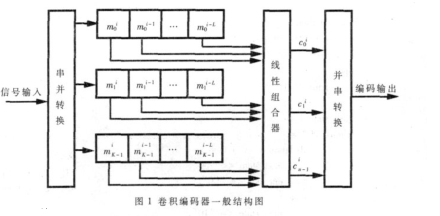

和复杂性相同的条件下,卷积码的性能优于分组码。但卷积码没有分组码那样严密的数学结构和数学分析手段,目前大多是通过计算机进行好码的搜索。什么是卷积码的约束长度?二进制卷积码编码器的形式如下图所示,它包括一个由

2008-05-30 16:06:52

(IRQ)和混合纠错(HEC)等方式,其基本特征是信道编码构造简单,需要反馈信道;另一类称为前向纠错(Forward Error Correction,FEC)方式,所谓“前向”,是指译码器根据码的规律性

2008-05-30 16:00:32

在编码和译码方面的基本思想,出现了形形色色的各种采用 Turbo(迭代)译码算法的纠错编码,使得信道编码学提到到了一个崭新的程度,越来越逼近 Shannon 限。这些码有:(1) Turbo 并行级联

2008-05-30 16:24:49

。由此可见,级联码适用于组合信道。由于内码译码器的错误往往是连续出现的,一般在内外编码器之间需要一个交织器,接收端也相应地增加反交织器。级联码的组合方式很多,如外码采用RS 码,内码用二进制分组码或卷积码

2008-05-30 16:16:10

是利用码盘上的刻线,转动的时候输出的一个个的脉冲数记录数值的,所以我们一般也叫光电编码器为角位移传感器,而且是数字信号的角位移传感器。 编码器都叫角位移传感器了,又怎么会出现线性编码器呢,是因为我们

2019-12-17 11:22:04

我买了一块FPGA学习开发板,我现在想用开发板去外接一个编码器,使用开发板去计编码器的圈数并显示在开发板上的数码管上,我该如何将编码器外接到开发板上?需要外接电路?设计外接电路的方针是?

2015-01-12 22:47:17

哪位大神给个基于FPGA的IR接收器VHDL语言的程序

2017-05-20 20:43:57

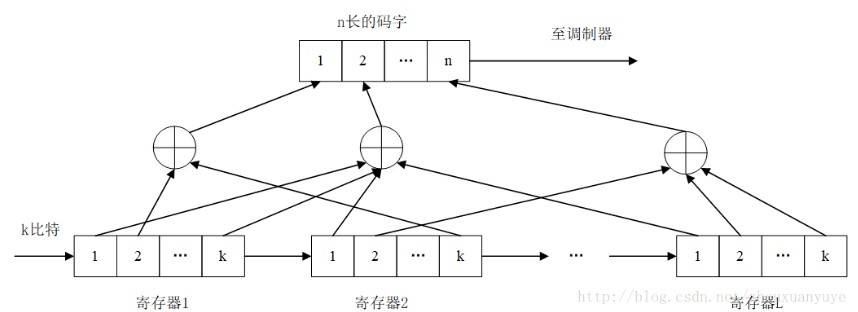

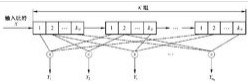

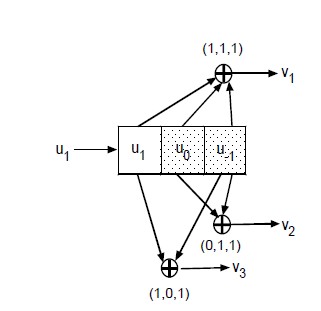

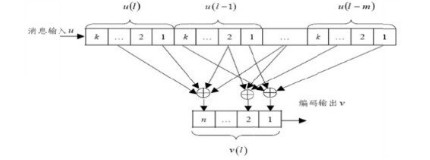

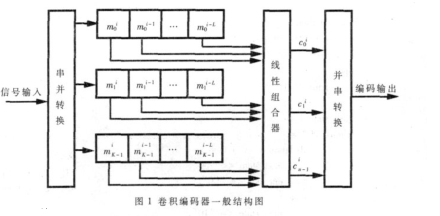

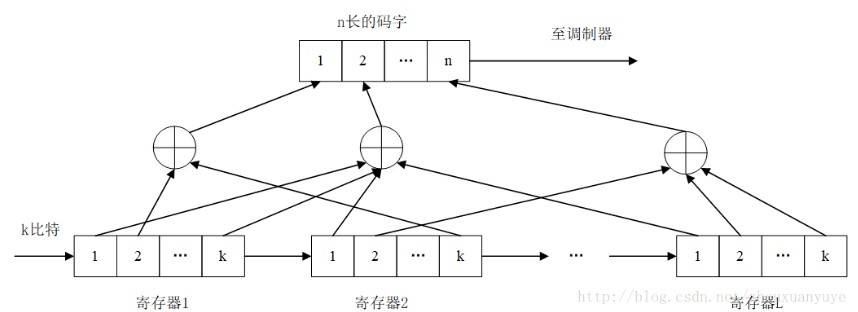

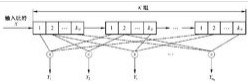

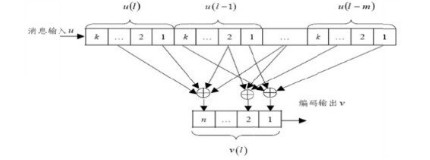

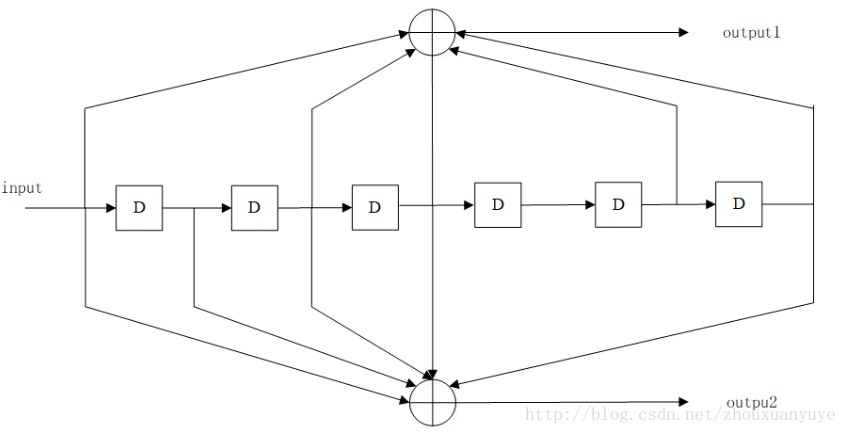

卷积码编码器的形式如下图所示,它包括一个由N 个段组成的输入移位寄存器,每段有k 个寄存器;一组n 个模2 相加器和一个n 级输出移位寄存器。对应于每段k 个比特的输入序列,输出n 个比特。由图中可以看到

2008-05-28 15:03:31

出现的,一般在内外编码器之间需要一个交织器,接收端也相应地增加反交织器。级联码的组合方式很多,如外码采用RS 码,内码用二进制分组码或卷积码;或内外码都采用卷积码 (当内码译码输出软信息时)。我们很

2008-05-28 15:09:03

由于卷积码优良的性能,被广泛应用于深空通信、卫星通信和2G、3G移动通信中。卷积码有三种译码方法:门限译码、概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法,是卷积码的最佳译码方式,具有效率高、速度快等优点。

2019-11-01 08:05:38

对不同的设计方法进行分析和比较,选择优化的设计方法,利用VHDL分别设计(15,7)BCH码的编码器和译码器,并能够对两部分进行单独仿真调试,实现其相应的功能。

2012-05-10 11:36:06

编码器实现指标分析LDPC码编码器实现编码器方案验证与优缺点分析

2021-04-30 06:08:10

求助!大佬们,问一下用FPGA实现卷积码编解码的难度。

2023-10-16 23:26:26

利用现场可编程门阵列(FPGA)和VHDL 语言实现了PCM码的解调,这样在不改变硬件电路的情况下,能够适应PCM码传输速率和帧结构变化,从而正确解调数据。

2021-05-07 06:58:37

什么是H.264视频编码技术?如何去实现并优化一种H.264视频编码器?

2021-06-03 07:00:52

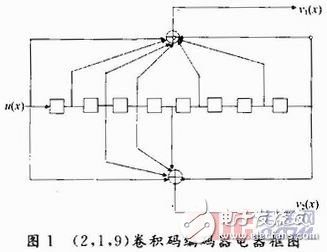

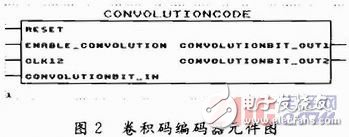

为了缩短卷积编码器设计周期,使硬件设计更具灵活性,在介绍卷积编码器原理的基础上,论述了一种基于可编程逻辑器件,采用模块化设计方法,利用VHDL硬件描述语言实现CDMA2000系统前向链路卷积编码器

2019-08-27 07:41:05

由于卷积码具有较好的纠错性能,因而在通信系统中被广泛使用。采用硬件描述语言VerilogHDL或VHDL和FPGA(FieldProgrammableGateArray——现场可编程门阵列)进行数字通信系统设计,可在集成度、可靠性和灵活性等方面达到比较满意的效果。

2019-10-14 06:02:23

安川伺服在使用绝对值编码器时如何选用电池?

2021-10-11 06:28:48

如何使用VHDL语言设计卷积码编解码器?

2021-04-29 06:39:03

使用光电旋转编码器有A、B两相。要达到的效果是:光电旋转编码器能够判定正反转,按键控制光电旋转编码器的电源,按键按下,光电旋转编码器上电,按键松开,光电旋转编码器掉电,只有在按键按下并且码盘转动

2018-07-30 09:09:58

本人小菜鸟,开始学FPGA的时候学的Verilog语言,后来因为课题组前期的工作都是VHDL就该学VHDL了。最近听了几个师兄的看法,说国内用VHDL的已经很少了,建议我还是坚持用Verilog,小菜现在好纠结,请问到底应该用哪种语言呢?望各位大神指点!

2015-07-08 10:07:56

最近在做扩频调制,有没有Labview编的gold码生成VI以及RS编码和卷积编码的VI啊?

2015-05-10 14:47:26

1. 正交编码器原理码盘:正交编码器有两个光电传感器,另一头有一个光源,当黑白相间的码盘转到白色对准光电传感器时,光电传感器发出一个脉冲。AB之间相隔的角度往往是90°的相位,即白格或者黑格的一

2021-08-12 07:10:00

本文详细介绍了一个测量各类海德汉编码器的数据的通用且实用的模块。该模块基于Xilinx FPGA平台和TI DSP平台,使用和调试方便,使用者可快速掌握;通过了实验和精度的检测,实现了设计目的,工作可靠;模块小巧,可以与上位机通信,可以很好的被结合到嵌入式系统中。

2021-04-30 07:01:32

该如何选用编码器呢?定位系统如何实现?

2020-03-22 20:24:46

栅条组成。位置信息通过计算自某点开始的增量数(测量步距数)获得。由于必须用绝对参考点确定位置值,因此圆光栅码盘还有一个参考点轨。 2、绝对式 绝对式编码器就是对应一圈,每个基准的角度发出一个唯一与该

2016-06-27 16:43:31

Turbo码编码器的FPGA实现Turbo码译码器的FPGA实现Turbo码编译码器的性能有哪些?

2021-05-07 06:06:23

绝对编码器会直接输出正在测量的轴的确切位置。每个旋转点都具有唯一的位置值或数据字,并在随轴一起旋转的码盘上编码。码盘上唯一代码的数量决定了位置的表示精度。编码器一旦开启,便立即使用光学、电容式或磁性

2018-12-20 16:31:09

为了实现多对极磁电式轴角编码器的高分辨率绝对式检测并降低其成本,基于改进格雷码构建了一种新型多极磁电轴角编码器模型,提出一种基于校准查表的信号处理方式,以消除磁场非线性和装配误差对测量精度

2010-06-02 10:04:24

如何用Verilog设计密勒码编码器,求大神指教!

2019-09-24 16:56:32

,不宜实现小型化。增量式光电编码器不具有计数和接口电路,一般输出A、B、Z脉冲信号,价格较低,在实际工程中比较常用。文中设计了一个基于FPGA的简单且精度高的接口电路,其结构简单、性能可靠。具有滤波

2019-06-10 05:00:08

汉明纠错吗编码器实例(VHDL源代码):

2009-05-27 10:11:15 43

43 卷积码是一种性能优良的差错控制编码。本文阐述了卷积码编解码器的基本工作原理,在MAX+PLUS2 软件平台上,给出了利用复杂可编程逻辑器件设计的(2,1,6)卷积码编解码器电路

2009-08-10 08:39:06 24

24 EDA卷积码编解码器实现技术针对某扩频通信系统数据纠错编码的需要, 构造并分析了(2 , 1 , 6) 卷积码编解码器的基本工作原理, 提出了基于MAX + plus Ⅱ开发平台的(2 , 1 ,

2009-12-05 16:17:42 0

0 本文探讨了无线通信中广泛涉及的差错控制问题,介绍了卷积码的编译码原理。提出了一种卷积码编码,及其高速Viterbi 译码的实现方案,对译码的各个组成部分作了分析,并在FP

2010-01-06 15:06:59 12

12 本文探讨了无线通信中广泛涉及的差错控制问题,介绍了卷积码的编译码原理。提出了一种卷积码编码,及其高速Viterbi译码的实现方案,对译码的各个组成部分作了分析,并在FPGA中实现

2010-07-21 17:20:04 22

22 本文重点研究了AVS-P2熵编码器的算法、结构以及利用FPGA实现的若干关键问题,给出了详细的块变换系数熵编码器硬件结构,并通过了仿真验证。实现中提出了一种新的2D-VLC码表存储

2010-08-06 16:37:38 24

24 对光码分多址(OCDMA)的误码特性和卷积码进行研究,根据两者的特点提出了一种新的基于OCDMA多址干扰信道模型的卷积码译码方法。针对这种新型卷积码译码方法的抗误码性和译

2010-08-26 16:40:22 17

17 【摘 要】 通过设计实例详细介绍了用VHDL(VHSIC Hardware DescriptionLanguage)语言开发FPGA/CPLD的方法,以及与电路图输入和其它HDL语言相比,使用VHDL语言的优越性。

2009-05-10 19:47:30 1111

1111

编码器,编码器是什么意思

编码器

编码器(encoder)是将信号

2010-03-08 15:04:26 2868

2868 卷积码/Viterbi译码,卷积码/Viterbi译码是什么意思

卷积码在一个二进制分组码(n,k)当中,包含k个信息位,码组长度为n,每个码组的(

2010-03-18 14:09:21 2219

2219 卷积码,卷积码是什么意思

卷积码在一个二进制分组码(n,k)当中,包含k个信息位,码组长度为n,每个码组的(n-k)个校验位仅与本码组的k个信息

2010-03-19 16:46:24 1656

1656 卷积码,什么是卷积码

卷积码在一个二进制分组码(n,k)当中,包含k个信息位,码组长度为n,每个码组的(n-k)个校验位仅与本码组的k个信息位

2010-04-03 12:11:06 6923

6923 本文设计的译码器,利用Tail-biting卷积码的循环特性,采用固定延迟的算法与维特比算法结合,在FPGA上实现和验证,能达到135.78 MHz时钟

2011-08-05 11:57:37 4348

4348

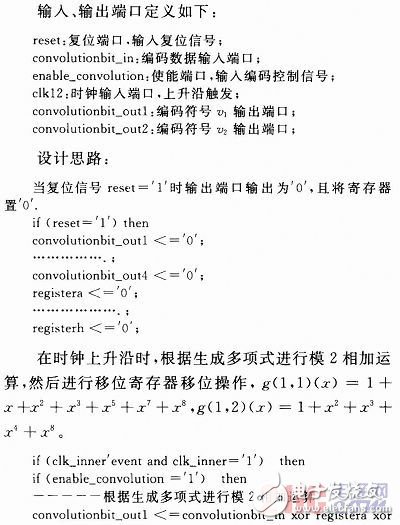

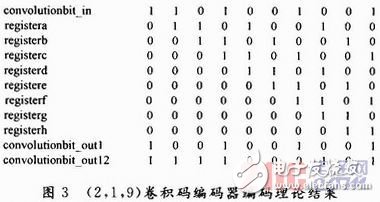

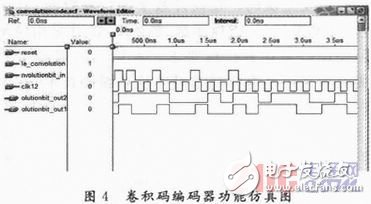

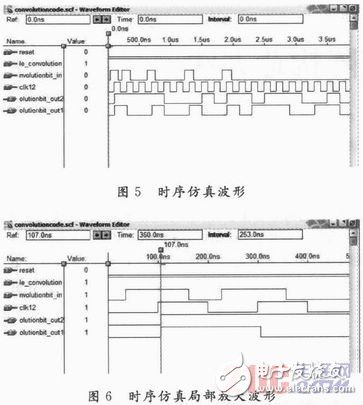

卷积码是深度空间通信系统和无线通信系统中常用的一种差错控制编码。它克服了分组码由于以码块为单位编译码而使分组间的相关信息丢失的缺点。(2,1,8)卷积码在2G、3G通信系统

2011-10-12 15:05:59 1540

1540

分析了光电编码器4倍频原理,提出了一种基于可编程逻辑器件FPGA对光电增量式编码器输出信号4倍频、鉴相、计数的具体方法,它对提高编码器分辨率与实现高精度、高稳定性的信号检测

2011-11-03 15:13:16 75

75 本文主要对卷积码编码和Viterbi译码进行MATLAB实现,并在此基础上分析移位寄存器对纠错能力的影响。论文首先根据MATLAB的存储特点及函数特征,主要介绍卷积编码的原理,同时给出MA

2012-01-13 16:56:57 37

37 800Mbps准循环LDPC码编码器的FPGA实现

2016-05-09 10:59:26 37

37 本文介绍了基于DSP和FPGA的编码器信号测量及处理的通用模块,对海德汉编码器进行了概述等。

2017-10-13 18:17:29 19

19 Verilog HDL硬件描述语言完成其FPGA实现与验证,测试结果表明多速率卷积编码器可以实时地调整码率,高效稳定地进行差错控制,满足L-DACS1 高速传输仍保持稳定的要求,并且用于实际项目中。

2017-11-18 12:26:34 1263

1263

卷积码又称连环码,他是非分组(没有固定长度)有记忆编码,但也是一种线性码,码的结构简单,其性能在许多实际情况优于分组码,通常更适用于向前纠错,是一种较为常见的纠错编码。

2018-08-20 14:53:54 8789

8789 卷积码是一种差错控制编码,由P.Elias于1955年发明。因为数据与二进制多项式滑动相关故称卷积码。

2018-08-20 15:11:13 18667

18667

卷积码拥有良好的纠错性能,是一种被广泛应用于移动通信的信道编码系统。

2018-08-20 15:30:55 13387

13387

卷积码,将k个信息比特编成n个比特,但k和n通常很小,特别适合以串行形式进行传输,时延小。

2018-08-20 16:42:20 27532

27532 在信道编码研究的初期,人们探索、研究出各种各样的编码构造方法,其中包括卷积码。

2018-08-20 16:58:32 5029

5029

在信道编码研究的初期,人们探索、研究出各种各样的编码构造方法,其中包括卷积码。

2018-08-20 17:26:26 4600

4600

在信道编码研究的初期,人们探索、研究出各种各样的编码构造方法,其中包括卷积码。

2018-08-21 08:31:23 3102

3102 卷积码是一种差错控制编码,由P.Elias于1955年发明。因为数据与二进制多项式滑动相关故称卷积码。

2018-08-21 09:20:42 2220

2220

以(n,k,m)来描述卷积码,其中k为每次输入到卷积编码器的bit数,n为每个k元组码字对应的卷积码输出n元组码字,m为编码存储度,也就是卷积编码器的k元组的级数,称m+1= K为编码约束度m称为约束长度。

2018-08-21 09:56:13 2827

2827 卷积编码是现代数字通信系统中常见的一种前向纠错码,区别于常规的线性分组码,卷积编码的码字输出不仅与当前时刻的信息符号输入有关,还与之前输入的信息符号有关。

2018-08-21 10:26:04 7945

7945

卷积码是一种差错控制编码,由P.Elias于1955年发明。因为数据与二进制多项式滑动相关故称卷积码。

2018-08-21 10:34:42 3730

3730

在卷积码的编码过程中,对输入信息比特进行分组编码,每个码组的编码输出比特不仅与该分组的信息比特有关,还与前面时刻的其他分组的信息比特有关。

2018-08-21 10:51:24 13746

13746

卷积码是1955年由Elias等人提出的,是一种非常有前途的编码方法。

2018-08-21 11:07:25 29023

29023

位置编码器是工业自动控制中重要的反馈环节执行元件。位置编码器按工作方式分为绝对式和增量式两种。绝对位置式编码器的数据输出一般采用串行通信的方式。位置编码器的通信速度,在一定程度上影响闭环系统的时间常数。

2019-04-26 08:40:00 3593

3593

自1955年Elias发明卷积码以来,卷积码作为一种高效的信道编码已被用在许多现代通信系统中。卷积码分为零比特卷积码(Zero Tail CC,简称ZTCC)和咬尾卷积码(Tail Biting

2019-05-03 09:00:00 3784

3784

卷积码的编码器是由一个有k位输入、n位输出,且具有m位移位寄存器构成的有限状态的有记忆系统,通常称它为时序网络。编码器的整体约束长度为v,是所有k个移位寄存器的长度之和。具有这样的编码器的卷积码称作

2018-11-14 08:10:00 10950

10950

详细探讨了卷积Turbo码编码器实现过程中的关键问题,结合CCSDS及IMT-2000国际通信标准给出了具体解决方案。使用Maxplus2开发工具在CPLD.上实现了整个卷积Turbo码编码器并给出了系统分析,实验结果表明了该编码器的正确性和合理性。

2019-05-30 17:26:55 9

9 介绍并用VHDL语言实现了卷积编码和维特比译码。根据编码器特征设计了一种具有针对性的简洁的维特比译码器结构,

2021-05-12 15:22:41 2112

2112

卷积码是一种信道纠错编码,在通信中具有广泛的应用。在发送端根据生成多项式进行卷积码编码,在接收端根据维特比(Viterbi)译码算法进行译码,能够有效抵抗信道噪声的影响,在误码率门限之下可以对传输过程中发生的突发错误进行纠错。

2022-04-28 15:02:12 8799

8799

电子发烧友App

电子发烧友App

评论