利用FPGA实现双口RAM的设计及应用

概述:为了在高速采集时不丢失数据,在数据采集系统和

2010-04-16 14:08:36 11323

11323

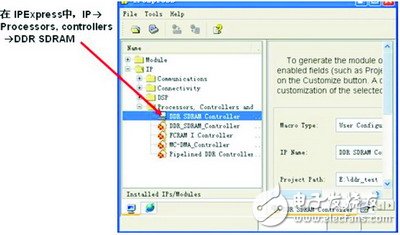

1. 背景 这篇文章主要介绍了DDR3IP核的写实现。 2. 写命令和数据总线介绍 DDR3 SDRAM控制器IP核主要预留了两组总线,一组可以直接绑定到DDR3 SDRAM芯片端口,一组是留给

2020-12-31 11:17:02 5068

5068

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA进出。DDR3存储器系统在大多数情况下可以为这些基于FPGA的系统

2019-05-24 05:00:34

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是与FPGA独立的,只是集成在了一起呢,还是占用了FPGA的资源来形成一个RAM?如果我以ROM的形式调用该IP核,在

2013-01-10 17:19:11

更快、更大,每比特的功耗也更低,但是如何实现FPGA和DDR3 SDRAM DIMM条的接口设计呢? 关键字:均衡(leveling)如果FPGA I/O结构中没有包含均衡功能,那么它与DDR

2019-04-22 07:00:08

各位大神,我最近在做FPGA项目遇到一个问题,我想实现这样的功能:向RAM里写一次数据,再多次读出来,可是我发现IP核里的RAM读第二次的时候RAM数据就清零了,根本读不我写的数据,请问有什么好的解决办法吗?谢谢啦!

2015-06-07 20:31:57

和DDR2/DDR3控制器(含DIMM);能够理解和使用FPGA中关于DDR器件的专用电路;能够使用和分析FPGA厂家提供的相关IP,以及8层PCB板层设计到BGN封装;能够了解高速数据传输的必要知识

2015-09-29 16:33:54

SDRAM和DDR2/DDR3控制器(含DIMM);能够理解和使用FPGA中关于DDR器件的专用电路;能够使用和分析FPGA厂家提供的相关IP,以及8层PCB板层设计到BGN封装;能够了解高速数据传输的必要

2015-09-30 10:36:41

=1.5V;但我看了一篇FPGA的DDR3 IP核例化文章,上面写FPGA的BANK1,3连接外部存储控制器(如下图,且只有四个BANK),所以要将DDR3连接在BANK3上。所以DDR3如何与FPGA芯片

2021-11-29 16:10:48

的相关内容,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用。话不多说,上货。IP

2023-03-14 17:38:29

实现特权同学的例程 特权FPGA VIP视频图像开发套件例程详解2——DDR2控制器读写测试 时,进行IP核配置时,进入下一步配置参数时,变成黑屏重装软件也不行

2018-01-24 08:23:17

实现特权同学的例程 特权FPGA VIP视频图像开发套件例程详解2——DDR2控制器读写测试 时,进行IP核配置时,进入下一步配置参数时,变成黑屏重装了软件也不行,到这个页面还是黑屏,软件版本是13.0

2019-05-17 06:35:42

就已经出现,随着FPGA芯片价格的不断降低,其在工业领域的应用正在飞速发展,采用FPGA来实现SVPWM调制算法也将层出不穷2. 系统任务分析及实现SVPWM调制算法相对比较复杂,在完成系统控制任务

2022-01-20 09:34:26

集中于非PCI部分,通过将FPGA厂商提供的IP模块与原理图、状态机及HDL语言等设计方法有机的结合,采用层次化结构,在功能强大的EDA软件环境下,于较短的时间内完成复杂电子系统的设计。来源

2019-05-08 07:00:46

×16bit)的DDR2 SDRAM为存储器。用一个IP核完成对4片DDR2的控制(带宽为64bit),且DDR2的最高速率可达200MHz,以此完成对数据的高速大容量存储。由于采用一个DDR2的IP核进行控制

2019-05-31 05:00:05

章礼宏 范全润1 引言随着电路规模不断扩大,以及竞争带来的上市时间的压力,越来越多的电路设计者开始利用设计良好的、经反复验证的电路功能模块来加快设计进程。这些电路功能模块被称为IP

2019-07-29 08:33:45

该IP核验证平台采用ALTERA Cyclone系列FPGA,型号为EP1C12Q240C8,提供超过30万门系统资源和240k bit的内部高速FIFO, 以及内部两个高速PLL,可以合成

2019-06-20 05:00:02

该IP核验证平台采用ALTERA Cyclone系列FPGA,型号为EP1C12Q240C8,提供超过30万门系统资源和240kbit的内部高速FIFO, 以及内部两个高速PLL,可以合成10M到

2019-06-12 05:00:07

和标准化。 在第一个专用 HVL(硬件验证语言)出现后不久,验证方法就应运而生。采用方法论(如 UVM)的主要优点是• 通过测试台重用和验证 IP 实现即插即用的可重用性• 一种行之有效的方法,具有行业

2022-02-13 17:03:49

...............................................11.2 FPGA 验证技术...............................................31.3 Altera

2015-09-18 15:26:25

拥有成本,从而带来可持续的长期盈利能力。美高森美公司(Microsemi)提供具有硬核ARM Cortex-M3微控制器和IP集成的SmartFusion2 SoC FPGA器件,它采用成本优化的封装

2019-06-24 07:29:33

先进的设计与仿真验证方法成为SoC设计成功的关键。一个简单可行的SoC验证平台,可以加快SoC系统的开发与验证过程。FPGA器件的主要开发供应商都针对自己的产品推出了SoC系统的开发验证平台,如

2019-10-11 07:07:07

你好任何人都可以指导我,Xilinx ISE中的DDR控制器是否有任何IP实现。如果没有如何实现DDR控制器以上来自于谷歌翻译以下为原文Hi can any one guide me

2019-02-27 12:13:51

请教各位大神,小弟刚学FPGA,现在在用spartan-3E的板子,想用上面的DDR SDRAM进行简单的读写,用MIG生成DDR核之后出现了很多引脚,看了一些资料也不是很清楚,不知道怎么使用生成的这个IP核控制器来进行读写,希望大神们稍作指点

2013-06-20 20:43:56

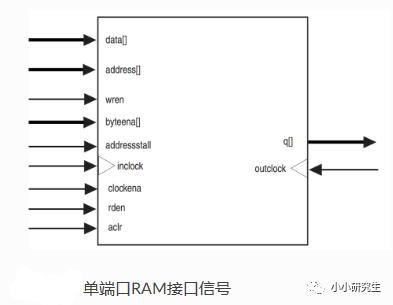

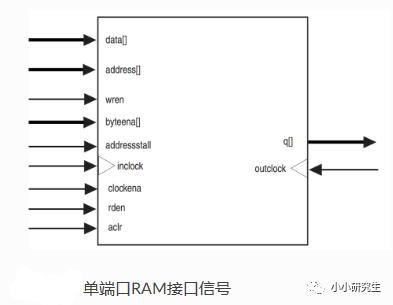

Altera Cyclone 系列FPGA器件的内部结构,然后介绍了RAM IP核的调用方法和配置窗口中的一些参数含义,然后通过仿真的方式对RAM IP核的接口时序进行了分析,为下一节课,RAM IP

2015-10-23 12:47:16

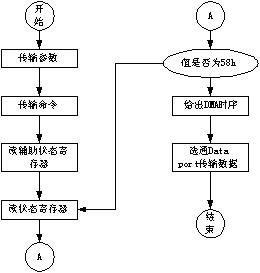

给FPGA,FPGA接收后存储在RAM中,再在按键的控制下,读取RAM中的数据,通过串口发送出去。来体现模块化设计的巨大优势。同时,视频花了相当的时间来演示使用Visio绘制系统架构图,一个好的架构图

2015-10-23 13:01:50

摘要针对FFT算法基于FPGA实现可配置的IP核。采用基于流水线结构和快速并行算法实现了蝶形运算和4k点FFT的输入点数、数据位宽、分解基自由配置。使用Verilog语言编写,利用ModelSim

2019-07-03 07:56:53

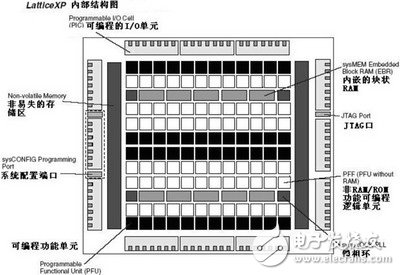

设计来增设全新的芯片功能,据此实现了芯片整体构造的简化与性能提升。下面英尚微电子介绍FPGA开发板内部ram是如何操作的。 除逻辑外,所有新的FPGA都有专用的静态ram块,这些块在逻辑元素之间分布并由

2020-09-10 11:11:57

你好,先生或女士我是中国学生。我已经研究FPGA一段时间了,我正在尝试使用FPGA来实现FC协议。经过一番研究,我发现GTH可以达到FC1。但是我发现使用7系列FPGA收发器向导IP存在一些问题。我

2020-08-17 10:28:07

采用FPGA来实现,TM的常规结构如图1所示。图1TM的常规结构图 目前主流的TM接口均为SPI4-P2接口形式,SPI4-P2接口信号速率高,TCCS(Channel-to-channel skew

2012-11-09 18:43:41

`例说FPGA连载36:DDR控制器集成与读写测试之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 本实例对Altera提供

2016-10-08 17:05:55

`例说FPGA连载38:DDR控制器集成与读写测试之FPGA片内RAM概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 我们所

2016-10-12 17:18:25

`例说FPGA连载39:DDR控制器集成与读写测试之FPGA片内RAM设置与集成特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc

2016-10-14 18:07:34

`例说FPGA连载41:DDR控制器集成与读写测试之DDR2 IP核接口描述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 如图

2016-10-27 16:36:58

。● ddr2_controller.v二级子模块也是一个软核IP,实现DDR2的时序控制功能,并且通过一个简单的Avalon接口实现DDR2和FPGA逻辑之间的读写数据传输。其实该模块下还有多个子模块,但由于只是一个IP核,内部代码不

2016-11-08 18:18:29

利用FPGA自带的IP核实现双口RAM用于2片MCU进行数据交换时多次读数据后RAM中数据变为了0,是什么意思,打什么帮帮忙!!!!!!!!!!!!!!

2018-01-15 16:22:16

。 本手册以一个经过验证的可稳定工作的设计为例,来系统介绍高云FPGA连接DDR3的硬件设计方法,FPGA芯片型号采用GW2A-LV18PG256,存储芯片采用镁光(Micron)公司生产的单晶粒封装

2022-09-29 06:15:25

进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行类FIFO接口的封装,屏蔽掉了DDR3 IP核复杂的用户接口,为DDR3数据流缓存的实现提供便利。系统测试表明,该

2018-08-02 09:34:58

Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取的应用背景,设计和实现了

2018-08-30 09:59:01

的应用。采用FPGA技术构造双口RAM,实现高速信号采集系统中的海量数据存储和时钟匹配。功能仿真验证该设计的正确性,该设计能减小电路设计的复杂性,增强设计的灵活性和资源的可配置性能,降低设计成本,缩短

2010-04-24 09:44:28

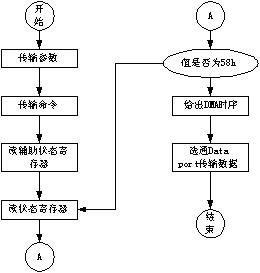

此提供了新的解决方案。IP核(IP Core)是具有特定电路功能的硬件描述语言程序,可较方便地进行修改和定制,以提高设计效率[3]。本文研究了基于FPGA的数据采集控制器IP 核的设计方案和实现方法,该IP核既可以应用在独立IC芯片上,还可作为合成系统的子模块直接调用,实现IP核的复用。

2019-07-09 07:23:09

但是,如果FPGA通过接口与DSP核心连接,并且高速视频数据是通过它来传输,那么它根本不是简单的系统。这种更高的设计复杂度导致了额外的验证难题,并且如果您在设计阶段晚期发现一处重大错误,那么这还会导致高成本的系统板重制。为了消除这一隐患,您必须仔细考虑自己采用的验证方法,以便降低重制风险。

2019-09-19 06:00:59

核的分类和特点是什么?基于IP核的FPGA设计方法是什么?

2021-05-08 07:07:01

工具,经面向硬件电路的仿真验证,本文的方法可实现OC-48接口(2.5Gb/s)上线速分组的IP碎片重组,并具有硬件开销小,可扩展性好的特点。关键词: IP碎片;FPGA;RLDRAM控制器;最大传输

2008-10-07 11:00:19

Xilinx公司发布的SP6,V6系列的FPGA中的DDR2的IP核是一大改变。它由原来的软核变为了硬核,此举让开发DDR2变的简单,因为不需要太多的时序调试,当然也带来了麻烦,这是因为当DDR

2015-03-16 20:21:26

Flow将其转成ASIC版图.实现流片。2.3 IP核的验证方法在芯片的设计流程中设计的验证是一个重要而又费时的环节。在进行Top_Down设计时.从行为级设计开始到RTT级设计再到门级设计相应地利

2021-09-01 19:32:45

1 简介随着设计的复杂程度不断增加,要求把更多的资源放到验证上,不但要求验证能够覆盖所有的功能,还希望能够给出大量的异常情况来检查DUT对应异常的处理状态,这在传统测试方法下往往是难以实现的。此外

2019-07-03 07:40:26

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一个单独的奇偶校验写使能位,但在FPGA RAM中没有单独的Pariaty写使能位。 如何实现ASIC RAM奇偶校验写入启用ino FPGA RAM。谢谢娜文G K.

2020-04-24 09:37:05

随着电路规模不断扩大,以及竞争带来的上市时间的压力,越来越多的电路设计者开始利用设计良好的、经反复验证的电路功能模块来加快设计进程。这些电路功能模块被称为IP

2019-09-03 07:44:22

如何采用现场可编辑门阵列FPGA来实现对直流电机的控制?

2021-10-19 09:08:30

请教各位大佬,UVM是基于sv的验证方法学,如果采用systemc语言编程,如何实现?

2019-11-07 15:30:16

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

Xilinx DDR 控制器。 DDR PHY 与电路板调试: Zynq UltraScale+ MPSoC VCU DDR 控制器采用 MIG PHY。 这意味着您可以使用标准 MIG 示例设计来验证您

2021-01-07 16:02:09

本帖最后由 小梅哥 于 2015-6-15 22:18 编辑

各位喜爱FPGA技术的小伙伴。小梅哥FPGA设计思想与验证方法视频教程的课程大纲已经出炉,欢迎大家根据自己的实际感受,提出各种批评

2015-06-15 22:01:45

大家好,我想设计自己的DDR控制器并在FPGA上验证它。我将在verilog中实现我刚开始阅读JESDC79C DDR规格..但我很困惑如何编写那些初始化序列?请建议如何处理这个设计DDR控制

2019-04-29 11:59:22

DDR2控制和FPGA实现

2015-07-21 19:28:14

步进电机控制通常采用什么方法实现?

2021-09-30 07:15:35

错误检查硬件,监视软错误导致的变化。由于这些硬核IP 是在FPGA 逻辑区中实现的,因此,系统处理器不再承担这些任务。设计按照Altera 的建议来实现。在认证方法方面,Altera 采用了IEC 规范

2013-11-20 16:57:29

本文介绍一种采用Lattice FPGA与IP来实现DDR RAM控制和验证的方法。

2021-05-06 09:52:30

IJF编码是什么原理?如何实现IJF编码?采用FPGA和集成器件来实现IJF编码

2021-04-13 06:56:04

本文介绍一款USB 设备控制器IP CORE 的设计与实现。论文首先介绍了USB 设备控制器的设计原理,模块划分及每个模块的功能。然后介绍了该IP CORE 在ModelsimSE 中的功能仿真及FPGA 验证结

2009-08-06 11:39:00 8

8 针对当今电子系统对高速大容量内存的需要,本文阐述了使用DDR 控制器IP 核来设计实现DDR内存接口的方法。该方法能使设计尽可能简单,让设计者更专注于关键逻辑设计,以便达到

2009-08-11 09:42:51 20

20 NandFlash控制器的FPGA实现方法技巧与程序案例分享。

2017-09-21 09:40:00 78

78 为了在高速采集时不丢失数据,在数据采集系统和CPU之间设置一个数据暂存区。介绍双口RAM的存储原理及其在数字系统中的应用。采用FPGA技术构造双口RAM,实现高速信号采集系

2010-02-11 11:20:27 69

69 本文主要阐述了在某雷达系统中为实现伪码对齐,所采用的滑动控制方法的原理及在FPGA芯片上的实现。

2010-03-02 16:04:22 13

13 DDR验证和调试的高级方法:Memory Design and ValidationChip/Component DesignPrecise understanding of circuit

2010-06-29 17:16:13 21

21 采用FPGA和DSP直接控制硬盘实现存储控制的方法

摘 要 介绍了采用FPGA和DSP直接控制硬盘进行数据存储的方法,并采用一片FIFO作为数据缓存,能够满足80Khz数

2010-01-12 11:27:22 981

981

利用FPGA实现时分多址的方法有很多种,但大多数方法都对FPGA芯片资源的占用非常巨大。针对这一问题,提出一种改进型方法来实现时分多址。通过使用FPGA芯片内部的双口随机访问存储器(双口RAM),利用同一块RAM采用两套时钟线,地址线和数据线,例化双口RAM的

2011-01-15 15:41:26 29

29 本文侧重于介绍IP 模块中组件控制器的设计和实现。一个基于FPGA 的LCD 控制器设计作为例子被介绍。这个组件控制器设计属于固核IP 设计,也就是软硬结合的方法。设计内容主要包括电

2011-12-22 14:00:11 1143

1143

基于FPGA的SD卡控制器IP,以验证可用。

2015-11-06 09:50:50 10

10 DDR2SDRAM控制器IP功能测试与FPGA验证_陈平

2017-01-07 21:45:57 3

3 技术方法,验证了SoC系统、DSP指令、硬件IP等。实验证明,此FPGA验证平台能够验证SoC设计,提高了设计效率。

2017-11-17 03:06:01 13138

13138

为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通过用户接口信号就能完成DDR

2017-11-18 18:51:25 6412

6412

提出一种便于用户操作并能快速运用到产品的DDR2控制器IP核的FPGA实现,使用户不需要了解DDR2的原理和操作方式的情况下,依然可以通过IP核控制DDR2。简单介绍了DDR2的特点和操作

2017-11-22 07:20:50 4687

4687

,理解内存控制器对存储设备的控制机制;然后,设计了接口协议解析逻辑的总体架构,采用FPGA实现并对其中的各个关键技术点,包括时钟、写平衡、延迟控制、接口同步控制等进行详细阐述;最后,通过modelsim仿真并进行板级验证,证明了该设计的正确性和可行

2017-12-05 09:34:44 10

10 本文实现的基于FPGA的PCIe总线接口的DMA控制器是在Altera PHY IP和Synopsys Core IP的基础上实现的,利用Synopsys VIP验证环境进行了功能仿真验证

2018-01-11 10:57:04 11281

11281

大家好,又到了每日学习的时间了,今天我们来聊一聊在FPGA设计中RAM的两种使用方法,RAM是用来在程序运行中存放随机变量的数据空间,使用时可以利用QuartusII的LPM功能实现RAM的定制

2018-06-08 11:30:28 19562

19562 实现数据的高速大容量存储是数据采集系统中的一项关键技术。本设计采用Altera 公司Cyclone系列的FPGA 完成了对DDR SDRAM 的控制,以状态机来描述对DDR SDRAM 的各种时序

2019-08-14 08:00:00 3401

3401

复旦大学微电子学院某国家重点实验室内部教学视频:基于ZYNQ FPGA与PC的IP设计与验证方案。

关键词:IP设计,IP验证,AXI总线协议,ARM,UDP传输,PYTHON

2019-08-06 06:16:00 1968

1968

学完SDRAM控制器后,可以感受到SDRAM的控制器的书写是十分麻烦的,因此在xilinx一些FPGA芯片内已经集成了相应的IP核来控制这些SDRAM,所以熟悉此类IP核的调取和使用是非常必要的。下面我们以A7的DDR3 IP核作为例子进行IP核调取。

2019-11-10 10:28:45 4702

4702

DesignWare DDR5/4 PHY IP核提供基于固件的训练,无需更改硬件即可进行现场升级,从而帮助客户降低采用新协议的风险。基于固件的训练也有助于使用复杂的训练模式,在系统层面上支持最高裕度和通道可靠性。

2020-08-28 15:38:04 1986

1986 DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 开发工具:Vivado

2020-11-26 15:02:11 7386

7386

核的使用。 BRAM是FPGA定制的RAM资源,有着较大的存储空间,且在日常的工程中使用较为频繁。BRAM以阵列的方式排布于FPGA的内部,是FPGA实现各种存储功能的主要部分,是真正的双读/写端口的同步的RAM

2020-12-29 15:59:39 9496

9496 基于FPGA的DDR3SDRAM控制器设计及实现简介(arm嵌入式开发平台PB)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现简介资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器设计及实现(嵌入式开发式入门)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 13:07:09 35

35 本实验基于xilinx ARTIX-7芯片验证实现,有时间有兴趣的朋友可在其他FPGA芯片上实现验证。

2023-04-11 10:51:14 703

703 我们知道除了只读存储器外还有随机存取存储器,这一篇将介绍另一种 存储类IP核 ——RAM的使用方法。RAM是 随机存取存储器 (Random Access Memory),是一个易失性存储器,断电丢失。RAM工作时可以随时从任何一个指定的地址写入或读出数据。

2023-08-29 16:46:07 1660

1660

本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 745

745

定制的RAM资源,有着较大的存储空间,且在日常的工程中使用较为频繁。BRAM以阵列的方式排布于FPGA的内部,是FPGA实现各种存储功能的主要部分,是真正的双读/写端口的同步的RAM。 本片

2023-12-05 15:05:02 317

317 FPGA双口RAM的使用主要涉及配置和使用双端口RAM模块。双端口RAM的特点是有两组独立的端口,可以对同一存储块进行读写操作,从而实现并行访问。

2024-03-15 13:58:14 81

81

正在加载...

电子发烧友App

电子发烧友App

评论