根据BPSK调制信号调制机理和平方倍频法原理,在FPGA平台上设计实现了BPSK调制信号载波频率估计单元。

2014-09-01 11:26:40 2585

2585 本文系统的实现主要用到了两类逻辑资源来优化系统性能:DSP48E Slice:25x18位二进制补码乘法器能产生48位全精度结果。此功能单元还能够实现诸多DSP模块如乘累加器、桶形移位器、宽总线多路复用器等。

2020-09-03 12:45:22 555

555

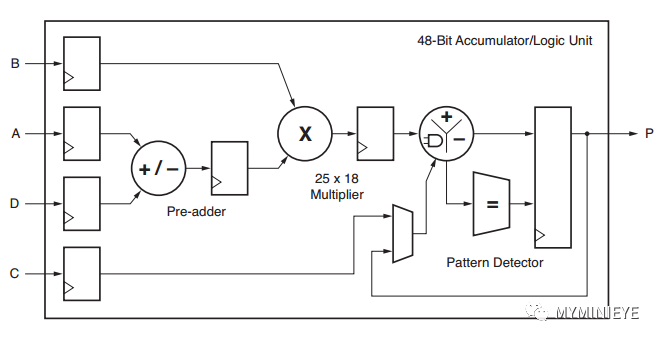

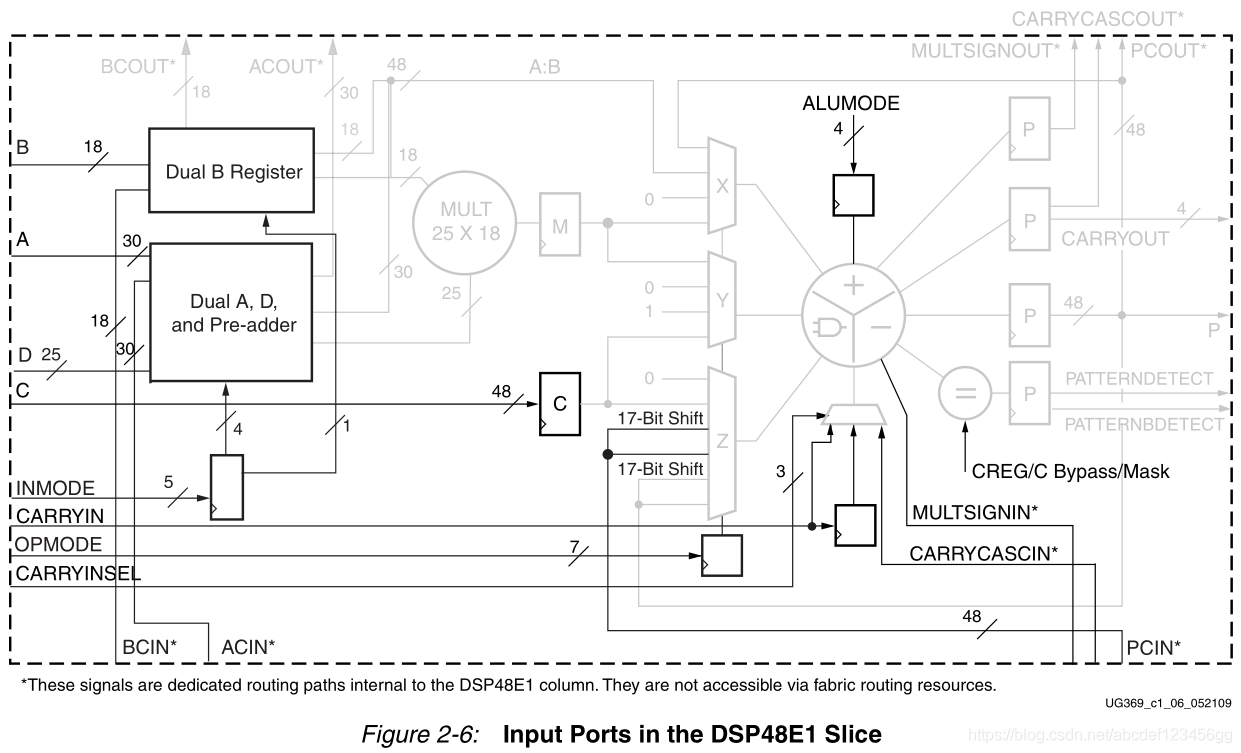

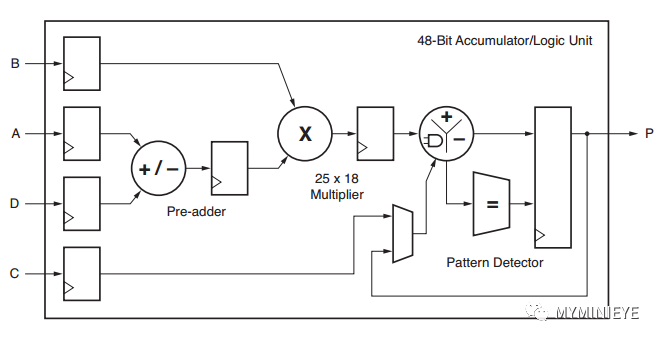

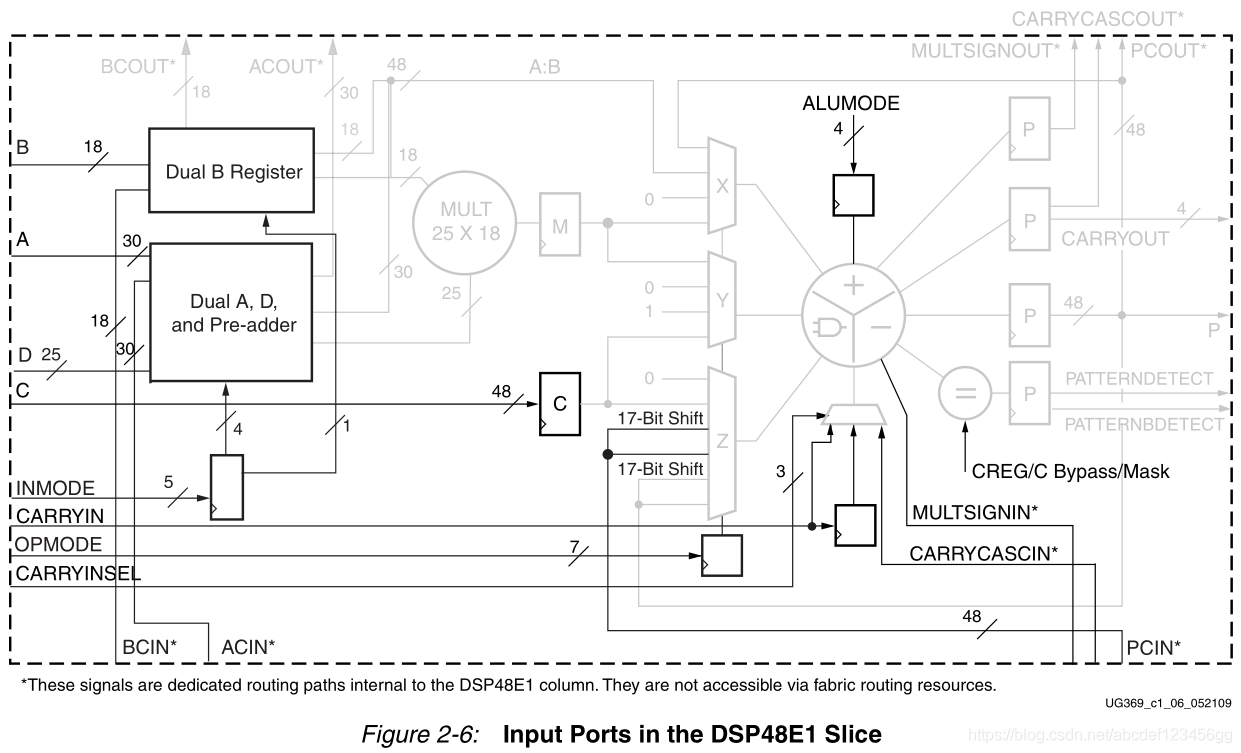

充分利用DSP资源,我们需要对DSP48E1有所了解。 1.DSP48E1介绍 DSP48E1是7系列的最小计算单元,DSP资源,支持许多独立的功能,其基本功能如下所示 DSP48E1简易模型 包括: 带有D寄存器的25位预加法器 25*18二进制乘法 48位累加 三输入加法 其他的一些功能还包括

2020-09-30 11:48:55 26617

26617

和C寄存器,具有独立的复位和时钟启用。 •CARRYCASCIN和CARRYCASCOUT内部级联信号支持两个DSP48E1片中的96位累加器/加法器/减法器 •MULTSIGNIN

2021-01-08 16:46:10

7系列FPGA DSP48E1片的特点什么

2021-03-05 06:26:41

我正在实例化DSP切片并进行简单的乘法然后加法((A * B)+ C)。根据DSP48E1用户指南,当使用所有三个流水线寄存器时,它给出了最高频率为600 MHz。但就我而言,它使用流水线寄存器

2020-06-12 06:32:01

嗨,我有一个如下的指令:(D-A)* B + C.端口A,B,C,D与DSP48E1输入引脚相对应。我试图将整个操作打包在DSP单元中。 (顺便说一句,我的数据宽度是8位)在布局和布线完成后,我

2019-04-01 14:25:40

在我的设计中,我需要延迟一些数据(32位宽)一段时间。我一直在使用SRL16而不是FFs,它可以很好地延迟超过几个周期。我还注意到,使用DSP48E1片很容易将数据延迟到48位宽,延迟三个周期,因此

2019-04-18 06:40:33

DSP48E1属性

2021-01-27 06:21:23

。 DSP48E1片输入数据端口支持许多通用的DSP和数学算法。DSP48E1片有四个直接输入数据端口,分别为A、B、C和D。 A数据端口宽30位,B数据端口宽18位,C数据端口宽48位,预加器D数据端口宽25位

2020-12-23 16:54:08

)是指在系统加电时,DSP将一段存储在外部的非易失性存储器的代码移植到内部的高速存储器单元中去执行。这样既利用了外部的存储单元扩展DSP本身有限的ROM资源,又充分发挥了DSP内部资源的效能。尽管用户代码在

2011-07-08 11:10:56

DSP56800 16位DSP内核架构DSP56800内核是一款旨在同时提供高效实时DSP能力和通用计算能力的可编程CMOS 16位DSP内核。DSP56800内核由四个并行执行的功能单元组成,从而

2011-07-16 14:21:33

DSP56800 系列简介DSP56800系列芯片基于DSP56800 16位定点DSP微控制器中央处理单元(CPU)内核。DSP56800内核的设计宗旨是同时提供高效的DSP和控制器运算能力。其

2011-07-16 14:20:41

`产品特点基于ZYNQ+并行DSP处理架构处理架构十分灵活,能够满足各类并行加速需求支持OpenCL编程,方便算法移植系统处理灵活:FPGA或DSP可选尺寸小巧,方便集成扩展能力强 应用领域并行控制

2017-06-08 10:33:07

DSP并行处理的方法摘 要:TI公司的TMS320C6x和AD公司的ADSP2106x是目前业界使用广泛的数字信号处理器(DSP)。

2009-11-03 15:16:47

操作,用硬件的方法总比用软件的方法有着无法比拟的速度优势。 DSP处理都有自己的累加器单元AUL,大多数的DSP处理器在执行乘加操作时可以在一条指令周期内同时...

2021-11-03 08:41:44

想请教一下高手,公司了DSP开发或大家自己开发学习用TI定义的库还是自己定义相关寄存器,然后在自己定义的基础上进行相关算法的开发????

2014-05-22 12:58:35

充当,利用DSP的HPI接口组成一个多DSP互 连并行系统,一般是一个主处理器和一个从处理器,此种方法的一个应用实例是在雷达中的应用。滑窗算法是数字信号处理中一种常用的基本算法,但滑窗算法一般

2019-04-08 09:36:19

近来,Altera公司推出业界首款浮点FPGA,它集成了硬核IEEE754兼容浮点运算功能,提高了DSP性能、设计人员的效能和逻辑效率。据悉,硬核浮点DSP模块集成在

2019-07-03 07:56:05

1.請問AM335X armv7 架構是否有向DSP 有單週期可執行多個乘加運算的功能 ??

2. FFT 運算式會運用到AM335X的VFP 還是NEON??

3.若執行一段浮點運算程式碼 例如

2018-06-21 06:58:42

算术逻辑单元(ALU)和一个带有48位累加器的单24x24位乘加器(MAC)。这些单元都以并行状态工作,并具有双口数据存储接口,可以同时产生地址信息。所有寻址模式包括反转和求模运算都支持高效率的单周期访问。

2011-03-12 03:00:07

分时钟、DSP48E/A模块、BRAM模块、DCM模块。0.5学时4. ISE高级操作技巧,包括:FloorPlanner、FPGA Editor、ChipScope Pro

2009-07-21 09:22:42

小、带宽要求低等优点,特别适用于各种无线设备和智能卡等计算资源受限的设备,因而受到了人们的广泛关注,成为新一代公钥密码标准。而模乘运算是椭圆曲线加密算法中的核心运算,如何高效地实现模乘运算是当前的一个研究热点。

2020-03-20 06:04:40

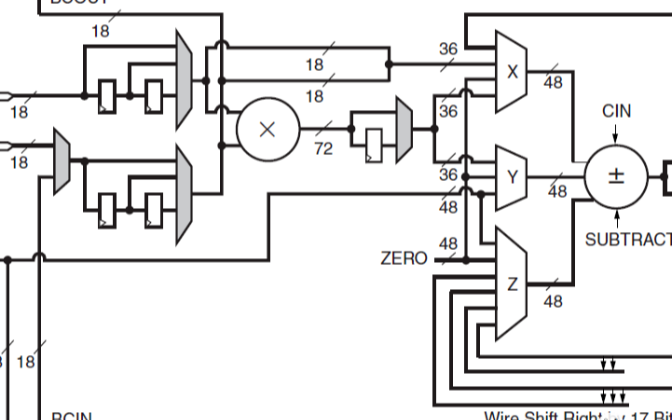

,Z选择器的输入;(7bit)

•ALUMODE逻辑控制选择单元;(4bit)

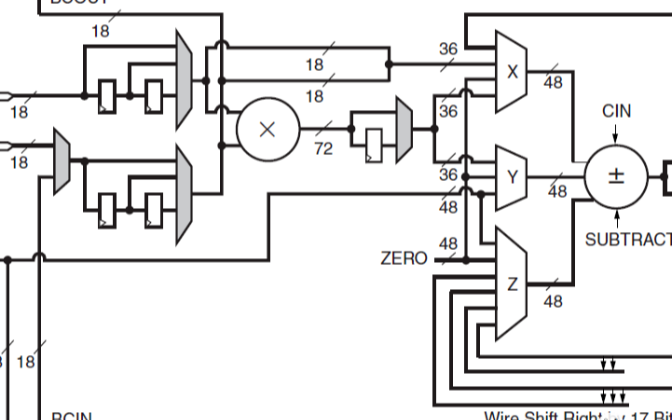

我们通过构建一个乘累加器来介绍DSP的使用以及寄存器的配置。

实现的乘累加完成如下功能,即SUM = SUM

2023-06-20 14:29:51

数字信号处理(DSP)芯片曾经作为协处理器来实现滤波器算法。现在DSP技术的发展已实现了多个复杂算法的并行。但是,这种功能的扩展也产生了新的问题,开发人员发现,在DSP处理能力方面,当MIP和存储器的问题得

2010-04-03 08:21:50

分时钟、DSP48E/A模块、BRAM模块、DCM模块。0.5学时4. ISE高级操作技巧,包括:FloorPlanner、FPGA Editor、ChipScope Pro

2009-07-21 09:20:11

分时钟、DSP48E/A模块、BRAM模块、DCM模块。0.5学时4. ISE高级操作技巧,包括:FloorPlanner、FPGA Editor、ChipScope Pro

2009-07-24 13:07:08

本帖最后由 eehome 于 2013-1-5 10:03 编辑

fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点

2012-08-11 18:27:41

fpga实现滤波器fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点。本文研究了一种16阶FIR滤波器的FPGA设计方法

2012-08-12 11:50:16

为什么BUFG驱动DSP48E1的CE会出现问题?警告:LIT:683 - DSP48E1符号“Inst_control_loop / u_Subsystem11

2020-06-12 11:45:43

QuartusII中乘加器IP的手册,如上图所示,出现DSP Blocks字样。手册中说到,DSP块由一些专用的逻辑块组成。这些逻辑块可以实现乘法、加法、减法、累加、求和运算。你可以把DSP块配置成

2020-09-04 10:31:13

与遵循冯·诺依曼结构的CPU和单片机不同,典型的DSP内部采用改进的哈佛结构和流水线技术,可以在单指令周期内完成乘加指令,更具有扩展动态范围的乘积累加单元、数据指针环形寻址和零开销循环跳转等特殊

2011-03-06 22:28:27

)、离散余弦变换(DCT)、小波变换、数字滤波器(有限脉冲响应(FIR)、无限脉冲响应(IIR)和自适应滤波器)以及数字上下变频器。这些算法中,每一种都有一些结构性的元件可以用并行方法实现。而FPGA

2021-12-15 06:30:00

的软件,变得更加重要。为满足需求,文中提出一种基于DSP/ BIOS的软件架构,可提高软件的可维护性和可重用性,方便算法的裁减添加及程序的跨平台移植,实现多类信号多路并行处理的软件快速开发设计。1 DSP

2012-09-03 17:18:51

传统数字滤波器硬件的实现主要采用专用集成电路(ASIC)和数字信号处理器(DSP)来实现。FPGA内部的功能块中采用了SRAM的查找表(lo-ok up table,LUT)结构,这种结构特别适用于并行处理结构,相对于传统方法来说,其并行度和扩展性都很好,它逐渐成为构造可编程高性能算法结构的新选择。

2019-10-22 07:14:04

DSP并行系统。因为该系列的处理器在构成并行处理系统时其本身就提供了实现互连所需的片内总线仲裁控制和特有的链路口,可以以各种拓扑结构互连DSP,满足大运算量和片间通信灵活的要求。此外,选用ADSP

2019-05-21 05:00:19

的距离块就可以完成256个单元的计算。把上述结构映射到FPGA上实现,则FPGA上并行32个运算单元,且每1个运算单元具有1个与其他运算单元独立的复数乘加模块、寄存器组和1个互相关值输出锁存寄存器

2009-09-19 09:25:42

DSU相关的权函数使用,记为fI和fQ;接收回波信号在A/D采样后,经过正交分解形成数据流rI和rQ,然后对接收数据进行相关操作,即回波数据以流水方式通过相关器与发射样本数据逐点进行乘加处理。本论

2015-02-05 15:34:43

针对长期演进(LTE)下行正交频分复用(OFDM)系统的最小二乘(LS)信道估计算法对噪声比较敏感的问题,提出了一种基于小波变换去噪与变换域插值相结合的信道估计方法。该方法通过在最小二乘(LS)估计

2010-05-06 09:01:31

/20755211100719/1310381718_530721f7.gif]4 FFT复乘的FPGA实现由于软件和DSP实现的速度较慢,而FPGA资源丰富,组织结构便于采用流水线结构和并行运算,其速度快、扩展能力强

2011-07-11 21:32:29

本帖最后由 mr.pengyongche 于 2013-4-30 03:23 编辑

8核的TMS320C6678款DSP芯片一个周期可

2012-02-18 13:19:36

本帖最后由 mr.pengyongche 于 2013-4-30 03:23 编辑

8核的TMS320C6678款DSP芯片一个周期可

2012-02-18 13:29:59

,图2-1和第14页和第16页的2-2中的原理图,我注意到乘法路径具有实现3级流水线所需的寄存器但是,C输入的datha路径只能使用2个寄存器。所以我的问题是,我应该在DSP48E1 Block之外添加

2020-07-21 13:52:24

FIFO芯片是什么?如何利用FIFO去实现DSP间双向并行异步通讯?

2021-06-02 06:08:17

DSP48E1片的数学部分由一个25位的预加器、2个25位、18位的补法器和3个48位的数据路径多路复用器(具有输出X、Y和Z)组成,然后是一个3输入加法器/减法器或2输入逻辑单元(参见图2-5

2021-01-08 16:36:32

简化DSP48E1片操作

2021-01-27 07:13:57

喜据我所知,有些xilinx FPGA具有DSP Slice(DSP48E)。在fpga设计摘要中,我看到切片寄存器,切片LUT,占用切片等以及DSP48E的单独行。我的问题是 - 1)DSP48E

2019-04-04 06:36:56

值。目前,数字信号处理器(DSP)技术的高速发展为高效媒体处理器的实现提供了可靠的硬件平台。C64系列DSP是当前TI(Texas Instruments)公司推出的处理能力最高的定点DSP,NVDK

2008-06-25 10:35:31

我一直在尝试将DSP48E1原语用于具有自动终端计数重置的计数器。大部分工作都很好,但我看到的一个问题是我无法让DSP48E1进行模式检测0.如果我将C输入设置为48'd0,则在P =开始时

2020-07-28 10:38:40

。 Achronix为了解决这一大困境,创新地设计了机器学习处理器(MLP)单元,不仅支持浮点的乘加运算,还可以支持对多种定浮点数格式进行拆分。

2020-11-26 06:42:00

嘿,为了在Zynq设备上对一种算法的不同实现进行简单比较,我想为每种实现的资源使用创建一个指示符,例如CLB的使用。因此,获得基本元素CLB,DSP48E1和BRAM36K的面积指标会很好。在

2020-07-25 11:04:42

基于STM32F407-DISCO的低通滤波器的设计

单电源低通加隔值电容

STM32F407自带DSP硬核和FPU处理单元,对外部输入的低频信号

2017-04-16 21:54:33

、译码和执行等操作可以重叠执行。 当然,与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。 DSP优势在于其有独特乘法器,一个指令就可以完成乘加运算,但GPP(通用处理器)处理一般是用加法代替乘法

2018-12-11 12:05:54

、译码和执行等操作可以重叠执行。 当然,与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。 DSP优势在于其有独特乘法器,一个指令就可以完成乘加运算,但GPP(通用处理器)处理一般是用加法代替乘法

2019-02-25 16:58:00

操作,使取指、译码和执行等操作可以重叠执行。 当然,与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。 DSP优势在于其有独特乘法器,一个指令就可以完成乘加运算,但GPP(通用处理器)处理一般是用

2019-05-16 17:06:34

我看书上说现代DSP内置MAC硬核,可以在一个时钟周期完成取数相乘并累加。实验如下,例如c=a*b+c;反汇编如下可以看到有七句汇编,先用2个周期取ab值,1个周期相乘,1个周期取c值,1个周期想加

2018-10-10 11:08:14

【摘要】针对以往DOA估计算法中智能天线系统的阵列单元模型多采用全向振子的情况,分析了当天线单元存在方向性时对MUSIC算法估计信号到达角的影响,并在进行阵元互耦校正后

2009-03-14 15:12:51 18

18 基于VxWorks的多DSP并行处理系统的实现

2009-03-29 12:31:18 17

17 High DSP Performance Platform– The DSP48E Slice– Essential DSP Building Blocks• Imaging Algorithms

2009-04-09 22:05:31 12

12 本文针对CDMA 系统,提出使用DSP 器件TMS320C6701 实现对CDMA 信号的波达方向估计。该算法基于对解扩前后相关阵相减,去除了干扰相关阵是,然后使用传统MUSIC或ESPRIT 算法进行DOA 估

2009-06-18 09:13:09 16

16 本文针对CDMA 系统,提出使用DSP 器件ADSP21160 实现对感兴趣用户的波达方向和多径时延进行联合估计的算法。该算法是对传统MUSIC 方法的推广与变形,克服了要求接收信号数小于阵

2009-08-26 08:55:22 11

11 信道估计是RAKE 接收机的关键技术,WCDMA 中可采用时分复用导频完成,给出了用DSP 的具体实现方案。关键词:DSP;信道估计;WCDMA

2009-09-15 09:36:23 28

28 PC机与DSP之间的并行通讯技术

摘要:对PC 机在EPP 模式下与C6000 系列DSP 的HPI 口之间进行的并行通讯进行了研究,提出了用EPP 协议和CPLD 实现DSP 与计算机并口

2010-04-07 14:37:06 35

35 基于TMS320C6416高性能通用DSP,实现了对AWGN信道的信噪比(SNR)估计,并以此估计值设计了一种低密度奇偶校验(LDPC)码的译码系统;详尽介绍了集成SNR估计的译码系统的实现方案和流程;仿真

2010-07-27 16:28:32 11

11 摘要:提出了一种巧妙实现DSP并行自举的方法,即采用“两次下载法”,利用DSP自身对FLASH编程,以实现DSP的并行自举。这种在系统编程的DSP自举实现方式无需文件

2006-03-11 17:39:50 1400

1400

带有饱和处理功能的并行乘加单元设计

本文介绍了一种48bit+24bit×24bit带饱和处理的MAC单元设计。在乘法器的设计中,采用改进的booth 算法来减少部分积的数目,用由压缩单

2009-03-28 16:28:58 1598

1598

在水下日标检测和跟踪系统中,多目标方位估计算法起着重要的作用.MUSIC算法是最具代表性的方法}为了满足目标方位估计对高速变时并行处理技术的要求,针对水下阵列信号处理的实

2011-10-12 16:19:54 41

41 介绍了时差测向的基本原理,其关键在于对时差的测量,因此主要工作即为对跳频信号进行时差测量。基于信道化方法对跳频信号进行时差估计具有较高的精度,可以在FPGA中实现。

2012-02-08 15:12:58 34

34 基于ADSP_TS201S的多DSP并行系统设计

2015-12-29 17:33:04 22

22 题(1):使用DS48E1的SIMD功能实现四路并行12位加法”,要求数据从不同的DSP48端口进去。 评分标准: 1)使用Vivado 仿真通过 2)使用7A50T板子,使用Vivado硬件实现且记录波形,或者,使用Matlab sysgen硬件仿真,或者其他硬件实现方式且有硬件结果 软件环境:

2017-02-07 20:23:33 2159

2159 TMS320VC5416DSP并行自举方案的设计与实现

2017-10-20 09:15:22 12

12 DSP通过FLASH并行加载的分析和实例

2017-10-20 10:15:16 7

7 DSP并行系统的并行粒子群优化目标跟踪

2017-10-20 10:54:00 6

6 介绍了利用CYPRESS公司的FIFO芯片CY7C419实现DSP间双向并行异步通讯的方法,该方法简单实用,速度快,特别适用于小数据量的数据相互传送。文中给出了CY7C419的引脚功能以及用FIFO

2017-10-25 11:35:25 0

0 根据BPSK调制信号调制机理和平方倍频法原理,在FPGA平台上设计实现了BPSK调制信号载波频率估计单元。利用ModelSim仿真环境对载频估计功能进行仿真,验证了平方倍频法对BPSK信号进行载波

2017-11-18 05:13:05 3576

3576

针对均匀线性阵列DOA估计中的实时性和解相干问题,提出了一种基于单次快拍数据的估计算法,通过对阵列接收的单次快拍数据进行相关处理后重构Toeplitz矩阵,并证明该矩阵的秩不受信号相干性的影响。通过

2018-03-06 10:57:38 0

0 更加多样化。DSP48基本结构如下图所示(图片来源:ug073, Figure 2-1)。DSP48中的核心单元是18x18的乘法器。从图中不难看出,DSP48可实现基本数学函数P=Z(X+Y+CIN

2020-10-30 17:16:51 5768

5768

A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相应的时钟启用输入和复位输入都是保留端口。D和INMODE端口对于DSP48E1片是唯一的。本节详细描述DSP48E1片的输入端口

2022-07-25 18:00:18 4426

4426

扩频码的相关解扩是扩频通信接收机的关键技术之一,主要介绍了数字相关器在全球定位系统(GPS)信号捕获中的应用,并进行了FPGA实现。在设计中,采用了16路并行相关运算的方式加快相关解扩运算速度

2021-01-26 16:22:43 15

15 在DSP48E1列中,级联各个DSP48E1片可以支持更高级的DSP功能。两个数据路径(ACOUT和BCOUT)和DSP48E1片输出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供级联功能。级联数据路径的能力在过滤器设计中很有用。

2021-01-27 07:34:32 8

8 A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相应的时钟启用输入和复位输入都是保留端口。D和INMODE端口对于DSP48E1片是唯一的。本节详细描述DSP48E1片的输入端口

2021-01-27 08:18:02 2

2 DSP48E1片的数学部分由一个25位的预加器、2个25位、18位的补法器和3个48位的数据路径多路复用器(具有输出X、Y和Z)组成,然后是一个3输入加法器/减法器或2输入逻辑单元(参见图2-5)。使用2输入逻辑单元时,不能使用乘法器。

2021-01-29 08:19:37 13

13 在定位系统的时差提取方法中,传统的互相关算法抗噪能力较弱、时差提取精度较低,针对以上缺点,提出卡尔曼-最优阶互相关算法,并且通过仿真对比分析相同条件下该算法和基本互相关算法、广义加权互相关算法的时差

2021-06-18 11:28:06 16

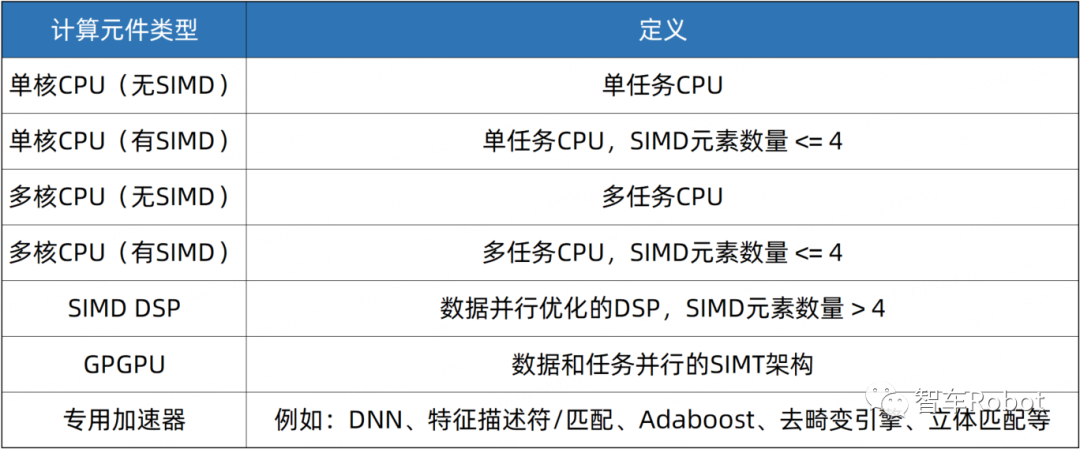

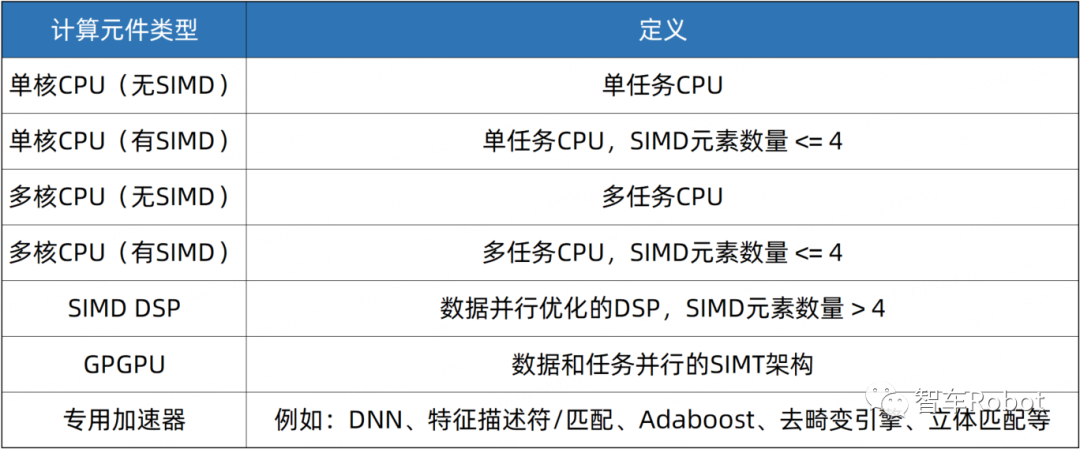

16 元件,如通用CPU、SIMD DSP、GPGPU和专用加速器等。 计算元件特性 •通用CPU适合运行顺序代码和有限的数据并行。 •SIMD DSP处理更数据密集的任务。 •GPGPU也可以处理高数据量和控制顺序灵活的任务。 •专用加速器针对特定操作实现最高执行效率

2023-10-04 10:34:00 262

262

正在加载...

电子发烧友App

电子发烧友App

评论