《UltraFast 设计方法时序收敛快捷参考指南》提供了以下分步骤流程, 用于根据《UltraFast设计方法指南》( UG949 )中的建议快速完成时序收敛: 1初始设计检查:在实现设计前审核

2021-11-05 15:10:26 4603

4603

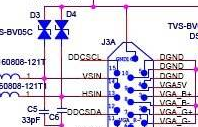

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

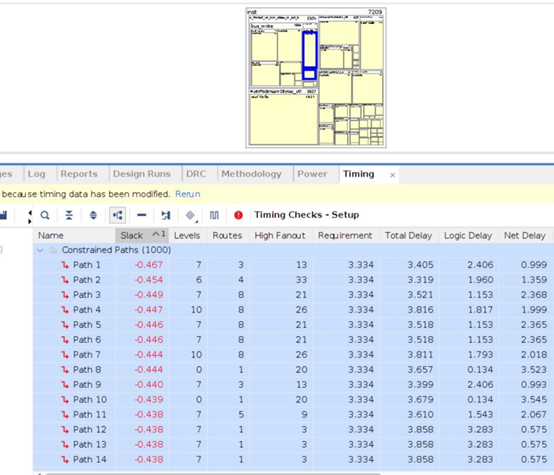

1382 在之前的文章里面介绍了Canny算法的原理和基于Python的参考模型,之后呢在FPGA上完成了Canny算法的实现,可是遇到了时序不收敛的问题,记录一下。

2023-11-18 16:38:28 450

450

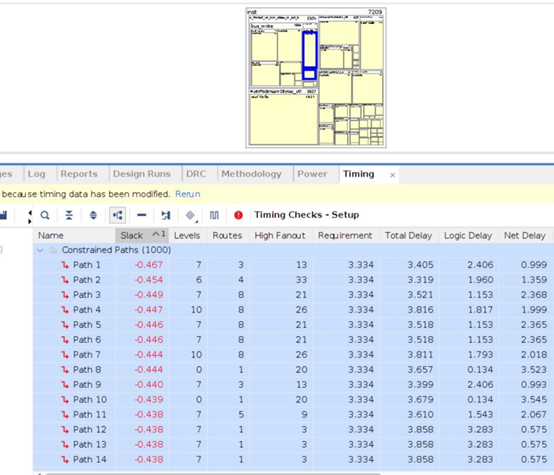

知道“时间分析器”和“planahead”可以帮助我,但我无法理解它的报告。我该怎么做才能解决时间问题。我找不到一些材料来帮助我理解“时序分析”,“代码风格”,“如何纠正时间问题” ','时序收敛'等等

2019-03-18 13:37:27

经过两天的恶补,特别是学习了《第五章_FPGA时 序收敛》及其相关的视频后,我基本上明白了时序分析的概念和用法。之后的几天,我会根据一些官方的文件对时序分析进行更系统、深入的学习。先总结一下之前

2011-09-23 10:26:01

的时序约束。FPGA作为PCB上的一个器件,是整个PCB系统时序收敛的一部分。FPGA作为PCB设计的一部分,是需要PCB设计工程师像对待所有COTS器件一样,阅读并分析其I/O Timing

2016-06-02 15:54:04

(InputDelay、OutputDelay)、上下拉电阻、驱动电流强度等。加入I/O约束后的时序约束,才是完整的时序约束。FPGA作为PCB上的一个器件,是整个PCB系统时序收敛的一部分。FPGA作为

2017-12-27 09:15:17

FPGA毕竟不是ASIC,对时序收敛的要求更加严格,本文主要介绍本人在工程中学习到的各种时序约束技巧。 首先强烈推荐阅读官方文档UG903和UG949,这是最重要的参考资料,没有之一。它提倡

2020-12-23 17:42:10

每日开讲---学习STM32不得不看的剖析(详细分析stm32f10x.h)摘要: 学习STM32不得不看的剖析(详细分析stm32f10x.h)。/**这里是STM32比较重要的头文件***************************************************************************

2021-08-05 07:44:05

本文跟大家一起详细分析一下USB协议。

2021-05-24 06:16:36

上一篇文章中,我们详细分析了VTIM和VMIN的功能,《嵌入式Linux 串口编程系列2--termios的VMIN和VTIME深入理解》 也明白了这两个参数设计的初衷和使用方法,接下来我们 就详细

2021-11-05 07:09:55

在嵌入式Linux专题(一)中已经对嵌入式Linux系统的架构及启动流程有了初步的介绍,本文将详细分析嵌入式Linux系统启动流程。

2021-11-05 09:25:29

DVI接口详细分析DVI 接口规格和定义 DVI 有DVI 1.0 和DVI 2.0 两种标准,其中 DVI 1.0 仅用了其中的一组信号传输信道(data0-data2 ),传输图像的最高像素时钟

2012-08-11 09:51:00

[url=]uboot代码详细分析[/url]

2016-01-29 13:51:41

《FPGA设计时序收敛》,很好的PPT!推荐给大家[hide][/hide]

2011-07-26 11:24:49

个器件,是整个PCB系统时序收敛的一部分。FPGA作为PCB设计的一部分,是需要PCB设计工程师像对待所有COTS器件一样,阅读并分析其I/O Timing Diagram的。FPGA不同于COTS

2017-10-20 13:26:35

三极管特性曲线详细分析,特性曲线看不懂,

2015-06-29 16:34:40

。掌握分析和确定关键路径时序的方法,并通过分析找出关键路径的时序问题,再对关键路径进行优化,通过RTL层面的不断优化,不断修炼自己的设计能力,让设计出来的电路更为靠谱有效!本资料属大西瓜FPGA开发团队,在此开源,与大家一起学习FPGA!

2017-02-26 09:42:48

有谁来解答一下如何去消除综合与时序导致的差异吗?

2021-04-30 06:20:15

如何使用基于图形的物理综合加快FPGA设计时序收敛?

2021-05-06 09:19:08

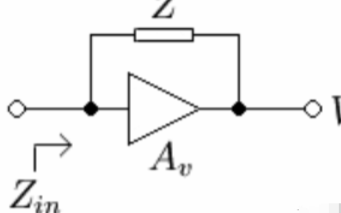

工程师应该掌握的20个模拟电路(详细分析及参考答案)

2013-08-17 09:58:13

工程师应该掌握的20个模拟电路(详细分析及参考答案).pdf

2013-04-07 13:28:38

什么是时序收敛?如何去解决物理设计中时序收敛的问题?

2021-04-26 06:38:50

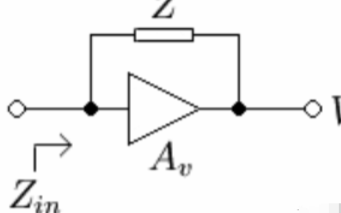

详细分析一下电路原理,尤其是运算放大器和各种三极管的开关作用,电路走向,感激不尽

2017-10-18 16:53:13

求大神详细分析电路图个元器件作用

2013-08-04 15:46:35

求大神详细分析一下,非专业人士,我不懂

2017-01-13 23:43:32

内含参考答案以及详细分析

2023-10-07 07:15:56

本文档的主要内容详细介绍的是硬件工程师必须掌握的20个重要模拟电路的概述和参考答案以及详细分析

2023-09-27 08:22:32

电子工程师需要掌握的20个模拟电路的详细分析

2023-09-28 06:22:26

急 帮帮忙 详细分析

2017-08-27 17:03:30

本帖最后由 eehome 于 2013-1-5 09:52 编辑

电源电路图最最最最最详细分析(转一网友)

2012-07-31 11:37:21

请问各位大神谁有hifi功放电路图详解的资料,电路分析的越详细越好,最好是每一个元件做什么用都能讲到.元件用得越复杂越好.谢谢各位大神了.1.前置放大器电路图,2.功率放大器电路3.HiFi功放电路4.AB类功放

2019-09-27 08:38:09

给大家详细分析一下艾德克斯车载充电机的测试方案

2021-05-08 08:38:05

参考ug612。4.输出时序约束输出就是输入的逆,因此分析的过程是类似的,分类也是类似的。针对时钟的不同,有系统同步和源同步两种。此处不再详细说明。系统同步SDR源同步DDR(一般来说不给约束就可以)5.

2019-07-09 09:14:48

请问一下怎样对stm32的启动代码进行详细分析呢?

2021-11-26 07:10:48

延时开关电路图及详细分析

2019-10-14 09:10:33

`哪个高手能给我详细分析已下逆变器内部构造,主要元器件名称及作用。谢谢!`

2018-12-29 13:23:01

为什么采用高距离分辨力单脉冲技术为可以消除距离闪烁?求业内高手详细分析

2015-06-28 21:30:21

在PCB走线的延时,因此上图只是一个理想过程,即没有考虑PCB走线的延时,而我们的时序分析工具确实将其考虑在内了,所以,我们的FPGA建立时间,除了包括数据保持稳定的时间外,还应加上这段走线延时的时间

2015-03-31 10:35:18

给我们的FPGA做内部时钟,在输出到外部做SDRAM的工作时钟,所以上图中,晶振到外部器件的时钟路径,应该是PLL的输出到SDRAM的输出路径还有,我们之前做的静态时序分析,是基于在FPGA内部的,所以数据

2015-03-31 10:20:00

本文详细分析了ADSL系统中ATM层和物理层之间的UTOPIA LEVEL2接口时序,采用FPGA实现了UTOPIA接口设计,应用在ADSL系统中,数据收发正确,工作稳定;该方案的实现对解决现有专门通信芯

2010-07-28 16:54:10 19

19 延长指纹锁使用寿命的详细分析

进入21世纪,中国的生物识别技术燃起烽火,使指纹锁行业得到了迅速发展。但是某些

2007-10-16 16:15:49 1605

1605 延时开关电路图及详细分析

图1:

2007-11-08 10:20:09 13453

13453 超级电容器原理及电特性详细分析

超级电容器是一种高能量密度的无源储能元件,随着它的问世,如何应用好超级电容器,提高电子线路的性能和研发新的电路、

2009-12-08 08:40:43 4320

4320 笔记本使用十大陋习详细分析

电脑越来越平民化,可是电脑却总是出问题 由于摩尔法则的影响,整个IT产品业界的产品售价正在

2010-01-20 14:18:53 316

316 焊接技术详细分析

焊接实质上是将元器件高质量连接起来最容易实现的方法,对于DIY高手来说,光能掌握电脑配件的性能和参数

2010-01-26 10:46:22 1630

1630 大屏幕显示技术的发展趋详细分析介绍

引言 随着网络技术、计算机信息技术、自控技术在煤炭生产企业的迅速普及,矿井的自

2010-02-21 16:56:17 615

615 电子整流器工作原理详细分析

2010-02-27 10:43:51 24851

24851 施密特触发器原理图解详细分析

重要特性:施密特触发器具有如下特性:输入电压有两个阀值VL、VH,VL施密特触发器通常

2010-03-08 14:23:43 68176

68176 主板设计的5大缺陷详细分析

第1页:显卡声卡不兼容一览

“太惨了!刚买的散热器竟然用不上!”“好郁闷,PCI扩展槽竟然装不上声卡。”

有的时候,我们经

2010-03-15 10:52:21 1509

1509 介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 摘 要: 时序相似搜索被认认最有前途的技术之一然而时序数据是典型的高维海量数据,本内容提供了高效时序相似搜索技术的详细分析

2011-07-27 15:52:49 23

23 uboot 1-1-6版本的 代码详细分析

2015-11-02 11:02:19 25

25 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 十二五规划教材大学电路(邱关源、罗先觉版)二端口网络的详细分析和经典例题以及解题方法

2015-12-23 18:15:36 0

0 电子工程师必须掌握的20个模拟电路详细分析

2016-06-08 17:52:35 34

34 近期的几个单片机例程及详细分析,感兴趣的可以看看。

2016-06-21 17:02:48 3

3 fpga时序收敛

2017-03-01 13:13:34 23

23 采用MATLAB对SPWM进行辅助设计与详细分析和解决方法

2017-09-14 14:22:28 18

18 半桥电源源高频链逆变电路的详细分析

2017-09-14 15:23:44 19

19 DC-DC变换器突加负载时的动态性能研究详细分析与实验验证

2017-09-15 08:45:09 21

21 Buck变换器原理详细分析

2017-09-15 17:26:25 30

30 介绍了一种在多工艺角多工作模式下快速实现时序收敛的技术MCMM(Multicorner-Multimode)技术,该技术将工艺角和模式进行组合,对时序同时进行分析和优化,到达快速实现时序收敛的目的

2017-10-20 15:21:11 3

3 一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2326

2326

问题的恼人之处在于没有哪种方法能够解决所有类型的问题。由于客户对于和现场应用工程师共享源代码通常非常敏感,因此我们通常都是通过将工具的潜力发挥到极致来帮助客户解决其时序问题。

2017-11-24 19:49:44 9123

9123

滤波电容器、共模电感、磁珠在EMC设计电路中是常见的身影,也是消灭电磁干扰的三大利器。对于这这三者在电路中的作用,相信还有很多工程师搞不清楚。本文从设计设计中,详细分析了消灭EMC三大利器的原理。

2017-12-01 10:12:13 11403

11403

OpenWrt是一个开放的linux平台,主要用于带wifi的无线路由上。类似于Ubuntu、Red Hat、之类的linux发行版本,它也有一套自己的启动流程。本文主要介绍了openwrt启动过程及详细分析。

2017-12-27 09:17:39 12398

12398

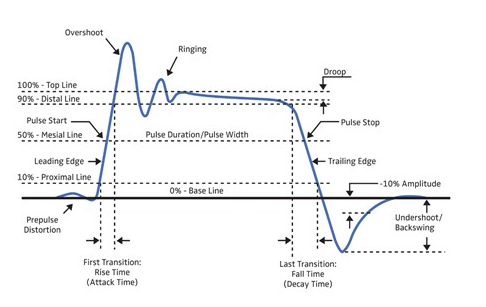

降低通信应用开发风险”将详细分析高速通信和数据中心的时序要求,并介绍Silicon Labs经市场验证的时钟振荡器解决方案,帮助工程人员克服日益艰钜的高速网络定时设计挑战。

2018-01-26 16:20:52 7551

7551 FPGA时序收敛让你的产品达到最佳性能!

2018-04-10 11:38:48 18

18 物联网的产业生态是怎样的详细分析概述

2018-12-08 10:00:07 4642

4642 本文档的主要内容详细介绍的是绘制原理图的基本规测和各种电气控制原理图详细分析。

2019-08-25 11:36:36 5477

5477 本文档的主要内容详细介绍的是硬件工程师必须掌握的20个重要模拟电路的概述和参考答案以及详细分析

2019-11-13 16:24:26 133

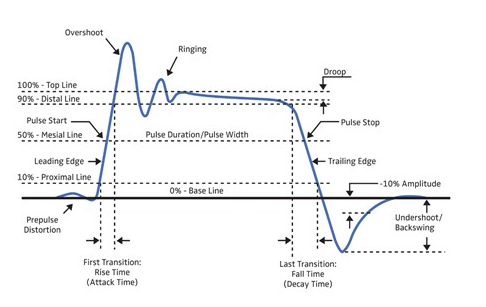

133 Boonton的功率表非常详细的波形跟踪可实现精确的测量,有效的校准,以及对线性和脉冲射频部件及系统的详细分析。

2020-01-10 09:56:00 847

847

本文档的主要内容详细介绍的是电子电路的复习题详细分析

2020-04-15 08:00:00 15

15 本文档的主要内容详细介绍的是一些开关电源的拓扑结构详细分析。

2021-01-06 00:16:00 20

20 电子发烧友网站提供《华为Mate40Pro的拆解报告详细分析.pdf》资料免费下载

2020-11-26 07:01:00 89

89 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 18

18 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束利序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是重点。只有约東正确才能在高速情况下保证FPGA和外部器件通信正确

2021-01-13 17:13:00 11

11 本文档的主要内容详细介绍的是FPGA的时序分析的优化策略详细说明。

2021-01-14 16:03:59 17

17 本文档的主要内容详细介绍的是FPGA的时序分析的优化策略详细说明。

2021-01-14 16:03:59 19

19 本文档的主要内容详细介绍的是如何实现LTE无线网络优化案例的详细分析。

2021-01-14 16:55:41 21

21 本文档的主要内容详细介绍的是功率放大电路的仿真资料详细分析。

2021-02-01 11:28:50 28

28 电子发烧友网为你提供隔离设计中的共模 (CM) 噪声详细分析资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-31 08:41:49 9

9 ,能够有效减少时序路径问题分析所需工作量。 时序路径问题分析定义为通过调查一条或多条具有负裕量的时序路径来判断达成时序收敛的方法。当设计无法达成时序收敛时,作为分析步骤的第一步,不应对个别时序路径进行详细时序分

2021-05-19 11:25:47 2677

2677

正激有源钳位的详细分析介绍。

2021-06-16 16:57:07 56

56 本文介绍了米勒效应的由来,并详细分析了MOSFET开关过程米勒效应的影响,帮助定性理解米勒平台的形成机制。最后给出了场效应管栅极电荷的作用。

2022-03-10 14:44:18 6226

6226

本文旨在提供一种方法,以帮助设计师判断给定模块是否能够在空裸片上达成时序收敛。 如果目标模块无法在空裸片上达成非关联 (OOC) 时序收敛,则恐难以与设计其余部分达成关联性时序收敛。设计师可从完整

2022-08-02 11:37:35 318

318

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

2022-08-02 09:25:06 425

425

FPGA时序不收敛,会出现很多随机性问题,上板测试大概率各种跑飞,而且不好调试定位原因,所以在上板测试前,先优化时序,再上板。

2023-06-26 15:41:31 1112

1112

电子发烧友网站提供《UltraFast设计方法时序收敛快捷参考指南(UG1292).pdf》资料免费下载

2023-09-15 10:38:51 0

0

电子发烧友App

电子发烧友App

评论