嗨专家,我有一个名为WAKEUP_N的信号,它有一个单独的上拉至3.3V辅助电压,总是3.3V,无论FPGA上电还是下电。当FPGA断电时,WAKEUP_N会低吗? FPGA IO和GND之间是否存在低阻抗路径?如果我在FPGA中将此引脚设置为输入,输出或高阻,那么会有什么区别吗?谢谢克里斯

2020-08-06 10:07:49

`FPGA 上电配置时候IO口会有一个短暂的3.3V 10ms 的电平,导致我控制端出现问题,我想问下如何可以避免这个电平`

2020-11-23 10:31:40

FPGA上电瞬间IO管脚输出的高电平怎么消除呢?

2023-04-23 14:48:08

设计、引脚分配产生非常重要的影响。这篇专题就针对FPGA从上电开始 ,配置程序,到正常工作整个过程中所有IO的状态进行分析。 从时间阶段可以分为两部分,第一阶段是从FPGA上电开始直到配置

2021-01-08 17:29:15

我用的TPS54618给xilinx公司XC5VLX110提供IO3.3的电压,电路图是由webench生成的,发现的问题如下:PCB上电后,测量所有的电压都正常,给FPGA烧写程序成功,断电后发现

2019-03-19 07:34:20

`关键内容提要:(1) FPGA IO命名方式;(2) FPGA的上电时序 今天想和大家一起聊聊FPGA的IO。先说说我当年入门的经历吧。国内的大学有FPGA开发条件的实验室并不太多,当年大学的那帮

2019-07-18 14:26:01

关键内容提要:

(1)FPGA IO命名方式;

(2)FPGA的上电时序

今天想和大家一起聊聊FPGA的IO。

先说说我当年入门的经历吧。国内的大学有FPGA开发条件的实验室并不太多,当年大学的那帮

2023-11-03 11:08:33

FPGA程序写完编译已用94%的资源。下载没有问题,上电后,有时正常运行,有时一上电没有现象,示波器看管腿的波形也没有,怀疑FPGA没有工作,有时epcs4的程序没有正确下载。量了FPGA的供电也都正常。到底是什么问题呢?

2015-01-08 15:18:37

cyclone fpga jtag突然不能下载程序,测量了一下电压,发现上电后 ,nstatus管教一直是低电平,其他供电正常 ,这是为什么呢?求帮忙解答,谢谢了

2016-09-27 20:40:03

请问 AD2S1210 上电后,不编程,会输出一个默认的激励频率吗?

2024-01-15 06:30:35

AD2S1210重新上电后,默认激励频率不为10kHz,而是二十几千赫兹,请问是为什么?

2023-12-08 06:43:56

AD9601加电后通过SPI配置寄存器,写完成后为什么读出来寄存器的状态不变,一直是默认值,但实际上配置的状态是有响应的,测试过程中,单独配置过0x00、0x14、0x16、0x17这些地址,但读出来的值却一直是默认值,不管写的是什么值,这是为什么

2019-01-11 07:13:37

采用AD9789,遇到以下问题,求大神解答!上电手动复位后,对芯片进行写操作无响应,无论写入什么数据,读取状态寄存器结果都是0xFF,示波器观察SPI管脚时序无误,上电后,不进行任何配置,从SDO

2018-11-14 11:02:18

各位工程师:

大家好!最近在用ADXL362做一款手环设备。请问大家一下,当芯片上电初始化后各个引脚状态是什么状态?

希望得到大家的帮助或者相关的资料,谢谢大家

2023-12-29 07:47:17

学习的时候了解到FPGA的多路供电要求一定的上电断电顺序,目前在搞Altera的Cyclone IV系列的FPGA,主要有内部逻辑供电VCCINT,PLL供电VCCD_PLL,IO口供电VCCIO等

2017-05-18 22:36:29

刻刀割断了VDDA(pin40)的走线,即VDDA现在是悬空的。上电后测量3V电压是OK的,电流也在正常范围内(mA级),SWD烧写程序显示为成功,请问是否有潜在的风险影响?

2024-03-18 06:26:43

割断了VDDA(pin40)的走线,即VDDA现在是悬空的。上电后测量3V电压是OK的,电流也在正常范围内(mA级),SWD烧写程序显示为成功,请问是否有潜在的风险影响?

2023-08-07 13:28:30

请问一下,CC3200在进入STANDBY模式后,所有IO处于什么电平状态呢?

按照以往使用其它芯片的情况,睡眠后,IO都是恢复到输入上拉高电平的状态。

而在CC3200开发板上运行的程序,进入

2018-06-21 13:43:49

CH579 GPIO上电后默认是什么状态? 高电平?低电平?高阻态?空闲模式、暂停模式、睡眠模式、下电模式;各模式下gpio 状态能保持吗?如果不能保持 唤醒后 gpio 是什么状态?有没有详细说明文档?

2022-08-16 06:24:08

上电默认配置是 PGA=128、 DataRate=10Hz。

2020-02-29 10:57:35

1.81v,问题二:手压FPGA芯片,FPGA提示配置成功,但是板子跑不起来;问题三:(1)如果是虚焊问题,问什么手压状态下,IO连接的LED灯状态也异常不亮,正常情况下:上电后IO状态应为高阻态, LED

2017-06-05 11:48:20

请问KL25的GPIO上电后默认是上拉还是下拉的,规格书中没有找到。看下有没有知道的,帮忙解释一下。多谢!

2015-02-12 10:24:43

M032芯片的所有GPIO在MCU上电过程直到完成reset的这段过程中,是什么状态?项目需要用GPIO控制多个外部IO,需要在设备上电过程中有明确的IO状态。

I/O Initial State

2023-08-21 07:38:50

PB23/RST,PB22/BOOT这两个引脚如果不进行配置默认上电是什么状态,是RST和BOOT的功能吗?还是需要对这两个端口进行上电初始化启用复用功能才会有这两个功能?

2022-05-25 07:08:42

软件模式

1)上电后默认的内部工作时钟是内部自己产生的还是外部MCLK?IIC工作必须要有外部时钟输入才行吗?

2)LDO_OUT输出的电压测量过好像在1.6V左右,并不是1.8V,目前我

2023-11-30 07:26:28

在某种状态,导致上电时没能进入到启动程序的状态。加大R53的值,VCC引脚还是有电压,但是已经在0.4V左右。此时单片机就可以正常启动。要想彻底解决这个问题,就是需要连接到单片机的IO引脚,在上电前

2020-12-28 17:07:01

STM32 IO口设置成推挽输出来控制光耦,从而控制继电器,现在采用的是灌电流的方式,但是一上电默认电平为低电平,我只能在程序里初始化函数后直接拉高,但是还是怕出现瞬间上电的现象,怎样能让他一上电到稳定的状态为高电平,在继电器那边加一个下拉电阻这样可行么

2022-05-05 16:51:59

如题,上电过程,到IO口被初始化前,是什么状态,在芯片手册什么地方有说明,这个没有找到

2024-03-11 07:54:47

STM8 芯片上电前用户使用的寄存器状态都会自动默认是0吗?

2023-10-13 07:58:02

焊接完第一次下载程序可以识别芯片,下载后重新上电,就会出现有时无法启动的状态,此时仿真器也无法识别CPU,正常工作电源显示负载电流11mA,若无法启动电流16mA,略有上升。

1.芯片是正规渠道

2024-01-12 06:14:20

上电后GPIO引脚的默认电平是什么,是3.3V吗?假如我用bbb连接继电器,引脚连接光耦采用上拉3.3v的情况下。会不会在复位时引起继电器动作?外接光耦的3.3V如果是另外的电源(比如1117),会不会上电时会损坏BBB的引脚。

2017-04-06 11:08:34

用了好长时间这款片子了,最近做了个设计,但是由于未考虑到下载IO状态问题(就是通过JTAG将MCS文件下载至Flash,上电由Flash加载时通过某引脚可配置,但与下载时不同),结果出现问题,输出

2016-10-16 22:07:59

包含ETX(或者x86等CPU)以及FPGA,由于一般PCI接口通过FPGA来控制实现,所以如果系统上电后FPGA的配置、初始化时间太长势必影响到板卡CPU对于PCI总线接口的访问,而且大部分情况下系统

2015-01-22 14:41:34

本人菜鸟一枚,自己做了一个LQFP封装的stc89c52的最小系统板,但上电后初始状态下除了P1为高电平口别的P2 P3 口都为低电平,不应该默认初始复位值都应该是高电平吗?为什么会这样?望大佬解答

2019-10-30 04:35:27

为GPIO管脚同时配置上拉电阻和下拉电阻。大部分单片机单个电阻的值约为100 kΩ。上电后,默认为所 有GPIO

2022-02-11 07:58:10

例说FPGA连载12:状态初始——复位电路特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc FPGA器件在上电后都需要有一个确定的初始

2016-07-25 15:19:04

单片机IO默认低电平,怎么上电后测量是高电平

2023-10-20 07:32:25

请教各位大佬,在stm32上电后,初始化GPIO之前,GPIO的状态是否都是floating的状态,必须要外加上拉或者下拉才能固定电平,否则会出现不定态或者毛刺,这一点在spec中有提到吗?

2024-03-20 07:18:19

,因此需要设计者特别关注上电时序。针对XILINX FPGA的上电通常需要遵循以下规则: (1)在PS端,Vccpint,Vccpaux,Vccpll一起上电,后启动PS的Vcco电源

2020-12-23 17:44:23

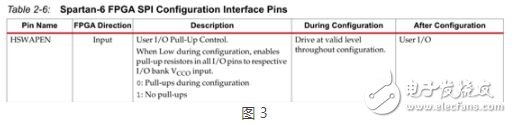

大家好, 我在spartan-6 FPGA(XC6SLX9TQ144)板上遇到了问题。我发现我的FPGA的所有io引脚在配置之前都处于高位状态。但是我需要它们低。我不知道究竟是什么原因。我

2019-07-26 12:00:25

你好,在我们的研究中,我们正在探索FPGA器件上SRAM的上电状态的固有随机性。因此,我们现在正试图在启动后从aVirtex-5器件读出分配的RAM值。但是,根据“Virtex-5 FPGA配置指南

2020-06-18 09:26:09

stm32的IO理解:STM32中空的I/O管脚是高电平还是低电平取决于具体情况。1、IO端口复位后处于浮空状态,也就是其电平状态由外围电路决定。2、STM32上电复位瞬间I/O口的电平状态默认

2022-01-25 07:28:43

最近在用AD7768在做数据采集,采用FPGA控制和处理转换后的数据,但是将FPGA和AD7768端口链接后,每次上电AD都会发烫 ,断开连线后正常,这是怎么回事

2018-08-06 09:17:15

怎么确定STM32上电后某个寄存器的初始状态

2023-10-13 06:01:25

实验中发现在如果在初始是不给FPGA的IO引脚执行操作,默认的输出时高电平,怎么回事呢?想设成是低电平,该怎么办?

2023-04-23 14:49:12

包含ETX(或者x86等CPU)以及FPGA,由于一般PCI接口通过FPGA来控制实现,所以如果系统上电后FPGA的配置、初始化时间太长势必影响到板卡CPU对于PCI总线接口的访问,而且大部分情况下系统

2015-01-20 17:37:04

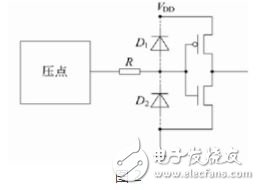

当没有电源给该组时,我无法找出IO引脚的状态。 Spartan 6 SelectIO用户指南告诉我以下内容VCCINT(1.2V),VCCAUX和VCCO电源可以按任何顺序应用。在FPGA启动配置

2019-06-28 10:36:33

本人做课设,想用FPGA输出一个方波作为时钟信号,使用FPGA的是Altera公司的EP1C12Q240I7,配置芯片是EPCS4I8,我用QuartusII下载了程序之后,发现只有上电和手动复位后

2016-12-08 16:20:03

AD2S1210重新上电后,默认激励频率不为10kHz,而是二十几千赫兹,请问是为什么?

2018-07-31 08:27:59

源电压。此时接入输入后,运放输出正常。断开输入电源后,运放输出为0V左右,正常。即异常只出现在输入悬空状态时的上电后。1、保持电路不变,更换之前使用的运放,没有异常,输入悬空状态下上电后运放输出为0V左右

2018-08-14 07:20:54

各位大侠: 请问CC2541 的IO上电的什么状态。我用P0_6作为输出,发现每次上电都会输出短暂的高脉冲。仿真时,程序还没跑就输出高电平;设置断点看,发现一直初始化IO才不会输出高电平

2019-10-08 09:15:17

请问CPLD/FPGA上电初始时IO口的状态是怎么样的呢?

2023-04-23 14:26:44

芯片DSP2812,初始化一些管脚为普通IO口,方向是输出引脚,没有指定状态,请问引脚此时的默认状态是什么电平,是否与内部结构有关,内部弱上拉电阻或者下拉电阻?(外部没接上拉或者下拉电阻)

2020-07-20 07:49:47

请问TMS320F***在上电时IO口管脚状态默认是输入还是输出方式?如果是输出是默认是高电平还是低电平?是否有相关文档介绍?盼回复,谢谢!

2018-09-14 10:44:58

M0516 上电IO电平状态在哪有描述?能否设置?

2023-08-25 07:42:03

软件模式1)上电后默认的内部工作时钟是内部自己产生的还是外部MCLK?IIC工作必须要有外部时钟输入才行吗?2)LDO_OUT输出的电压测量过好像在1.6V左右,并不是1.8V,目前我设计使用内部

2019-03-07 10:57:23

请教:STM32F4 上电时,IO口是什么状态 ? 高电平?低电平 ?还是其他的状态?谢谢 !

2018-10-19 08:33:06

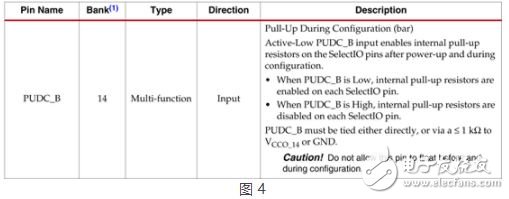

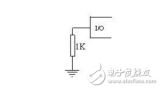

您好!我目前用的是TMS320C6748芯片,想问一下这个芯片能不能通过某个引脚上下拉来配置上电瞬间(程序还没运行起来)的所有IO电平状态的呢?我看到技术参考手册中可以通过配置PUPD_SEL

2019-08-22 12:14:12

本帖最后由 一只耳朵怪 于 2018-6-14 10:48 编辑

请问TMS320F28035上电过程中是否将IO口设置为输入状态?上拉电阻多大?

2018-06-14 06:26:13

TMS320F28335 上电初期代码没有开始控制引脚的默认状态,可能会触发被控对象误动作。如何设置上电初期引脚默认状态为底呢?

2018-08-31 15:18:28

(Bank 15)进行电压切换(3.3V至1.8V)。在默认上电顺序中,XC7K160T IO Bank 15以3.3V的速率上升。后来我们要求将IOs电压从3.3V切换到1.8V。使用Kintex-7可以

2020-04-28 10:17:52

AVR单片机IO口初始化PORT和DDR两个寄存器值0X00,表明为高阻态的输入状态。我想修改这个默认设置,例如,上电复位后,默认IO为输出口,输出高电平

2019-06-26 05:56:08

我对一些问题很困惑。(1)上电后寄存器的状态是“1”还是“0”?(2)下载.bit文件后寄存器的状态是什么?它与代码有什么关系吗?我的意思是reg a = 1'b1。(3)在上述情况下,io引脚怎么样?谢谢

2020-06-14 11:51:03

喜我在我的项目中使用xc7z020-clg484。早期上电状态下IO引脚的状态是什么?我期待所有IO引脚都处于高阻态,直到我在程序中用逻辑低电平或逻辑高电平初始化它?谢谢&问候卡萨拉加内什

2020-08-27 08:31:45

重置后通用输入/输出(GPIO)的默认状态是什么

2020-11-23 12:13:21

:Altera CPLD的IO在上电后复位前处于弱上拉状态。也难怪出现这个高电平,而且对背光产生了作用。弱上拉已成事实,那解决的办法有一个,加个下拉,电阻要远小于上拉。而看看电路,原本就有一个

2011-07-21 08:49:22

IO口状态切换说明

2009-04-01 18:50:12 22

22 c51单片机上电后io口默认的电平默认都是高电平,因为只不过P0没有内部上拉电阻,是弱上拉,不加外部上拉电阻的话只能驱动外部的门电路。P1到P3都有上拉电阻,是强上拉,可以直接驱动外部的接口电路。

2017-11-21 16:08:31 10027

10027

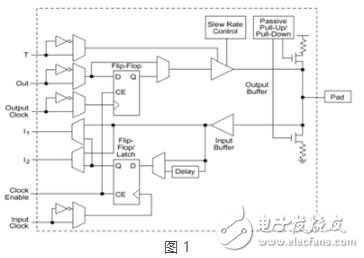

在进行FPGA硬件设计时,引脚分配是非常重要的一个环节,特别是在硬件电路上需要与其他芯片通行的引脚。Xilinx FPGA从上电之后到正常工作整个过程中各个阶段引脚的状态,会对硬件设计、引脚分配产生非常重要的影响。这篇专题就针对FPGA从上电开始 ,配置程序,到正常工作整个过程中所有IO的状态进行分析。

2020-09-02 09:20:21 12353

12353

介绍IO口与FPGA管脚对应关系表。

2021-03-18 10:02:26 12

12 由STM32切换到LPC1788,发现LPC的IO未初始化时输出高电平,初始化后才能拉低,这样和STM32的设计就不兼容了。分析查LPC数据手册后,发现:复位状态为输入模式,上拉模式。后面也有具体

2021-11-17 09:21:03 2

2 关于 FPGA 的 IO资源分析共分为三个系列进行具体阐述,分别为: IO资源:分析FPGA IO资源的电气特性; IO逻辑资源:分析FPGA的输入输出数据寄存器、DDR工作方式、可编程输入延时

2022-12-13 13:20:06 1099

1099

电子发烧友App

电子发烧友App

评论