1、引言

随着图像处理、工业控制、无线通信等领域的飞速发展,对数据采集系统的速度、精度等性能要求也越来越高。这些要求都对数据采集系统的设计和实现提出了新的挑战。目前数据采集系统的设计方案通常分为以下几类:

1)以微处理器单一控制芯片和A/D转换器形式为主,该设计方案简单,在对性能要求不高的应用场合为了降低成本甚至可以采用集成A/D转换器的微处理器。

2)采用通用计算机配置数据采集卡的方式,通常需要开发计算机端应用程序,可以完成复杂的计算,但不同的采集卡相应的驱动程序不同,如果需求改变需要更换采集卡时,相应的应用程序也需要重新开发。因此,该设计方案通用性差,实时性不高。

3)以ARM和FPGA或DSP和FPGA组合方式作为采集系统的核心,ARM处理器适合控制领域,DSP处理器适合信号处理领域,FPGA器件由于其自身特点,适合高速并行采集与处理领域,具有ARM或者DSP等处理器无法比拟的优势。这类组合方式结合各自特点,处理能力强,应用范围广。

ARM和FPGA之间的数据交换采用双口RAM芯片来实现FIFO功能。系统中ARM处理器作为系统控制核心,负责控制整个系统工作时序、并将数据通过网络上传到服务器中进行存储。FPGA负责A/D转换器的模式配置,数据传输。该组合方式结合ARM在控制方面和FPGA在采集方面的优势,具有通用性强、配置灵活的特点。

2、系统设计

本系统硬件主要由信号调理电路、模数转换器ADS1278、FPGA器件CyCLOnE系列EP1C6、双口RAMIDT7205和处理器PXA270及外围电路组成,系统结构框图如图1所示。输入信号经过信号调理电路后,进入A/D转换器进行数据转换,将模拟信号转换成23位尾数和一符号位的数据,FPGA配置A/D转换器并将转换的数据按照顺序存储到双口RAM中,当转换数据存储满后中断ARM处理器,ARM处理器将数据从双口RAM读出进行运算,并通过网络接口将采集数据传输到服务器。

图1 系统结构

2.1、24位A/D转换芯片ADS1278

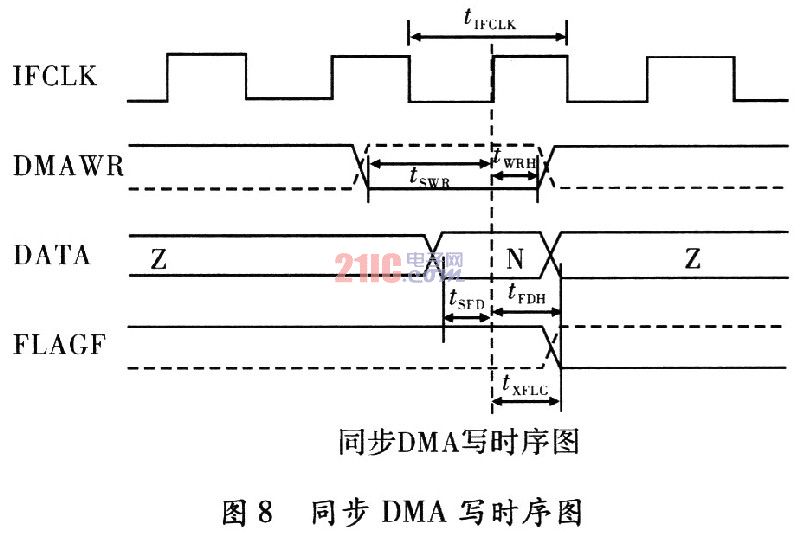

ADS1278是德州仪器(TI)公司推出的采样率高达128KS/S、24位8通道同步采样Σ-ΔADC。支持多种工作模式,内部集成线性相位数字滤波器,数据输出接口支持SPI或可选帧同步,便于与FPGA互连。可满足国防、航天和医疗应用。

ADS1278转换器内部集成的数字滤波器通过奈奎斯特采样将输入信号抽取为长度为1比特的高分辨率数字信号。8通道输入信号分别进入独立的8个A/D转换器,它内部由高阶斩波器、数字滤波器、调制器组成,可将输入模拟信号经过高阶滤波器后得到数字信号。图2为ADS1278的SPI格式下,时钟和数据时序图。

图2 SPI格式下时序

2.2、ARM与FPGA的接口设计

本系统核心采用ARM和FPGA的组合方式,在ARM和FPGA之间采用3片双口RAMIDT7205进行24BIT数据传输,其中,FPGA器件控制A/D转换,并将转换数据按照一定顺序存储到双口RAM中,当数据存储完后将中断ARM,ARM将双口RAM中的数据进行读取,比使用FIFO传输的方案降低了成本、提高了数据传输的吞吐量。

本系统中FPGA的设计作用如下:复位并配置ADS1278的工作模式,FPGA内部设置一个地址加法器控制将A/D转换器的数据写入双口RAM中,当双口RAM写满后,大小24KB,地址加法器复位。ARM与FPGA的接口方式有很多种,如IIC、SPI等串行接口或总线等并行接口,串行接口由于本身的局限性限制了其在大数据量、实时数据的传输的应用,而总线的形式更合理一些,稳定性较之更好一点。但ARM与FPGA通过地址、数据、控制总线直接连接的方式在大数据传输时会影响系统的效率,因此,在ARM与FPGA之间采用双口RAM进行连接的方式,ARM与FPGA异步工作,提供了系统的效率。其接口如图3所示。

图3 ARM与FPGA的接口

FPGA的控制信号WR、RD、nRESET与双口RAMIDT7205的复位信号RS、读写信号WR和RD连接,数据总线D0~D23与双口RAM的数据总线连接,FPGA通过内部地址加法器依次将将A/D转换器的数据串并转换后写入双口RAM中。双口RAM的EF、HF信号分别与PXA270的GPIO0和GPIO1连接,接受数据写满后产生的中断。PXA270提供6个分区的静态存储器BAnK0~BAnK5,设计将双口RAM的存储空间映射到PXA270的BAnK3上。

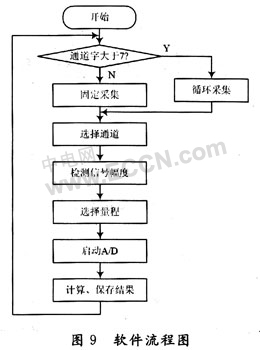

3、驱动程序设计

为了实现ARM与FPGA通过双口RAM的数据传输,需要设计嵌入式LInux下的驱动程序。当FPGA将数据写到双口RAM中,根据双口RAM中数据的状态中断ARM处理器进行数据读取。这一过程主要需要中断和总线驱动程序配合。

在中断驱动程序中,通过REquEST_IRq()函数为双口RAM的中断分配中断请求(IRQ)号,当处理器检测到这一IRQ号对应的中断产生时,将启动该IRQ对应的中断服务例程[9]。IRQ号与中断处理例程是一一对应的,在系统/PORC/InTERRuPTS文件中可以为设备选择IRQ号。FP-GA将A/D转换的数据写入双口RAM后,当数据写满后会中断ARM处理器,ARM会响应中断处理例程,读取双口RAM中的数据。中断处理例程首先要清除PXA270的中断寄存器相应的位,需要通过对状态寄存器相应位进行写操作,这是为了能够继续响应双口RAM产生的中断。然后是设置数据传输标志位,当主程序中检测到标志位,进而调用总线驱动程序进行数据传输,这种工作方式可以避免中断处理例程的冗长,提高系统传输效率。

由于应用程序工作在用户空间,它无法完成对总线的操作,而驱动程序工作在内核空间,可完成对总线的操作,因此,在总线驱动程序中,必须支持应用程序对总线的操作,以完成数据的传输。传统的LInux应用程序需要通过总线驱动程序完成对总线空间的访问方法是通过2个函数完成用户空间与内核空间之间的数据传递,其中内核空间向用户空间传输数据使用COPy_FROM_uSER函数,用户空间向内核空间传输数据使用COPy_TO_uSER函数。COPy_FROM_uSER,COPy_TO_uSER等。这种方法虽然能完成2个空间的数据传输,但是效率不高,最好的方法是将内核空间能访问的物理地址直接映射到用户空间,LInux内核提供了REMAP_PAGE_RAnGE函数,应用程序对该用户空间的地址访问相当于直接对物理地址的访问。本文的总线驱动程序就是直接映射的方法,来完成快速的读写。

下面是驱动程序代码段,它使用REMAP_PAGE_RAnGE()函数在驱动程序中完成MMAP系统调用中物理空间到虚拟空间的映射,REMAP_PAGE_RAnGE()函数原型如下:

InTREMAP_PAGE_RAnGE(vMA_AREA_STRuCT*vMA,un-SIGnEDLOnGFROM,unSIGnEDLOnGTO,unSIGnEDLOnGSIzE,PG-PROT_TPROT);

REMAP_PAGE_RAnGE()函数的调用需要初始化。

虚拟内存空间指针vMA、起始地址、物理地址、映射区域字节数等参数。首先计算物理地址,然后通过右移PAGE_SHIFT位,本系统使用PXA270的BAnK3的物理空间,起始地址0x0C000000,大小为4KB映射到虚拟空间。驱动程序中,还需要判断虚拟内存大小和偏移了指定距离后物理内存的大小,如果虚拟内存过大,应该返回并提示映射超出允许的内存空间。

调用REMAP_PAGE_RAnGE()函数过程如下:REMAP_PAGE_RAnGE(vMA,vMA->vM_START,0x0C000000+vMA->vM_PGOFF<<PAGE_SHIFT,vMA->vM_EnD-vMA->vM_START,PGPROT_nOnCACHED(vMA->vM_PAGE_PROT));

应用程序中调用MMAP系统就是对MMAP()函数的参数初始化。MMAP()函数原型如下:

void*MMAP(vOID*START,SIzE_TLEnGTH,InTPROT,InTFLAGS,InTFD,OFF_TOFFSET);

首先将文件描述符FD指定的设备文件与START处开始的内存空间关联,通常将START设为0,MMAP()函数返回实际关联的内存地址。LEnGTH为内存映射的字节长度,PROT为内存保护类型,FLAG为映射类型,MAP_SHARED标识符表示与其他所有映射这个对象的进程共享内存区域。本设计调用MMAP()函数过程如下:

BASE=(unSIGnEDLOnG*)MMAP(0,0X100,PROT_READ|PROT_WRITE,MAP_SHARED,FD,0);

4、系统实验结果分析

本系统中,FPGA外部晶振频率采用32.768MHz,经过内部16分频器后得到2.048MHz时钟频率作为ADS1278的工作时钟。ADS1278完成8通道24位精度的采样传输大约需24μS,采样数据被FPGA写入双口RAM基本在采样结束后同步完成。当双口RAM数据被写满后,中断ARM处理器进行数据读取,ARM的工作频率为520MHz,外部总线时钟频率为104MHz,配置PXA270外部BAnK3的MSC寄存器为0x7FF4满足系统对双口RAM时序读写的需要。

为了提高采集精度,首先需要对A/D转换器进行零偏校准,零偏校准后,通过动态范围计算公式20×LG(信号电压/噪声电压)得到各通道实际动态范围如表1所示。其中零偏电压以转换后的数字形式给出。从表1中动态范围一列中可以看出,系统各通道实现的动态范围都接近A/D转换器24位采样精度时的理想动态范围111DB,测量结果表明本文设计的系统可充分发挥A/D转换器高精度、大动态范围的特性。

表1 各通道参数

系统测量加速度信号各通道显示界面如图4所示,从图中可以看出,加速度信号实时、连续地显示验证了本文提出的采用双口RAM作为ARM与FPGA之间的数据传输方式及相应的总线、中断驱动程序的正确性和可行性。该方案也可应用于电力频率测量等其他高精度采集领域。

图4系统采集显示界面

5、结论

充分利用ARM和FPGA各自的优势,设计一种ARM和FPGA组合的高精度数据采集系统,采用双口RAM设计了ARM与FPGA之间的数据传输方式,解决了使用传统FIFO芯片成本高、容量小的问题,提高了ARM与FPGA传输吞吐量。编写了LInux下设备的驱动程序,采用中断方式及用户空间对内核空间的直接访问方式进行数据传输,大大提高了系统传输的效率。设计的基于双口RAM的ARM与FPGA采集系统具有成本低、精度高、动态范围大等特点,是高精度采集处理的一种高效可行的解决方案。

电子发烧友App

电子发烧友App

评论