随着SystemVerilog成为IEEE的P1800规范,越来越多的项目开始采用基于SystemVerilog的验证方法学来获得更多的重用扩展性、更全面的功能覆盖率,以及更合理的层次化验证结构

2014-03-24 14:07:47 2929

2929 的。此外,设计不断地重用,而验证也希望能够重用一样的验证模块,这就催生了层次化的验证方法。Synopsys的 VMM验证方法学提供了基于SystemVerilog的

2023-08-25 16:45:55 586

586 的。此外,设计不断地重用,而验证也希望能够重用一样的验证模块,这就催生了层次化的验证方法。Synopsys的 VMM验证方法学提供了基于S

2023-08-29 17:00:51 490

490 ,南无设计流程可能会出现冗余。作为验证工程师,你的工作是阅读同样的硬件规范并对其含义做出独立的判断,然后利用测试来检查对硬的RTL代码是否与你解读的一致。1.2 基本测试平台的功能测试平台的用途在于确定

2020-12-03 18:45:39

、2005三个版本verilog较VHDL更有前景:具有模拟电路描述能力、不仅可以开发电路还可以验证电路、门级以下描述比VHDL强RTL级和门级的综合已经成熟,主要是注意行为级的综合结果,使用可综合

2012-01-12 15:15:21

可重用机床编码技术及重构算法研究摘要:在产品开发过程中80%的设计工作是在重用的基础上进行的。设计重用能够缩短产品开发周期、降低设计成本和避免重复性错误。本文从可重用机床的模块分析入手,详细分析了可

2009-05-17 11:58:53

不太熟悉 HDL 验证概念的人。它使用与 UVM 相同的设计重用和功能验证概念,但使用 Python 实现。 VHDL、Verilog和 System Verilog 等硬件描述语言仅用于可综合

2022-02-13 17:03:49

.......................................51.5 Verilog 良好编程习惯........................................62基于 ALTERA 的 ASIC 验证

2015-09-18 15:26:25

重来。因此,仿真在整个验证中的重要性可见一斑。(特权同学,版权所有)提到仿真,我们通常会提testbench的概念。所谓testbench,即测试平台,详细的说就是给待验证的设计添加激励,同时观察它

2019-04-10 06:35:34

DUT的输出并把它们传递给scoreboard,完成这个功能的是monitor。验证平台要能够给出预期结果。在记分板中提到了判断的标准,判断的标准通常就是预期。假设DUT是一个加法器,那么 当在它

2020-12-02 15:21:34

本帖最后由 IC那些事儿 于 2020-12-4 15:50 编辑

上次更新完《IC验证"UVM验证平台"组成》后本打算不再更新......但有人反映要继续更新...继续

2020-12-04 15:48:19

验证的基本常识,将会散落在各个章节之间。UVM的一些高级功能,如何灵活地使用sequence机制、factory机制等。如何编写代码才能保证可重用性。可重用性是目前IC界提及最多的几个词汇之一,它包含

2020-12-01 15:09:14

IC验证平台

2021-08-09 07:39:47

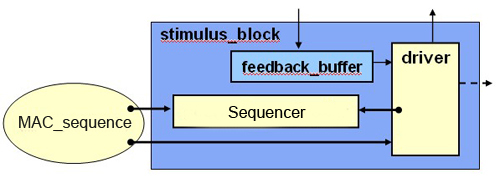

在上一节中,**《IC验证"UVM验证平台加入factory机制"(六)》**虽然输出了“main_phase is called”,但是“data is drived”并没有

2020-12-09 18:28:15

员开始使用Verilog(或者VHDL,这里以Verilog为例)将特性列表转换成RTL代码,而验证人员 则开始使用验证语言(这里以SystemVerilog为例)搭建验证平台,并且着手建造第一个测试

2020-12-01 14:39:13

第二章 验证flow验证的Roadmap验证的目标UVM验证方法学ASIC验证分解验证策略和任务的分解AMBA可重用、灵活性、兼容性、广泛支持一.验证的Roadmap1.ASIC芯片项目流程市场需求

2021-11-01 06:28:47

嗨,我想用Modelsim XE来模拟我的设计。您能否提供以下有关Modelsim XE模拟器的信息或我可以找到这些信息的任何链接:-1。它是否支持系统verilog进行验证?2。代码覆盖率支持.3

2018-11-27 14:20:41

的PQLab,旨在帮助foundry PDK工程师确保PDK的质量,并帮助设计工程师快速分析和验证foundry的PDK,并比较不同版本和不同厂家的PDK性能。 产品优势 最全面的PDK QA

2020-07-01 09:54:30

- 为什么选择 Python?如何使用 Python 进行验证(测试平台)? Cocotb -(CO-routine 和 CO-simulation 的Testbench)可能是事实上的 标准Python

2022-11-03 13:07:24

先进的设计与仿真验证方法成为SoC设计成功的关键。一个简单可行的SoC验证平台,可以加快SoC系统的开发与验证过程。FPGA器件的主要开发供应商都针对自己的产品推出了SoC系统的开发验证平台,如

2019-10-11 07:07:07

的性能有一个准确的把握。有了接口性能数据后,可以帮助在系统测试阶段定位问题。在系统测试阶段,性能瓶颈一方面来自于接口,一方面来自于WiFi。在接口验证阶段获得这个数据后可以帮助分析和定位问题。(3)在平台

2019-06-21 05:00:09

UVVM(通用 VHDL 验证方法)

简介

UVVM(通用 VHDL 验证方法)是一种免费的开源方法和库,用于开发非常结构化的基于 VHDL 的测试平台。

概述、可读性、可维护性、可扩展性和重用性

2024-01-02 12:59:24

项目名称:基于FPGA的数字电路实验验证平台应用领域:高校的数字电路实验课程中实验结果验证与分析参赛计划:一、设计思路:在高校的数字电路课程中,要通过在FPGA器件上通过设计一些简单的时序或者组合

2021-05-12 18:13:29

1、验证码与打码平台的攻防对抗 众所周知,验证码的出现是为了区分人和机器,但随着科技的发展,黑产从业者的可图之利增多,验证码的战场也进入了一段破解与抗破解的持久博弈。 验证码在逐渐复杂的同时,黑

2022-09-28 11:02:12

标有阴影的CPU0和CPU1不是被测系统的一部分,这些模块将在SystemVerilog测试平台中建模。CPU和其余模块之间的信号是DUT外界的接口。02 存储系统验证大多数验证项目中,验证存储器系统的方法

2022-11-04 11:10:21

本文介绍一种通用的UART自动验证平台,可用于自动测试UART接口的所有方面。

2021-04-30 06:46:31

设计的验证平台,以此来提高工作效率。论文介绍了FF-DX地址计算部件的时序建模和静态时序分析方法。在静态时序分析之后,将SDF文件中的延时信息反标到逻辑网表中,通过动态时序验证进一步保证设计的时序收敛

2011-12-07 17:40:14

嗨,大家好,我一直在使用Vivado设计套件一段时间了。只是想知道 :1.如果我可以通过链接Vivado使用Questasim 10.0b来验证设计?2.我可以使用系统verilog编写

2019-04-02 14:11:11

Systemverilog [1]和 UVM [2]为验证团队提供结构和规则。它使得在许多测试中能获得一致的结果,并可以在团队之间共享验证。许多验证团队都在使用由C代码编写的验证套件。本文将讨论将基于C的测试和验证套件集成到常规UVM测试平台的各种方法。

2020-12-11 07:59:44

Systemverilog [1]和 UVM [2]为验证团队提供结构和规则。它使得在许多测试中能获得一致的结果,并可以在团队之间共享验证。许多验证团队都在使用由C代码编写的验证套件。本文将讨论将基于C的测试和验证套件集成到常规UVM测试平台的各种方法。

2020-12-15 07:38:34

,对50Hz的正弦信号,采用100Hz和99Hz两个信号对采样前后的波形和频谱进行分析,验证系统的可靠性,在频域采样系统中,通过对傅立叶变换之后的信号进行102点和97点采样之后的结果,来验证采样点数与原信号点数关系。通过该虚拟系统,可以很好地理解并加深对时域和频域采样定理的认识。

2019-06-26 09:13:53

的、设计重用的、可综合性和可测试性等方面的规则检查; 代码覆盖率分析.研究仿真中的测试矢量是否足够;设计性能和面积分析.在设计逻辑综合过程中分析所设计的RTL所能达到的性能和面积要求;可测性分析:IP核

2021-09-01 19:32:45

,设计不断地重用,而验证也希望能够重用一样的验证模块,这就催生了层次化的验证方法。Synopsys的VMM验证方法学提供了基于SystemVerilog的验证方法,包括了有约束的随机数生成,层次化

2019-07-03 07:40:26

,设计不断地重用,而验证也希望能够重用一样的验证模块,这就催生了层次化的验证方法。Synopsys的 VMM验证方法学提供了基于SystemVerilog的验证方法,包括了有约束的随机数生成,层次化

2019-07-01 08:15:47

您还有第二个MCU或其他要通过Z-Wave OTA传输的数据文件。如何重用Bootloader固件来验证签名并解密数据?引导加载程序中已经存在用于验证和解密文件的代码,并且众所周知。重用现有的引导

2022-02-14 07:54:04

我是用modelsim仿真出来的,但是不知道结果是否正确。有没有哪位同志知道怎么验证FFT的仿真结果是否正确?也不知道怎么将modelsim与matlab联合仿真?求大神指点

2015-09-14 22:07:50

的软件模拟器作为验证的第一站。Mentor Graphics验证IP(VIP)是一个可复用组件库,无缝集成到使用UVM、OVM、Verilog、VHDL和SystemC构建的测试平台,也可与第三方软件

2017-04-05 14:17:46

在emulator环境下对于程序记过的验证

是否可以使用printf打印结果输出,或者写文件?

我使用了printf打印似乎对实时系统的性能有很大的影响?

2018-06-21 17:40:19

尽快完成控制算法的验证,所以如果有现成的验证方案更好。我自己搭建平台是可以的,但是预算有限,并且时间上也来不及了。我对平台的要求是比较简单的,能跑出来结果就行。具体要求如下:1 能测量三相的相电流;2 有位置编码器,能进行实现FOC控制;3 能得到电流、电压、位置、速度的曲线图。

2019-12-23 16:25:38

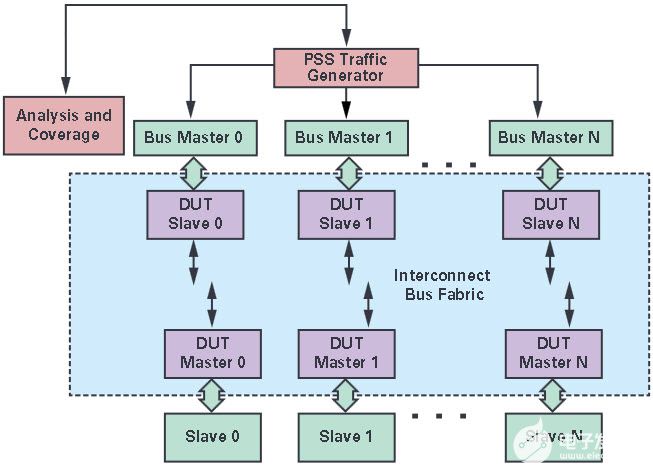

本文提出了一种基于FPGA的NoC验证平台。详细讨论了该验证平台中FPGA硬件平台和NoC软件的基本功能,并阐述了TG/R,MPU,MPI以及NoC软件的可重用性等特点。通过一个实例仿真验证的结果说明了该验证平台的基本功能和优越性。

2021-05-06 07:20:48

SoC系统验证平台总体框架是怎样的?SoC系统验证平台如何去构建?

2021-04-28 07:13:41

结果一起上报到验证码平台,验证码平台配置规则和策略来对这些信息进行分析和匹配,筛选出可能是黑灰产的请求进行二次验证或拦截,这样就可以起到识别黑灰产的效果。目前,顶象依赖设备指纹和实时风控引擎技术,可以

2022-11-01 15:21:22

有条理,我们要在验证计划当中明确要搭建什么样的验证平台,目前主流的验证平台有基于verilog的印证平台,基于systemverilog的验证平台,以及适用uvm方法学建立的验证平台,据uvm验证方法

2021-01-21 15:59:03

为构建平台的结构上花去过多的时间,可以把精力集中放在事物级建模以及结果的分析上。另外,由于不同项目的平台的结构和使用方法基本相同,这就为多个验证工程师之间的沟通交流提供了方便,uvm为验证工程师提供了

2021-01-21 16:00:16

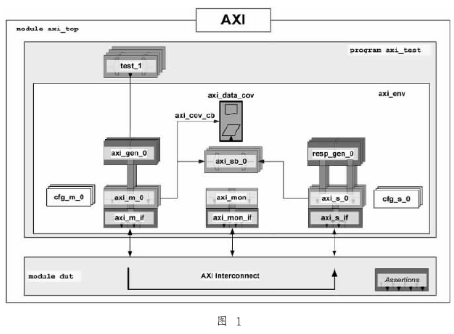

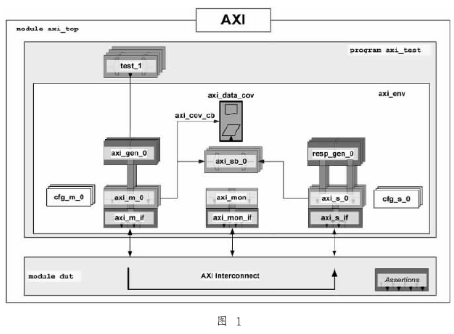

。 我们一个直观的印象,就是uvm验证平台,它是分层的结构。图中的每一个巨型框都代表着平台的一个构成元素。这些元素呢,我们称为平台组建,下面来简单的分析一下。 从最底层上来看,agent 中包含

2021-01-22 15:32:04

请教一下基于FPGA的通信系统基带验证平台该怎样去设计?

2021-04-28 06:59:45

晶片验证测试及失效分析

2012-07-18 17:24:41

智能家庭现有技术及验证要点分析

2021-05-08 06:02:33

验证平台中定义的参数和变量,既可调整仿真的行为,也可约束配置的范围,是对验证平台的必要的装点和修饰。若把验证平台比作一个姑娘,那么参数和变量就像是姑娘身上的发卡、耳环、项链和手表。 通常验证者会创建一

2023-04-04 17:20:51

验证方法(UVM For VHDL)开放式验证方法 (OVM)验证方法手册 (VMM)eVC 重用方法论 (ERM)参考验证方法 (RVM)高级验证方法 (AVM)通用重用方法论 (URM)系统验证

2022-11-26 20:43:20

。例如,VHDL 有许多语言结构,它们不打算用于硬件综合,但可用于测试平台以在仿真中刺激或分析其他代码。然而,像 VHDL 或 Verilog 这样的HDL 主要针对 RTL 设计和行为建模。它们

2022-02-16 13:36:53

以上各种应用涉及的工具、目标数据以及输出结果各不相同,我们仍然可以把仿真和验证过程大致分为激励信号准备、仿真、结果察看和分析三个主要步骤。从这个角度看,不同应用只是侧重点不同:数字电路的仿真验证更侧重

2012-04-27 14:33:36

本帖最后由 eehome 于 2013-1-5 10:01 编辑

EDA先锋工作室的精品书籍,国内少有的系统讲述FPGA设计和验证的好书,特别是验证部分很精华,现在和大家分享,同时附上本书的实例源代码和Verilog HDL语法国际标准。

2011-08-02 14:54:41

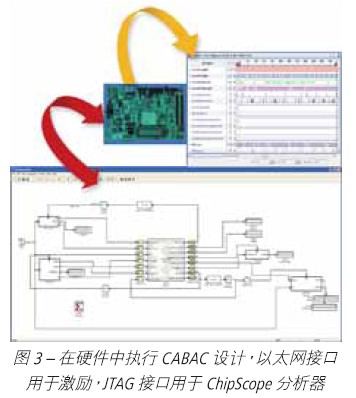

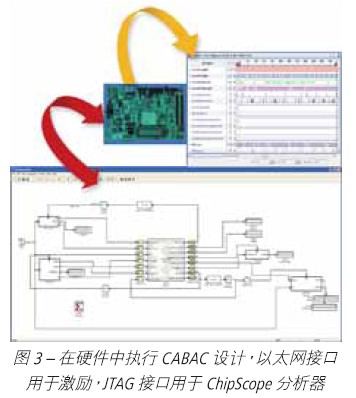

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法[2].本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。

2019-06-18 07:43:00

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法。本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。1、RFID芯片的FPGA

2019-05-29 08:03:31

本文首先介绍RVM验证方法学和覆盖率驱动技术,然后详细分析如何使用结合覆盖率驱动技术的RVM验证方法学对SOC(System On Chip)进行完备的功能验证, 最

2009-09-05 08:53:00 15

15 Verilog设计与验证://以下是编译指令,定义时间单位和时间精度`timescale 1ns / 100ps

//以下是module名称, 端口列表module HelloVlog

2010-02-09 09:31:36 48

48 Open Verification Methodology(OVM)是Mentor Graphics 和Cadence 共同推出的,业界第一个基于SystemVerilog、通用开放的验证方法学;其基于事务交易级的方法学,基于Factory Pattern 的对象生

2010-07-04 11:43:22 7

7 无线温度验证系统 温度压力一体 温度验证仪分有线系统与无线系统。有线的温度验证系统精度低,价格相对于无线产品的价格要低廉的多,无线验证系统操作方便,节省时间,而有线布线特别麻烦。所以在某些全封闭

2023-12-20 10:10:23

提出了基于事务断言验证技术,用属性说明语言(Property Specification Language,PSL)描述系统的属性,用事务进行系统的验证,通过编程语言接口机理和工具控制语言来控制验证中PSL断

2010-08-02 17:26:35 0

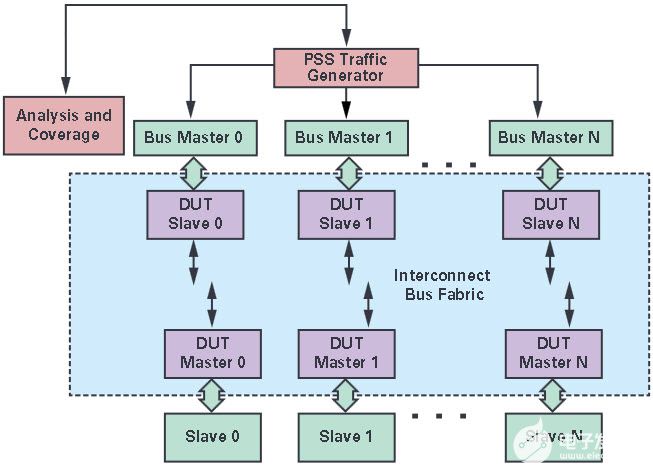

0 针对基于软件仿真片上网络NoC(Network on Chip)效率低的问题,提出基于FPGA的NoC验证平台构建方案。该平台集成可重用的流量产生器TG(Traffic Generation),流量接收器TR(Traffic Receiver)

2011-01-04 16:24:38 12

12 随着深亚微米工艺技术日益成熟,基于IP复用的IC设计方法广泛采用,集成电路芯片的规模越来越大,这对集成电路验证技术和方法学提出了很大的挑战。就如芯片

2009-04-04 10:58:40 1361

1361

HDL设计和验证与System Generator相结合

Xilinx®SystemGeneratoRForDSP是用来协助系统设计的MATLABSimulink模块集。SystemGeneratorforDSP在熟悉的MATLAB环境中引入XilinxFPGA对象,让您能够

2010-01-06 14:39:30 1181

1181

针对数字信号处理器的不同仿真和验证要求,提出了一种可测性软硬件协同仿真和验证平台的设计. 采用可配置IP 模块和总线结构,实现了硬件平台可配置性和可重用性;采用在线仿真模块

2011-06-09 17:54:21 39

39 本文简单讨论并总结了VHDL、Verilog,System verilog 这三中语言的各自特点和区别 As the number of enhancements

2012-01-17 11:32:02 0

0 IP核验证平台采用6层板PCB设计,使用独立的外部时钟同步芯片,可以为PCI及其它接口提供稳定的零延迟时钟系统电路,满足PCI总线的时钟要求,使验证平台高速,稳定,可靠的工作。

2012-01-17 14:02:19 1501

1501

芯片验证的工作量约占整个芯片研发的70%,已然成为缩短芯片上市时间的瓶颈。应用OVM方法学搭建SoC设计中的DMA IP验证平台,可有效提高验证效率。

2012-06-20 09:03:29 2627

2627 SoC基于IP设计的特点使验证项目中多语言VIP(Verification IP)协同验证的需求不断增加,给验证工作带来了很大的挑战。为了解决多语言VIP在SoC验证环境灵活重用的问题。提出了一种

2015-12-31 09:25:13 12

12 本章介绍了如何编写测试验证程序(test bench)。测试验证程序用于测试和验证设计的正确性。Verilog HDL提供强有力的结构来说明测试验证程序。verilog相关教程材料,有兴趣的同学可以下载学习

2016-04-25 16:09:32 17

17 设计与验证,很不错的一本书,《设计与验证》以实例讲解的方式对HDL语言的设计方法进行介绍。全书共分9章,第1章至第3章主要介绍了Verilog HDL语言的基本概念、设计流程、语法及建模方式等内容

2016-10-10 17:04:40 566

566 基于UVM的CPU卡芯片验证平台_钱一文

2017-01-07 19:00:39 4

4 基于UVM的验证平台设计研究_王国军

2017-01-07 19:00:39 4

4 UVM已经成为了一种高效率的、从模块级到系统级完整验证环境开发标准,其中一个关键的原则是UVM可以开发出可重用的验证组件。获得重用动力的一个方面表现为标准的仿真器和硬件加速之间的验证组件和环境的复用

2017-09-15 17:08:11 14

14 控制器设计出的新型元器件通用验证方法,硬件由通用验证平台和功能应用子板两部分组成。软件包含有上位机调试工具、命令解析模块、通信模块、数据智能处理模块等。解决了新型元器件验证周期长、成本高、难以实时控制和智能数据分析等缺点。用此方法已成功对芯片JS71238进行了性能功能的验证,取得了理想的验证效果。

2017-11-17 03:00:45 1027

1027

设计了一种基于FPGA的验证平台及有效的SoC验证方法,介绍了此FPGA验证软硬件平台及软硬件协同验证架构,讨论和分析了利用FPGA软硬件协同系统验证SoC系统的过程和方法。利用此软硬件协同验证

2017-11-17 03:06:01 13138

13138

原则和天线设计的理论模型。同时,给出了验证平台的测试结果,通过实际的测试证明了验证平台设计的正确性和可靠性。该验证平台有力地支撑了RFID芯片的功能验证,大大提高了标签芯片的投片成功率。

2017-11-18 08:42:22 1938

1938

,仿真时将端口激励文件转换成对应于验证电路端口的时序信号。通过对通用同步/异步串行接收/发送器、中断及定时器等功能模块的验证,证明了激励发生机制具有较强的可观察性、可控制性及可重用性。验证结果分析表明,在验证

2017-11-28 17:43:39 0

0 本文以软件工程的视角切入,分析中科院计算所某片上系统(SoC)项目的验证平台,同时也介绍当前较为流行的验证方法,即以专门的验汪语言结合商用的验证模型,快速建立测试平台(test-bench)并在今后的项目中重用(reuse)之。

2020-04-10 09:23:23 1151

1151

带宽会受限于SPI接口有效速率,本文采用芯片为W5500,支持10M/100M自适应,其理论值高达80Mbps,基本达到算法验证的要求。 ZYNQ可以通过灵活的EMIO模拟SPI接口,从而在最少改动官方demo的前提下移植C语言驱动程序。本文着重讲述EMIO的C语言软件驱动方式及可重用封装

2020-12-25 17:22:19 1888

1888 SystemVerilog语言简介 SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充

2021-09-28 17:12:33 2803

2803 第二章 验证flow验证的Roadmap验证的目标UVM验证方法学ASIC验证分解验证策略和任务的分解AMBA可重用、灵活性、兼容性、广泛支持一.验证的Roadmap1.ASIC芯片项目流程市场需求

2021-10-25 12:36:01 22

22 百度百科对UVM的释义如下:通用验证方法学(Universal Verification Methodology, UVM)是一个以SystemVerilog类库为主体的验证平台开发框架,验证工程师可以利用其可重用组件构建具有标准化层次结构和接口的功能验证环境。

2022-11-30 12:47:00 1061

1061 一个掌握Verilog语言的工程师初次看SystemVerilog都会有这样的感受,这就是Verilog啊,很容易啊,So easy啊。没错,确实是这样,System Verilog的产生

2022-12-09 15:08:05 2303

2303 同样,需要根据芯片验证的特定要求重写exec代码。验证平台中用于控制总线上不同主站的基本软件驱动程序(如DMA和内存控制器)通常可用于此类应用。生成的 C 代码还需要以评估平台可接受的格式进行集成

2022-12-21 11:23:05 1416

1416

我们将介绍如何使用verilog参数和generate语句来编写可重用的verilog 代码。

与大多数编程语言一样,我们应该尝试使尽可能多的代码可重用。这使我们能够减少未来项目的开发时间

2023-05-11 15:59:21 647

647 本文介绍了从一组可重用的验证组件中构建测试平台所需的步骤。UVM促进了重用,加速了测试平台构建的过程。

2023-06-13 09:11:11 270

270

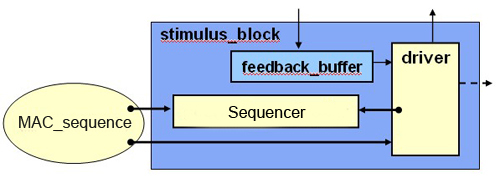

本文介绍了从一组可重用的验证组件中构建测试平台所需的步骤。UVM促进了重用,加速了测试平台构建的过程。 首先对 测试平台集成者(testbench integrator) 和 测试编写者(test

2023-06-13 09:14:23 326

326

相信很多人已经接触过验证。如我以前有篇文章所写验证分为IP验证,FPGA验证,SOC验证和CPU验证,这其中大部分是采用动态仿真(dynamic simulation)实现,即通过给定设计(design)端口测试激励,结合时间消耗判断设计的输出结果是否符合预期。

2023-07-21 09:53:24 4286

4286

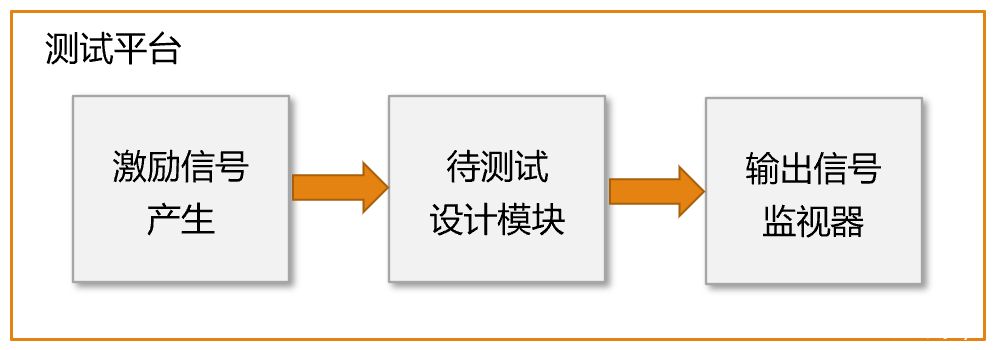

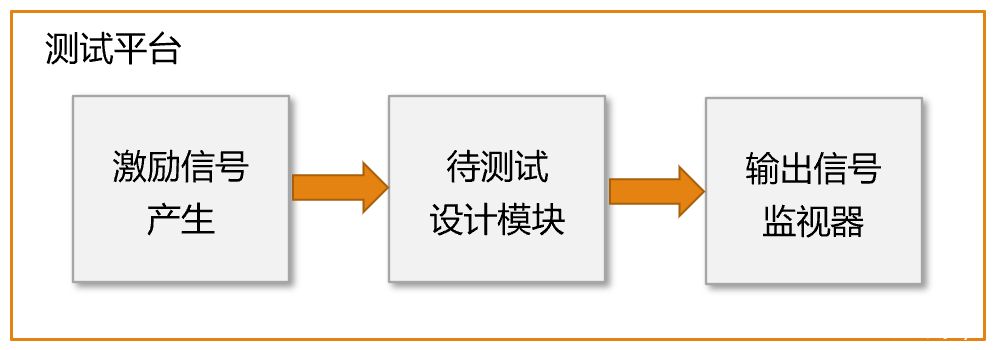

仿真验证主要作用是搭建一个测试平台,测试和验证程序设计的正确性,验证设计是否实现了我们所预期的功能。其结构如下图所示。

2023-10-02 16:29:00 660

660

电子发烧友App

电子发烧友App

评论