本文主要是Lattice公司市场总监Shakeel Peera给大家谈面对竞争激烈的FPGA市场,Lattice公司将持续优化FPGA成本和功耗。

2012-08-14 14:12:55 783

783

Altera推出业界唯一投产的低功耗28 nm Cyclone® V GT FPGA,帮助开发人员降低了PCIe Gen2应用的系统总成本,并全面通过了PCI Express® (PCIe®) 2.0规范的兼容性测试。

2013-03-19 12:37:39 2139

2139 FPGA芯片厂商赛灵思日前宣布已收购峰科计算解决方案公司(以下简称“峰科计算”),旨在通过自动硬件感知优化强化赛灵思Vitis统一软件平台,进一步降低软件开发者使用自行调适计算的门槛。

2020-12-03 11:46:03 2003

2003 实际情况进行资源的自动调度和优化,从而进一步提高工作效率和降低人力成本。总结,AI智能呼叫中心凭借自动化处理、个性化服务、数据驱动决策以及节约成本等一系列优势,为企业建立了更加高效、智能的服务系统,随着

2023-09-20 17:53:17

发展的芯片。云端运算已在深度学习训练的效能表现相当显著,然而若要运用到终端产品上,除了功耗与芯片体积的限制,加上云端运算有数据存取、实时性与安全性的考虑,预期将会催生AI芯片向终端的「 边缘运算」迈进

2017-12-05 08:09:38

I/O 可优化管脚分配,从而提高布通率和信号完整性。主要优势:■ 通过采用并行流程缩短总设计时间■ 通过消除 PCB 信号层降低 PCB制造成本■ 消除由于 PCB 上的过期 FPGA符号所导致

2018-09-20 11:11:16

FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能够做到如此低的功耗是因为什么?

2021-04-30 06:08:49

0.5 V,静态电流将从原来的12μA降低到8μA.4结束语本文在分析了FPGA中静态功耗的分布和基本单元的漏电流模型后,提出了使用双阈值电压的晶体管来降低整个芯片的静态功耗。由于是在非关键路径上使用高阈值电压栅的晶体管来降低静态功耗,所以对芯片的工作速度影响很小。

2020-04-28 08:00:00

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本

2015-02-09 14:58:01

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-11-05 07:54:43

被引入FPGA中,以满足客户产品快速上市的要求。此外,FPGA企业都在大力降低产品的功耗,满足业界越来越苛刻的低功耗需求。 与此同时,ASIC的开发成本并不如外界所想的高,加上晶圆技术不断进步,目前

2012-11-07 20:25:53

被引入FPGA中,以满足客户产品快速上市的要求。此外,FPGA企业都在大力降低产品的功耗,满足业界越来越苛刻的低功耗需求。 与此同时,ASIC的开发成本并不如外界所想的高,加上晶圆技术不断进步,目前

2012-11-20 20:09:57

当AI遇上FPGA,告别高门槛、高能耗、高成本

2019-10-21 08:00:04

技术完成对单个设计的测试,可以提高晶圆良率,大幅降低总成本,且无需额外的客户工程设计工作或再认证。 EasyPath-6 FPGA提供世界级的故障覆盖率,几乎达100%,并且客户在生产过程中可以在

2012-08-11 18:17:16

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-08-29 07:52:29

电压、输出电压、输出/负载电流和温度等参数都是非常重要的信息。系统设计人员还希望能够记录FPGA在各种应用情况下的功耗,利用这些信息动态的调节某些FPGA性能,或者调节系统中不需要的某些部分,以便降低

2018-10-23 16:33:09

管理和对FPGA 相关的各种内部电压及I/O 电压排序。电源管理已成为FPGA 设计者的一个重要考虑因素,是在设计便携式、电池供电的产品时。通过功率监控设计技术能够减少功耗、增强可靠性、降低成本,并

2012-08-11 16:17:08

目前许多终端市场对可编程逻辑器件设计的低功耗要求越来越苛刻。工程师们在设计如路由器、交换机、基站及存储服务器等通信产品时,需要密度更大、性能更好的FPGA,但满足功耗要求已成为非常紧迫的任务。而在

2019-07-15 08:16:56

4个I/O Bank。在多电压应用环境中比较有利,并且支持热插拔和施密特触发器。Actel在IGLOO系列产品的开发过程中,对静态功耗的主要物理来源——漏电流方面做了改进。同时在生产过程中对产率、速度

2019-07-05 07:19:19

设计技巧为什么能够节省功耗?降低FPGA功耗的设计技巧有哪些?

2021-04-30 06:04:19

降低FPGA功耗的设计技术 Design Techniques to Reduce Power Consumption Each generation of FPGAs gets

2009-12-18 16:49:59

:在工业生产过程中,NanoEdge AI 可以帮助实现对生产线的实时监控和故障预测,提高生产效率和降低维护成本。

3.智能交通:通过将 NanoEdge AI 应用于交通信号灯、无人驾驶汽车等设备

2024-03-12 08:09:00

低成本Spartan现场可编程门阵列(FPGA)系列在成本、性能和开发工具方面实现了完美的平衡,可帮助为消费、汽车、监控、无线以及其它成本敏感型市场设计更多创新的终端产品。 这一业界最新的低功耗

2019-07-26 06:47:56

。阿呆8年前在微软亚洲研究院参与用FPGA+Open Channel SSD加速Bing搜索引擎的研究,那个时候FPGA做机器学习性能已经可以甩CPU几条大街了,同时还能节省购买服务器的成本,降低散热

2018-08-21 09:50:44

无论从微观到宏观、从延长电池寿命到减少全球变暖的温室效应等等,各种不同因素都在迅速推动系统设计人员关注节能问题。一项有关设计优先考虑事项的最新调查指出,大部分工程师已把功耗排在首位,或者是将其紧跟在性能、密度和成本之后。在功耗方面,FPGA带来了独特的挑战。为什么要设计优化FPGA功耗?

2019-08-08 07:39:45

客户关注的问题。降低FPGA功耗是降低封装和散热成本、提高器件可靠性以及打开移动电子设备等新兴市场之门的关键。

2019-09-20 06:33:32

Altera公司产品和企业市场副总裁DannyBiran低功耗是一种战略优势 在器件的新应用上,FPGA功耗和成本结构的改进起到了非常重要的作用。Altera针对低功耗,同时对体系结构和生产工艺进行

2019-07-16 08:28:35

是在映射或布局和布线后设计的基础上对器件功耗进行估计的。 对于成熟的投产的 FPGA 和 CPLD,XPower 计算出的功耗估计的平均设计批量误差 (suite error) 小于 10%。它将

2012-01-11 11:59:44

市场上已有的解决方案,以降低开发成本。在当今对成本和功耗都非常敏感的“绿色”环境下,对于高技术企业,两种挑战都有什么影响呢?第一种挑战意味着开发全新的产品,其功能是独一无二的,具有较低的价格以及较低

2019-08-09 07:41:27

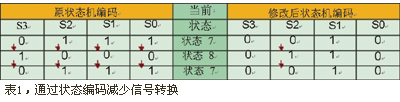

复用器重构降低FPGA成本

2012-08-17 10:43:02

过去一段时间以来,收益递减法则(Law of Diminishing Return)在传统处理器架构的进展方面已经明显体现出来。每一代新工艺几何尺寸和新兴微架构的进步,在相应性能上所能带来的增益正在

2019-08-02 06:32:24

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-08-15 08:28:42

低功耗mcu的选择方法如何降低mcu的功耗

2021-02-24 06:11:07

降低工业应用的总体拥有成本大约三分之一的嵌入式设计人员考虑在嵌入式应用中采用FPGA,只是认为在设计中使用FPGA 过于昂贵。但是,从系统级了解总体拥有成本(TCO) ( 由产品生命周期中的开发

2013-11-13 11:17:35

充分发挥低功耗优势的公司之一,它是世界上最大的电信系统供应商之一,可提供基于Altera Stratix IV FPGA的运营商级以太网芯片解决方案。Altera高性能、低功耗技术与TPACK高度集成

2019-07-31 07:13:26

全球可编程逻辑解决方案领导厂商赛灵思公司 (Xilinx Inc.) 宣布,为推进可编程势在必行之必然趋势,正对系统工程师在全球发布赛灵思新一代可编程FPGA平台。和前代产品相比,全新的平台功耗降低

2019-08-09 07:27:00

有什么方法可以提高片上系统级集成吗?有什么方法可以降低物料成本吗?

2021-05-14 06:20:23

对于各种不同的数据中心工作负载,FPGA 可以显著提高性能,最大程度减少附加功耗并降低总体拥有成本 (TCO)。

2019-10-10 07:46:05

易失性FPGA的电源特性是什么?如何在进行板级设计时,降低系统的静态与动态功耗?

2021-04-08 06:47:53

如何才能实现降低FPGA设计的功耗?

2021-04-29 06:47:38

如何设计才能充分发挥 FPGA 的作用?请问DSP设计流程通常包括哪几个步骤?

2021-04-08 06:10:27

在针对大批量应用开发系统时,要考虑的一个重要因素是成本。有多个方面会影响总体拥有成本,而不仅仅是每个元器件的价格。这包括硅片的功耗要求、材料(BOM)总成本、设计和测试系统的工程师的效能等。选择FPGA供应商很重要,要考虑影响系统成本的方方面面,这体现在整个产品设计周期中。

2019-10-14 06:11:14

Actel公司的ILGOO系列器件是低功耗FPGA产品,是在便携式产品设计中替代ASIC和CPLD的最佳方案。它在Flash*Freeze模式时的静态功耗最低可达到2µW,电池寿命是采用主流PLD

2020-05-13 08:00:00

。 除了在AI的线上推理方向,FPGA在其他很多方面也能发挥价值。在面向计算密集型任务,比如矩阵运算、图像处理、机器学习、压缩、非对称加密、搜索的排序等的时候,拥有流水线并行和数据并行的FPGA效率会

2021-09-17 17:08:32

品相比,功耗可降低75%。在CrossLink-NX FPGA上运行解决方案时,sensAI可提供多达2.5Mb的分布式内存、RAM块以及额外的DSP资源,MIPI I/O提供瞬时启动的性能可在不到

2020-10-23 11:43:04

可以做哪些措施来降低功耗

2023-10-23 07:51:09

请问有什么方法可以降低Linux的成本吗?

2021-04-25 06:15:12

理解技术,我们会联合这些合作伙伴,一起把效果最好用的、以及真正能够解决用户需求的一些技术开放出来,让大家在讯飞开放平台上一站式地开发,降低大家开发的门槛和成本。”并现场列举了一些基于讯飞开放平台AI能力开发

2018-06-15 20:36:18

,提升规模经济的关键原因。 板上芯片 (COB) 光源模块是有助于降低成本的最新封装方法之一。在这种模块中,LED 芯片采用半导体芯片形式,既无外壳,也不用连接,只需直接安装到 PCB 上或者更通俗地讲,安装到基材上。 而且,这种封装形式还带来了许多相关优势,如设计更灵活、配光更好、制造工艺更简单等。

2019-07-17 06:06:17

的:1)降低θJA:热阻抗取决于芯片与环境的热传导效率,可通过加散热片或者风扇减小热阻抗图12)减小PD:通过优化FPGA设计,降低总功耗,这也是本文重点讲解的部分。2.功耗估计在讲解低功耗设计之前,介绍

2014-08-21 15:31:23

供应商提出,最后,整个行业链中出现了铺天盖地的降价声。在企业整个价值链中,各个环节之间都存在着依存性,下一环节的成本管理必须建立在上一环节成本管理的基础之上,上一环节的成本最小化并不意味着下一环节的成本

2018-10-11 10:20:16

和存储器的空间都是用钱买来的,如果写代码时多花几天时间提高一下程序效率,那么从降低CPU主频和减少存储器容量所节约的成本绝对是划算的。CPLD/FPGA设计也类似。二:低功耗设计现象一:我们这系统

2019-03-07 07:57:19

应用降低了成本,功耗和延迟。在数据中心之外执行处理可以限制隐私和带宽问题,同时通过提供较低的延迟来确保响应速度的提高。 所有这些综合因素促使在未来十年内,至少有640亿个新设备需要在终端和边缘使用嵌入式

2020-07-27 17:57:36

什么是TICKLESS?怎么能实现功耗的降低呢?TICKLESS是如何去实现功耗降低的呢?

2022-02-24 08:02:02

如何利用FPGA设计技术降低功耗?

2021-04-13 06:16:21

本帖最后由 曾12345 于 2018-5-23 15:49 编辑

全新的毫瓦级功耗FPGA解决方案为机器学习推理在大众市场物联网应用中实现快速部署创造机遇。1. 将AI加速部署到快速增长

2018-05-23 15:31:04

应用实例——汽车的视频分析结论Cyclone V FPGA降低了总体拥有成本。TSMC的28LP工艺设计用于尽可能降低功耗,同时也是成本最低的28nm制造工艺。低功耗意味着提高了用户价值链的系统可靠性

2015-02-09 15:02:06

本资料是关于如何采用低功耗28nm降低系统总成本

2012-07-31 21:25:06

工业电子产品的发展趋势是更小的电路板尺寸、更时尚的外形和更具成本效益。由于这些趋势,电子系统设计人员必须降低印刷电路板(PCB)的尺寸和成本。使用现场可编程门阵列(FPGA)和片上系统(SoC

2019-03-08 06:45:06

近年来,由于对电子设备的需求不断增长,低功耗芯片的设计发挥了重要作用,这些电子设备越来越小化,并且功耗越来越低,以支持电池电源。人工智能(AI)的使用 —— 越来越多地出现在可穿戴设备、物联网设备

2022-03-24 10:45:43

新一代 FPGA的速度变得越来越快,密度变得越来越高,逻辑资源也越来越多。那么如何才能确保功耗不随这些一起增加呢?很多设计抉择可以影响系统的功耗,这些抉择包括从显见的

2009-06-20 10:37:12 2321

2321

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标

2010-07-01 11:08:43 465

465 自从Xilinx推出FPGA二十多年来,研发工作大大提高了FPGA的速度和面积效率,缩小了FPGA与ASIC之间的差距,使FPGA成为实现数字电路的优选平台。今天,功耗日益成为FPGA供应商及其客户关注的问题。降低FPGA功耗是缩减封装和散热成本、提高器件可靠性以及打开移

2011-03-15 14:58:34 31

31 FPGA设计方面最大的难题与挑战是什么?许多客户回答都是功耗的控制。随着FPGA密度和性能的提升,不可避免地带来了功耗的倍增。FPGA领域的发展着重围绕三个关键点:低功耗、低成本

2012-05-04 11:05:26 1064

1064 LatticeECP4 系列:具有高级通信引擎和强大的 DSP 模块的低成本、低功耗 FPGA 新的LatticeECP4系列是第四代具有高级通信引擎和功能强大的DSP模块的高可靠、低成本、低功耗FPGA。创新的Latt

2012-06-06 09:51:38 1924

1924 本文主要介绍Cyclone V FPGA的一个很明显的特性,也可以说是一个很大的优势,即:采用低功耗28nm FPGA减少总系统成本

2012-09-05 15:35:27 26

26 白皮书 :采用低成本FPGA实现高效的低功耗PCIe接口 了解一个基于DDR3存储器控制器的真实PCI Express (PCIe) Gen1x4参考设计演示高效的Cyclone V FPGA怎样降低系统总成本,同时实现性能和功耗

2013-02-26 10:04:25 72

72 问题加以考虑,一般来说应该从选择 FPGA 开始。减少FPGA的功耗可以降低供电电压,简化电源设计和散热管理,降低对电源分配面的要求,从而简化电路板设计。

2017-11-22 15:03:01 2573

2573 基于将AI 计算性能植入到边缘端的应用,市场上一方面仍然着重于研究AI计算性能的提升,另一方面,关于降低 AI应用门槛的呼声也越来越高。而正是在这样的呼声之下,我们看到一些企业开始推广即插即用的AI相关应用,拟从部署便捷程度、应用成本等角度来降低AI 的应用门槛!

2017-11-25 09:21:28 3126

3126 硅谷的初创公司Subtle Medical正在利用AI大幅降低磁共振成像的时间和资金成本,同时降低辐射暴露的风险。

2018-08-09 14:35:19 4578

4578 设计周期和更低开发成本压力的情况下设计出“更绿色”的产品。新的Virtex-6 FPGA系列比前一代产品功耗降低多达50%,成本降低多达20%。该系列产品进行了最合适的组合优化,包括灵活性、硬内核IP

2018-11-15 10:09:02 787

787 reconfigure.io的Rob Taylor在法兰克福的XDF 2018云轨道中展示了一个用例。

Rob讨论了FPGA在FPGA中的可访问性,降低了评估和利用FPGA的成本。

2018-11-22 06:08:00 3402

3402 的关注点,一场卡位大战已经打响,目前我们看到首先爆发的是手机的AI芯片,相信接下来还会扩散到更广泛的终端设备市场。其中FPGA因为其产品特性,一直被认为在云端和网络端的AI技术方面更有发挥空间,而近日,作为低功耗、小尺寸、低成本FPGA的代言人,莱迪思公司宣布进入网络边缘计算市场的AI领域。

2018-11-23 17:25:41 767

767 AI 很火,但是 AI 的门槛也很高,普通的开发者想要搭上这波 AI 红利依然困难。

2019-01-10 09:06:09 3125

3125 12月11日,腾讯云发布大数据与AI领域的最新研究成果,包括AI换脸甄别技术AntiFakes、腾讯星图以及企业画像平台等七大新品,并对AI、大数据产品进行全线升级,致力于降低企业AI技术应用门槛。

2019-12-12 09:58:58 659

659 FPGA从成本、性能、开发门槛方面都在改变满足边缘AI的需求,那到底什么样的FPGA可以更好满足边缘AI需求?

2019-12-16 15:24:18 595

595 在针对大批量应用开发系统时,要考虑的一个重要因素是成本。有多个方面会影响总体拥有成本,而不仅仅是每个元器件的价格。这包括硅片的功耗要求、材料(BOM)总成本、设计和测试系统的工程师的效能等。选择FPGA供应商很重要,要考虑影响系统成本的方方面面,这体现在整个产品设计周期中。

2020-07-17 18:08:34 1718

1718 、海内外院士、商业领袖、科创精英莅临现场,探讨新兴科技发展现状及其为人类社会带来的巨大影响。第四范式创始人、首席执行官戴文渊发表了主题演讲,以下为经过整理后的演讲实录: 大家上午好,非常高兴有机会能在这边跟大家交流我们在 AI 驱动产业升级方面的一些思考。实际上

2020-11-27 09:30:18 1633

1633 并不是所有元件都具有相同的静止功耗。根据普遍规则,器件工艺技术尺寸越小,泄漏功耗越大。但并不是所有工艺技术都一样。例如,对于 90 nm 技术来说,Virtex-4 器件与其他 90 nm FPGA 技术之间在静止功耗方面存在显著差异,

2021-01-08 17:46:48 5063

5063

正在加载...

电子发烧友App

电子发烧友App

评论