All Programmable技术和器件的全球领先企业赛灵思公司(Xilinx, Inc.,(NASDAQ:XLNX))昨日宣布推出符合汽车级要求的Zynq® UltraScale+™ MPSoC系列器件,其可支持安全攸关的ADAS和自动驾驶系统的开发。

2018-01-17 09:15:26 9204

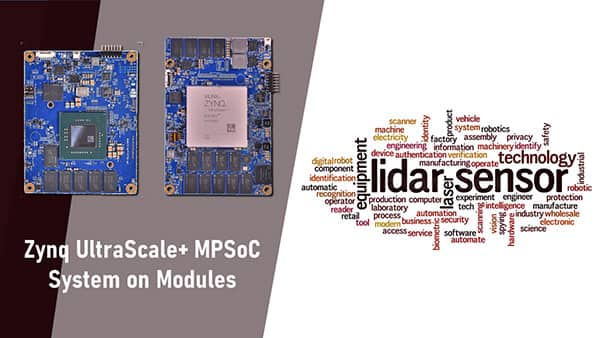

9204 LiDAR 技术的 Zynq UltraScale+ MPSoC 适应性 Zynq UltraScale+ MPSoC 器件实现了基于 SoC 的自适应产品设计,这给 LiDAR 应用实现带来了非常大的前景。将处理器和 FPGA 架构同时整合到一个设备中,可以针对任何特定领域快速部署

2022-11-05 16:52:45 9597

9597

专注于引入新品并提供海量库存的电子元器件分销商贸泽电子 (Mouser Electronics)即日起备货Xilinx的Zynq® UltraScale+ 多处理器片上系统 (MPSoC)。

2019-11-25 15:28:48 1102

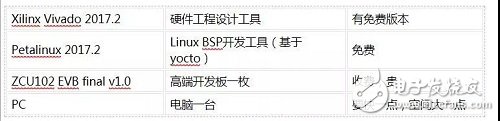

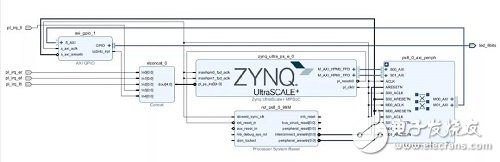

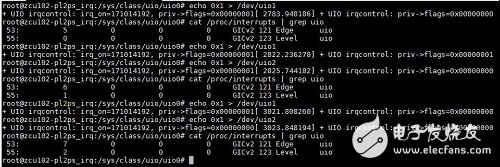

1102 ZYNQ Ultrascale+ MPSOC FPGA教程

2021-02-02 07:53:25

Linux主机测试CDC功能履行实施细节设计类型仅PSSW类型Zynq®UltraScale+™MPSoC Linux操作系统CPU的ARM Cortex A53 Core 0以1.1 GHz运行PS

2019-01-03 09:59:50

赛灵思和 DornerWorks 的系统软件团队在赛灵思的 Zynq® Ultrascale+™ MPSoC 上启动 Xen Project 管理程序时,我们发现可通过运行当年叱诧一时的流行电子游戏

2019-10-09 06:21:21

UltraScale+ MPSoC EV 部件上与 Zynq UltraScale+ MPSoC VCU(H.264/H.265 视频编解码器)连用。 因此,调试将不同于 MIG 等传统

2021-01-07 16:02:09

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

2021-01-22 06:29:21

+ MPSoC的seL4之上运行Linux。自己尝试Zynq UltraScale + MPSoC端口的主要目标是扩展seL4生态系统并为开发人员提供更多选择。因此,如果人们真的有能力尝试我们的工作,它会

2020-08-20 19:23:19

本身是否存在问题(换句话说,我无法实现这一点)?要么2)ZCU102电路板设计有问题吗?要么3)Zynq Ultrascale + MPSOC APU上运行的Linux设备驱动程序是否存在问题?对于

2019-10-14 09:17:03

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 在高性能系统中越来越多地使用高速串行互联意味着你会在Zynq UltraScale+ MPSoC系列中的11款器件中发现很多Gbps

2017-02-08 05:50:41 552

552 闲话Zynq UltraScale+ MPSoC 作者: Hello,Panda 时隔三年,Xilinx推出了其全新的异构SoC,大名叫Zynq UltraScale+。相比它的前辈

2017-02-08 08:24:11 588

588

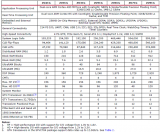

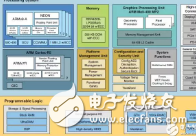

作者:Hello,Panda Zynq UltraScale+ MPSoC架构 Xilinx新一代Zynq针对控制、图像和网络应用推出了差异化的产品系,这在Xilinx早期的宣传和现在已经发布的文档

2017-02-08 08:25:49 451

451

作者:Hello,Panda Part3 I/O资源 和Zynq-7000相比较,Zynq UltraScale+ 增强了PS端的IO性能;PL端每个产品系都有HR和HP两种类型的IO。 1.PS

2017-02-08 08:29:11 491

491

作者:Hello,Panda Part 2 : Zynq UltraScale+ MPSoC启动 熊猫君在这里讨论启动(Boot),主要是想聊它的启动设备和启动方式。看看启动设备是否广泛支持,启动

2017-02-08 08:31:11 358

358

作者:Hello,Panda Part 2 : Zynq UltraScale+ MPSoC启动 熊猫君在这里讨论启动(Boot),主要是想聊它的启动设备和启动方式。看看启动设备是否广泛支持,启动

2017-02-08 08:31:11 339

339

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 上周,Xilinx发布了 Zynq UltraScale+ MPSoC,此款产品拥有一个ARM Cortex-A53四核CPU

2017-02-09 07:26:36 408

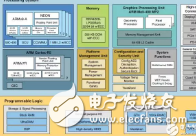

408 MPSoC器件族中的11个功能单元以“为任务量身打造模块”的概念引入所需的处理能力。以下块状图展示了 Xilinx Zynq UltraScale+ MPSoC系列中所有可用的元件。 这里可清楚看到

2017-02-09 08:01:11 1934

1934

本篇文章将与大家讨论的是Xilinx Zynq UltraScale+ MPSoC的电源解决方案参考设计。

2017-03-14 02:24:12 3418

3418

将计算能力、可靠性和可扩展性带入极度苛刻的应用 Enea近日宣布OSE5 MCE多核操作系统支持Xilinx® Zynq® UltraScale+™多处理器片上系统(MPSoC)芯片。OSE5新内核支持最新的A53处理器,并支持UltraScale+ ZCU102板卡,提供流畅的软件应用开发。

2018-06-30 01:04:00 2541

2541

熟悉运行在赛灵思 Zynq UltraScale+ MPSoC 上的 Xen 管理程序。 赛灵思和 DornerWorks 的系统软件团队在赛灵思的 Zynq® Ultrascale+™ MPSoC

2017-11-16 20:17:53 3147

3147

通过这篇有趣的教程,熟悉运行在赛灵思 Zynq UltraScale+ MPSoC 上的 Xen 管理程序。 赛灵思和 DornerWorks 的系统软件团队在赛灵思的 Zynq

2017-11-18 18:39:25 2298

2298

通过这篇有趣的教程,熟悉运行在赛灵思 Zynq UltraScale+ MPSoC 上的 Xen 管理程序。 赛灵思和 DornerWorks 的系统软件团队在赛灵思的 Zynq

2018-02-01 01:38:53 1100

1100 本文试图搞清楚在 Xilinx 基于 ARM 的 Zynq-7000、Zynq UltraScale+ MPSoC 和 Zynq UltraScale+ RFSoC 器件中是否存在任何漏洞。

2018-06-28 15:53:00 2492

2492 在本演示视频中,Xilinx讨论了其Zynq®UltraScale+™RFSoC系列的产品详细信息。

2018-11-21 06:07:00 5736

5736 该视频重点介绍了UltraScale +产品系列的第一个成员Zynq®UltraScale+™MPSoC,并展示了使用可编程逻辑中的DDR4 SDRAM IP的存储器接口系统的稳健性。

2018-11-29 06:36:00 3044

3044 该演示展示了Zynq UltraScale + MPSoC的视频处理功能。

使用ZCU102开发套件,Zynq UltraScale + MPSoC将全高清1080p视频输入转换为UltraHD 4K视频输出

2018-11-29 06:28:00 2904

2904 Lauterbach演示了Zynq UltraScale + MPSoC上的ARM Cortex-A53和Cortex-R5内核在2015年嵌入式世界中首次使用其TRACE32产品进行同步调试和跟踪。

2018-11-27 06:48:00 3562

3562 Zynq®UltraScale+™MPSoC,现已开始发售。视频向您重点介绍了Xilinx UltraScale +产品组合的第一位成员

2018-11-27 06:47:00 3262

3262 该视频重点介绍了UltraScale +产品组合的第一个成员,Zynq®UltraScale+™MPSoC,以及其多样化收发器技术的稳健性。

2018-11-27 06:33:00 2501

2501 使用Zynq UltraScale + MPSoC的ZCU102开发套件,该视频展示了使用SDSoC开发环境的开发流程。

2018-11-27 06:29:00 4495

4495 Xilinx展示了在QEMU软件仿真器上运行的Zynq UltraScale + MPSoC。

四核ARM Cortex-A53在SMP模式下运行4个Linux应用程序,在双核ARM Cortex-R5上运行裸机应用程序。

2018-11-26 06:46:00 5917

5917 Xilinx展示Zynq UltraScale + MPSoC在由6个FPGA组成的硬件仿真板上运行,以实现四核ARM Cortex-A53,双核ARM Cortex-R5,核心交换机互连,图形控制器,内存控制器......

2018-11-26 06:44:00 3160

3160 在本演示中,Intelliprop演示了在Xilinx Zynq UltraScale + MPSoC中实现的NVMe主机加速器。

2018-11-26 06:18:00 5658

5658 行业抓取式演示视频重点介绍了Zynq UltraScale + MPSoC装有专用处理引擎,面向图像处理,实时处理和功能安全性。

2018-11-23 06:59:00 2723

2723 该视频显示了Zynq®UltraScale+™MPSoC处理系统中硬化控制器的性能如何,LPDDR4以2.4Gbps运行48小时以上,在压力下,具有低抖动和大量余量。

2018-11-22 06:14:00 3772

3772 (PS)和可编逻辑(PL)架构,主要用在航空航天与国防,汽车电子,数据中心,无线通信基础设备和无线基础设施.本文介绍了Xilinx公司的Zynq® UltraScale+™MPSoC系列主要特性,应用方案以及AvnetUltra96开发板主要特性,框图,电路图,材料清单和PCB设计图.

2019-03-05 15:18:14 2854

2854

为了满足关键的系统级需求,设计者必须将功率/热量与整体性能抵消。Zynq UltraScale+?MPSOC有助于实现这种平衡。

2019-02-19 11:53:22 17

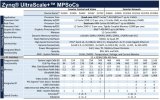

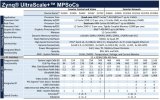

17 Zynq UltraScale+™ MPSOC系列基于Xilinx UltraScale™MPSOC体系结构。该系列产品在单个设备中集成了功能丰富的64位四核或双核ARM®Cortex™-A53

2019-02-21 16:48:54 19

19 XA Zynq UltraScale+ MPSoC 系列已通过 Exida 认证,符合 ISO 26262 ASIL-C 级的安全规范。Exida 是全球领先的自动化和汽车系统安全性和保密性专业认证公司之一。

2019-07-29 11:11:49 2364

2364 在美国计算机学会杂志《美国计算机协会通讯全集》的一篇专栏中,Steve Furber 指出,32 位 ARMv7 SoC(例如 Zynq UltraScale+ MPSoC)是最丰富和最受欢迎的 SoC 产品。

2019-07-30 16:21:33 2579

2579 Zynq UltraScale+ MPSoC 面向广泛的应用领域而打造 , 非常适用于 5G 无线基础设施、面向数据中心和有线通信的软件定义网络、新一代汽车驾驶员辅助系统和无人驾驶系统 (ADAS)、工业物联网系统 (IIoT)、超高清和超高画质摄像机、航空电子以及便携式软件定义无线电等各种应用。

2019-07-30 15:30:48 2435

2435

Virtex UltraScale+ 器件加上 Zynq UltraScale+ MPSoC 和 Kintex UltraScale+ FPGA展示了赛灵思16nm产品组合三大系列已经悉数登场。

2019-07-30 17:14:49 2239

2239 Zynq UltraScale+ MPSoC是Xilinx推出的第二代多处理SoC系统,在第一代Zynq-7000的基础上做了全面升级,在单芯片上融合了功能强大的处理器系统(PS)和用户可编程逻辑(PL)。Zynq UltraScale+ MPSoC系统框图

2019-11-18 11:03:22 2540

2540

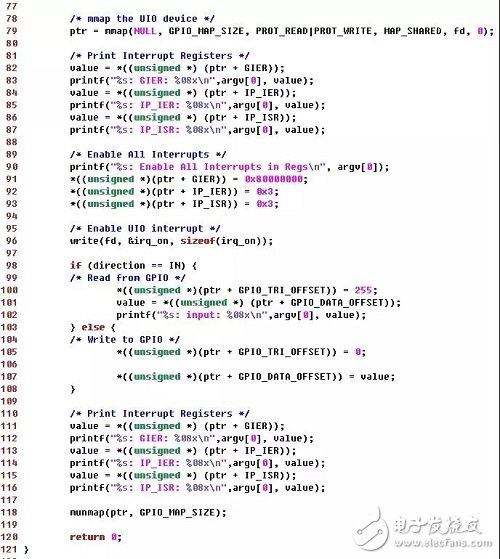

使用的是 Zynq UltraScale+ MPSoC ZCU104 评估板。但是,无论您使用任何器件,下列步骤都应适用。 先使用 Vivado 来创建了块设计。建立了 Zynq UltraScale PS,并把

2020-11-20 14:05:34 3840

3840 Zynq UltraScale+ MPSoC VCU DDR 控制器是一款专用 DDR 控制器,只支持在 Zynq UltraScale+ MPSoC EV 部件上与 Zynq

2021-02-23 06:00:10 15

15 米尔电子推出的国内首款zynq ultrascale+ mpsoc平台核心板(及开发板):MYC-CZU3EG吸引了人工智能、工业控制、嵌入式视觉、ADAS、算法加速、云计算、有线/无线通信

2022-01-07 15:20:29 3

3 ZU19EG 是一款紧凑型 SoC 原型开发板,采用 Zynq® UltraScale+™ MPSoC 器件,可提供 64 位处理器可扩展性,同时将实时控制与软和硬引擎相结合,用于 SoC 原型

2022-09-26 11:28:39 4

4 基于 Xilinx 公司ZYNQ Ultrascale+ MPSoC系列 FPGA 芯片设计,应用于工厂自动化、机器视觉、工业质检等工业领域

2022-11-02 14:35:47 1127

1127 Zynq UltraScale+ Use Case 4.4 原理图s

2023-02-03 18:47:07 2

2 Zynq UltraScale+ Use Case 4.1 原理图s

2023-03-22 19:15:48 0

0 Zynq UltraScale+ Use Case 4.2 原理图s

2023-03-22 19:16:00 0

0 Zynq UltraScale+ Use Case 4.3 原理图s

2023-03-22 19:16:12 0

0 Zynq UltraScale+ Use Case 1.1 原理图s

2023-03-22 19:16:27 0

0 Zynq UltraScale+ Use Case 1.2 原理图s

2023-03-22 19:16:44 0

0 Zynq UltraScale+ Use Case 1.3 原理图s

2023-03-22 19:17:02 0

0 Zynq UltraScale+ Use Case 1.4 原理图s

2023-03-22 19:17:16 0

0 Zynq UltraScale+ Use Case 2.1 原理图s

2023-03-22 19:17:36 0

0 Zynq UltraScale+ Use Case 2.2 原理图s

2023-03-22 19:17:56 0

0 Zynq UltraScale+ Use Case 2.3 原理图s

2023-03-22 19:18:07 0

0 Zynq UltraScale+ Use Case 2.4 原理图s

2023-03-22 19:18:25 0

0 Zynq UltraScale+ Use Case 3.1 原理图s

2023-03-22 19:18:36 0

0 Zynq UltraScale+ Use Case 3.2 原理图s

2023-03-22 19:18:54 0

0 Zynq UltraScale+ Use Case 3.3 原理图s

2023-03-22 19:19:07 0

0 Zynq UltraScale+ Use Case 3.4 原理图s

2023-03-22 19:19:20 1

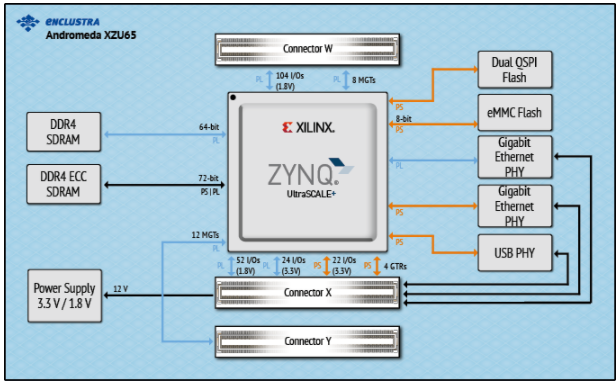

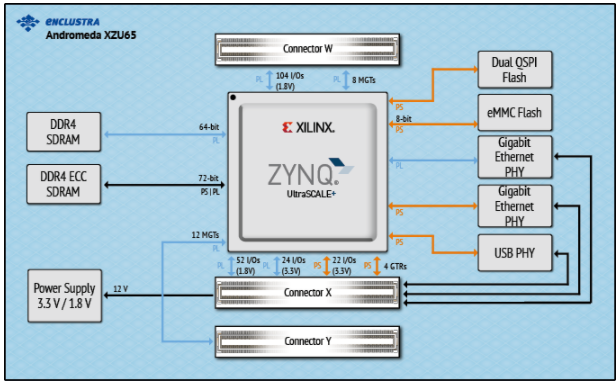

1 基于AMD-Xilinx Zynq UltraScale+ MPSoC器件,Andromeda支持三种外形尺寸:S(40 x 56 mm),M(52 x 66 mm)和L(80 x 64 mm)。它们提供 2 到 6 个高速连接器,支持多达 780 个 I/O。

2023-04-25 09:14:44 707

707

Zynq UltraScale+ Use Case 4.4 原理图s

2023-07-04 19:20:02 0

0 Zynq UltraScale+ Use Case 4.1 原理图s

2023-07-10 18:35:08 0

0 Zynq UltraScale+ Use Case 4.2 原理图s

2023-07-10 18:35:21 0

0 Zynq UltraScale+ Use Case 4.3 原理图s

2023-07-10 18:35:38 0

0 Zynq UltraScale+ Use Case 1.1 原理图s

2023-07-10 18:35:49 0

0 Zynq UltraScale+ Use Case 1.2 原理图s

2023-07-10 18:35:59 0

0 Zynq UltraScale+ Use Case 1.3 原理图s

2023-07-10 18:36:16 0

0 Zynq UltraScale+ Use Case 1.4 原理图s

2023-07-10 18:36:35 0

0 Zynq UltraScale+ Use Case 2.1 原理图s

2023-07-10 18:36:50 0

0 Zynq UltraScale+ Use Case 2.2 原理图s

2023-07-10 18:37:10 0

0 Zynq UltraScale+ Use Case 2.3 原理图s

2023-07-10 18:37:26 0

0 Zynq UltraScale+ Use Case 2.4 原理图s

2023-07-10 18:37:46 0

0 Zynq UltraScale+ Use Case 3.1 原理图s

2023-07-10 18:38:02 0

0 Zynq UltraScale+ Use Case 3.2 原理图s

2023-07-10 18:38:16 1

1 Zynq UltraScale+ Use Case 3.3 原理图s

2023-07-10 18:38:32 0

0 Zynq UltraScale+ Use Case 3.4 原理图s

2023-07-10 18:38:50 0

0 电子发烧友网站提供《Zynq UltraScale+ MPSoC上的单芯片FIPS 140-3.pdf》资料免费下载

2023-09-14 10:26:09 3

3 电子发烧友网站提供《Zynq UltraScale+ MPSoC:FIPS 140-3入门白皮书.pdf》资料免费下载

2023-09-14 14:24:43 1

1 电子发烧友网站提供《Zynq UltraScale+ MPSoC:软件开发者指南.pdf》资料免费下载

2023-09-14 10:03:42 9

9 电子发烧友网站提供《Zynq UltraScale+ MPSoC中的隔离方法.pdf》资料免费下载

2023-09-13 17:11:48 1

1 电子发烧友网站提供《Zynq UltraScale+ MPSoC的隔离设计示例.pdf》资料免费下载

2023-09-13 11:28:01 2

2 电子发烧友网站提供《适用于Xilinx Zynq UltraScale+ MPSoC应用的电源参考设计.pdf》资料免费下载

2023-09-13 09:55:25 1

1 电子发烧友网站提供《Zynq UltraScale+MPSoC嵌入式设计教程.pdf》资料免费下载

2023-09-13 09:14:33 4

4 电子发烧友网站提供《Zynq UltraScale+ MPSoC中的隔离方法应用笔记.pdf》资料免费下载

2023-09-15 14:49:14 0

0 电子发烧友网站提供《Zynq UltraScale+ MPSoC生产勘误表.pdf》资料免费下载

2023-09-15 10:35:56 0

0 电子发烧友网站提供《Zynq UltraScale+设备技术参考手册.pdf》资料免费下载

2023-09-15 10:18:18 5

5 电子发烧友网站提供《Zynq UltraScale+ MPSoC数据手册:DC和AC开关特性.pdf》资料免费下载

2023-09-15 10:27:21 0

0 电子发烧友网站提供《Zynq UltraScale+ MPSoC验证数据手册.pdf》资料免费下载

2023-09-15 10:13:41 0

0 电子发烧友网站提供《Zynq UltraScale+ MPSoC软件开发人员指南.pdf》资料免费下载

2023-09-15 10:16:47 8

8 电子发烧友网站提供《采用Zynq UltraScale+ MPSoC满足汽车ESD和SEED要求.pdf》资料免费下载

2023-09-18 09:44:32 1

1

正在加载...

电子发烧友App

电子发烧友App

评论