近年来,由于成像技术的不断进步以及图像应用领域的拓宽,数字图像包含的数据量与日俱增,图像处理算法也越来越复杂[1]。目前应用普遍的数字信号处理器(Digital Signal Processor,DSP)和图形处理器(Graphics Processing Unit,GPU)技术虽然在实现图像处理上有着廉价、易于编程的优点,但是在性能、功耗、实时性方面,它们与FPGA相比仍有巨大的差距,难以满足嵌入式图像领域不断增长的灵活性、高性能、低功耗的要求。大量研究表明,采用FPGA实现图像处理能够获得较高的计算性能。因此,从计算性能、实时性的角度考虑,FPGA是嵌入式图像处理应用的理想选择方案[2]。

Xilinx公司的ZYNQ-7000系列产品集成了最新工艺的ARM Cortex-A9双核处理器与高性能的FPGA。作为新一代的可编程片上系统,ZYNQ-7000 SoC非常适合于计算密集、功能丰富的嵌入式应用设计。Xilinx公司的Vivado HLS工具将C语言、C++以及系统C语言引入到可编程逻辑设计中,而无须通过传统的硬件描述语言编写复杂的程序,大大地加速了IP创建,满足了处理算法的灵活性[3]。设计利用Vivado HLS工具实现了可变参数的拉普拉斯算子图像滤波算法,将生成的IP加入到ZYNQ-7000的可编程逻辑部分,用于处理OV7670摄像头采集到的图像数据。移植Ubuntu Linux桌面系统到ZYNQ-7000双核处理器中,利用Qt工具编写上位机人机交互控制界面与下位机显示程序,实现了嵌入式Linux可视化实时图像处理系统。

1 系统总体结构

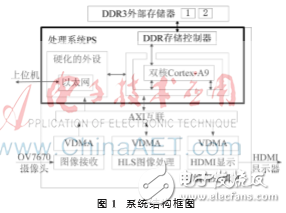

ZYNQ-7000嵌入式数字图像处理系统结构框图如图1所示,系统主要由OV7670摄像头、ZYNQ-7000 SoC、数据存储单元DDR3、HDMI显示器以及上位机等组成。ZYNQ-7000 SoC作为整个实时处理系统的核心,包括处理系统(Processing System,PS)和可编程逻辑(Programmable Logic,PL)两部分,其中PS部分主要包含了双ARM Cortex-A9核,PL部分包含了传统意义的DSP资源和FPGA逻辑单元。

1.1 PL部分实现的功能

可编程逻辑PL部分实现的主要功能如下:

(1)从OV7670摄像头中获取图像数据,并通过视频存储器直接访问(Video Direct Memory Access,VDMA)传输至DDR3存储芯片中存储;

(2)将DDR3中存储的图像数据通过VDMA传输到可变参数的拉普拉斯滤波算法IP模块进行图像处理,并把处理生成的图像数据通过VDMA重新传输到DDR3;

(3)PL中的显示模块配合VDMA构成嵌入式Linux的硬件显示单元。

图像采集采用OV7670摄像头,OV7670图像传感器体积小、工作电压低,提供单片VGA摄像头和影像处理器的所有功能。通过SCCB 总线控制,可以输出整帧、子采样、取窗口等方式的各种分辨率的8位影像数据。设计选用RGB565、VGA640×480作为输出格式,将相应的寄存器值通过SCCB控制模块写入到寄存器中,并把采集的数据通过AXI4 Stream接口协议写入到DDR3中。在该设计中,通过硬件描述语言实现SCCB图像控制与图像接收模块的设计。

1.2 PS部分实现的功能

处理系统PS部分实现的主要功能如下:

(1)运行Ubuntu桌面系统,为上层应用提供操作系统支持;

(2)调用编写的VDMA、HDMI图像显示驱动实现与PL数据交互、桌面系统显示的功能;

(3)实现Qt编写的上层应用程序及网络编程等。

如图1所示,VDMA提供了PL与DDR3存储器进行高速数据传输的机制。VDMA具有两个数据端口:MM2S和S2MM。MM2S和S2MM的最大数据位宽均为64 bit,缓存区深度为512 B[4]。其中S2MM端口实现图像数据从PL向DDR3存储器传输,MM2S端口实现图像数据从DDR3存储器向PL传输。ARM处理器可以通过通用接口AXI_GP对VDMA进行控制。

2 拉普拉斯算子滤波算法的实现

2.1 拉普拉斯算子滤波算法

拉普拉斯算子是图像处理技术中常见的一种增强算子,因为具有旋转不变性、实现简单等特点,被广泛地应用于图像锐化和高频增强等算法中。图像信号中,高频分量一般对应于图像的边缘轮廓,采用拉普拉斯算子的图像滤波算法能够实现图像锐化、增强图像轮廓清晰度的效果。拉普拉斯算子是最简单的各向同性微分算子,具有旋转不变性。一个二维图像函数的拉普拉斯变换是各向同性的二阶导数,定义为:

该方程的离散形式为:

拉普拉斯算子可以表示成模板的形式,如图2(a)所示,图2(b)表示其扩展模板,图2(c)和图2(d)则分别表示其他两种拉普拉斯的实现模板。

2.2 Vivado HLS实现算法编写

Vivado HLS利用C语言、C++语言以及系统C语言提供的高级结构来提高抽象层次,提供数据原语方便使用基础硬件构建IP模块。与使用RTL相比,Vivado HLS代码更加紧凑,可读性和可维护性更加优良,可以更轻松地实现各种接口协议,从简单的FIFO接口到完整的AXI4 Stream,满足不同模块间的数据通信。

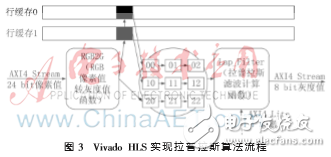

Vivado HLS实现拉普拉斯算法流程如图3所示。数据处理按照图中箭头依次进行,数据在单个单元中并行运算或在不同单元间并行移动。每个时钟周期AXI4 Stream接口将24 bit的一个像素数据送入算法模块中,先经过灰度处理,然后存入2×640的行缓存中,行缓存和新的数据构成3×3的窗口数据,窗口的9个数据和AXI_GP接口传输进来的拉普拉斯算子参数进行运算得到一个新的8 bit像素数据送回到DDR3中。

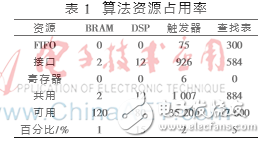

编写的算法在XC7Z010器件上的资源占用率如表1所示,可以看出,只用了PL很少的资源便实现了图像滤波算法。

2.3 Qt实现参数控制程序

良好的人机交互功能是嵌入式系统重要的一部分[5]。设计采用Qt Creator开发工具在PC上实现了控制端应用程序,如图4所示。PC通过以太网与下位机进行连接,在控制端输入不同的拉普拉斯算子,系统会产生不同的滤波效果,并将滤波后的图像显示在下位机的HDMI显示器上。

3 设计仿真与系统测试

3.1 Vivado HLS仿真

Vivado HLS除了将高效的编程代码转换为IP以外,还提供了另一项重要功能:C语言仿真和C/RTL协同仿真。C语言仿真中C/C++的编译和执行与常见的C/C++程序相同,具有良好的可读性和高效性。C/RTL协同仿真会根据C/C++测试平台自动生成RTL测试平台,设置并执行RTL仿真,检查实现方案的正确性。C语言仿真测试代码如下:

IplImage* src=http://file.elecfans.com/web1/M00/4C/02/pIYBAFqx-tuAJJz7AADgwlEY8QE555.jpg"text-indent: 2em;"> AXI_STREAM src_axi, dst_axi;//定义流数据类型变量

IplImage2AXIvideo(src, src_axi);

//图片转换为流数据类型

Laplasian_fil(&lap00,&lap01,&lap02,&lap10,&lap11,

&lap12,&lap20,&lap21,&lap22,src_axi, dst_axi);

//滤波算法主函数

AXIvideo2IplImage(dst_axi, dst);

//流数据类型转换为图片

cvSaveImage("lena_result.jpg", dst);//保存图片

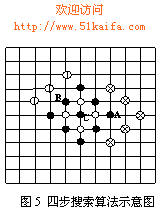

测试程序首先将本地用于测试的图片转换为AXI4 Stream接口协议数据,并设置拉普拉斯算子的值,然后将图片数据和拉普拉斯算子以参数的形式送入到图像滤波算法中,滤波后的图片会以jpg的形式存入本地。测试原图片及生成图片如图5所示。

3.2 系统测试

测试系统采用Xilinx公司提供的ZyBo开发板,该开发板搭载了XC7Z010主芯片,扩展外设通过PMOD接口与OV7670摄像头进行连接,PC通过板载以太网接口和串行接口与ZyBo通信,HDMI显示运行的Ubuntu桌面系统。

控制端输入图2中不同的拉普拉斯算子得到的处理结果如图6所示,结果完全满足每秒30帧、RGB640×480格式图像实时滤波的要求。

4 结论

基于ZYNQ-7000异构架构的图像处理系统不但可以实现嵌入式操作系统相关的任务,如图形界面、用户输入、网络、DDR3控制等,还可以提供高性能实时图像处理的功能[6]。采用Xilinx最新的Vivado HLS工具进行FPGA高层次设计对图像算法进行加速,能够有效提高设计效率,并且能够快速生成工业标准的IP核,有利于进一步实现系统集成。设计的实验和验证结果表明了基于ZYNQ-7000异构架构和Vivado HLS工具的实时图像处理系统易于移植,便于针对特定应用定制,为未来的高性能图像处理提供了较高的工程应用与参考价值。

电子发烧友App

电子发烧友App

评论