AXI STREAM FIFO如何设置双时钟

- 异步时钟(9361)

相关推荐

Zynq中AXI4-Lite和AXI-Stream功能介绍

等于b0000(非缓冲和非缓存)。 5) 不支持互斥性操作。 Zynq中AXI-Stream功能 AXI-Stream协议作为一个标准接口,用于连接数据交换元

2020-09-27 11:33:02 8051

8051

8051

8051

Xilinx zynq AXI总线全面解读

,是面向地址映射的接口,允许最大256轮的数据突发传输; (B)AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。 (C)AXI4-Stream:(F

2020-12-04 12:22:44 6179

6179

6179

6179

ZYNQ SOC案例开发:AXI DMA使用解析及环路测试

provides high-speed data movement between system memory and an AXI4-Stream-based target IP such as AXI

2020-12-31 09:52:02 7166

7166

7166

7166

同步FIFO设计详解及代码分享

FIFO (先入先出, First In First Out )存储器,在 FPGA 和数字 IC 设计中非常常用。 根据接入的时钟信号,可以分为同步 FIFO 和异步 FIFO 。

2023-06-27 10:24:37 1199

1199

1199

1199

AXI VIP当作master时如何使用

AXI VIP当作master时如何使用。 新建Vivado工程,并新建block design,命名为:axi_demo 新建axi vip,参数设置如下,第一个参数设置为Master,其他都保持

2023-07-27 09:19:33 633

633

633

633

XILINX FPGA IP之AXI Traffic Generator

AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互连以及其他AXI4系统外设上生成特定序列(流量)。它根据IP的编程和选择的操作模式生成各种类型的AXI事务。是一个比较好用的AXI4协议测试源或者AXI外设的初始化配置接口。

2023-11-23 16:03:45 580

580

580

580

AXI-stream数据传输过程

。AXI4-Stream的核心思想在于流式处理数据。 图 4‑58 AXI-Stream Interface 全局信号 1.ACLK 全局时钟信号,在上升沿时对信号采样。所有的输入信号都通过上升沿采集,所有

2021-01-08 16:52:32

AXI 1G / 2.5G以太网子系统在AXI4-Stream接口中的最大“数据包”大小是多少?

个恒定的6个32位字,所以必须注意帧数据或控制数据的缓冲区填满的条件。防止无序状况。“我还说在AXI4-Stream接口中“数据是以数据包的形式传输而不是连续流”。最大9Kb“帧”大小是否也适用于通过AXI4-Stream接口发送的最大“数据包大小”?问候。

2020-05-25 09:37:36

AXI FIFO和AXI virtual FIFO这两个IP的使用方法

软件中设置非常简单。我们需要在软件中执行以下操作:配置 AXI Stream FIFO读取FIFO的占用情况从 FIFO 中读出指定的字数在应用软件中根据需要处理样品#include <

2022-11-04 11:03:18

AXI VDMA可以工作,但是少数线路不正确,总是丢包

较大的图像总是会丢失数据包。我认为问题可能是vdma fifo设置。我的项目:结果比较system.mhs 11 KB以上来自于谷歌翻译以下为原文Hi, allI met a problem

2019-03-01 12:26:32

AXI4S接口视频协议在视频IP中的应用总结

在一起。1.2.2 多像素编码示例AXI4S视频接口支持每时钟双像素或四像素,对于RGB、YUV444和YUV420色彩空间,每个分量有8位、10位、12位和16位。当参数“每个组件的最大位数”设置为

2022-11-14 15:15:13

AXI接口协议详解

。 AXI4-Stream:(For high-speed streamingdata.)面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。 Stream的理解,可以想象一下

2022-10-14 15:31:40

AXI接口协议详解

机数据本次传输有效;(8) TUSER信号 :用户定义信号,宽度为128bit。对于AXI4-Stream总线命名而言,除了总线时钟和总线复位,其他的信号线都是以T字母开头,后面跟上一个有意义的单词

2022-04-08 10:45:31

AXI流FIFO挂起

“base_address + 0x1C”之前我需要采取的任何步骤以上来自于谷歌翻译以下为原文I am using the AXI stream FIFO to stream data

2019-04-24 12:54:04

axi4-stream combiner问题的解决办法?

AXI4-Streamslave接口上TDATA信号的宽度(以字节为单位)。 AXI4-Stream主接口TDATA宽度是此值乘以从属接口数参数。此参数是一个整数,可以在0到(512 /从站接口数)之间变化。设置为0以省略

2020-08-20 14:36:50

axi4-stream互连问题如何解决

你好,大家好。我正在使用EMI14.4和xc6v315t。我正在尝试模拟IP CORE.It的axi4-stream interconnect.I配置ip为6siand 4mi。但是当我用ismI模拟它时发现s_tready很低,有什么问题?

2020-06-18 15:08:59

FPGA片内FIFO的Xilinx库设置和功能仿真

、57、58……。●FIFO为空时,指示信号fifo_empty为高电平,一旦写入数据后的第2个时钟周期,fifo_empty为低电平,表示当前FIFO不空。●读使能信号fifo_rden拉高时,第2个

2019-04-08 09:34:40

FPGA问题 PL端获取的数据和时钟 如何存入DDR中

RT,求助自己做了一个PL核 获取时钟和数据 并输出 如何把数据传入DDR中,有现成的IP核还是有相关的教程吗开发工具 vivado 除了 使用Video In to AXI4-Stream 和 AXI Video Direct Memroy Access 有没有别的方法麻烦大家了

2022-07-20 09:24:20

Vivado HLS直通AXI Stream IP-Core如何分配

嗨,我已经创建了一个带有IP-Core的硬件设计。但它不能正常工作。对于我提到的调试问题,我创建了一个IP-Core,然后通过AXI Stream。所以我可以检查我的IP-Core是否不起作用

2020-04-14 09:25:10

ZYNQ中不同应用的DMA总结

到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<

2022-03-31 11:39:10

vsync和hsync生成以及视频输入到axi流兼容性

视频信号,而我正在传输像素,但我不清楚是否必须包括空白同步。如果存在限制或最小值,我需要多少个时钟才能保持高hsync和vsync ....使用videoIn_to_axi-stream IP核可

2019-04-23 06:00:37

【FPGA开源教程连载】第十五章 嵌入式块RAM使用之FIFO

。通过设置双时钟FIFO的写入位宽为16位,读取位宽为8位,则可以实现将16位的ADC数据转换为以太网支持的8位发送数据,然后通过以太网发送到PC机。4.实现FIFO的方法在AlteraFPGA中使

2017-01-04 16:41:25

为什么我的vout初始化标志总是向上且没有达到锁定状态?

+ DataPattern >> v_vid_in_axi4s >> AXI4-Stream >> v_axi4s_vid_out \\ ====== VTG(计时)==== //`我

2019-07-15 09:47:54

介绍一下不带数据的Stream—Event

使用SpinalHDL lib中所提供的Event:Event对应一个payload为NoData的Stream信号,而NoData顾名思义,其实现为一个空的Bundle:》Example这里我们以Axi

2022-06-27 16:07:04

使用外部时钟驱动AXI外设无法运行

嗨,我一直在尝试使用外部时钟驱动一些AXI外设,尽管该设计已经过测试,使用相同频率的内部时钟(Zynq PLL生成),但在使用外部时钟时无法运行。分机时钟通过时钟使能引脚提供,路由到MMCM,通过

2019-04-09 09:12:26

关于异步fifo的安全问题:

由于,如果异步fifo的双口ram真的空了,而跨时钟域延迟造成的rdempty仍然非空,则读fifo的逻辑,就有可能根据rdempty信号(非空指示),发出将导致错误的读请求rdreq5. 另外,如果

2018-03-05 10:40:33

可以从AXI流端口获取输出采样数据吗?

大家好我对7系列家族的XADC向导提出了一个小问题。我设计了我的XADC并且它运行成功,但是因为我想在其后放置一个FIFO内存,我想在XADC中启用AXI4Stream以实现更好的同步。所以我现在

2020-05-20 14:53:11

可以在EDK中使用Axi4Stream接口/总线吗?

你好,我正在EDK中使用axi4stream。有人可以帮助我如何使用通过Vivado高级综合(HLS)生成的ap_fifo / axi4stream接口可以在EDK中使用吗?我正在使用Export

2019-02-28 13:47:30

如何使用AXI配置的ILA调试PCIe AXI接口?

user_clk从端点连接到AXI configuredILA的时钟端口时,似乎永远不会出现在硬件管理器中(在调试探针窗口中)。 a)这是否必须对自由运行时钟要求做些什么? b)我使用了缓冲的系统时钟(来自

2019-09-25 09:26:14

如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法

到。axi-vip和axi-stream-vip都有自带的仿真例程,常用的功能在仿真例程中都有涉及。2.1设置VIP支持的Outstanding读写深度例如,设置slave vip的outstanding深度为

2022-10-09 16:08:45

如何使用虚拟FIFO控制器从XADC获取单通道数据

我正在尝试使用DDR3 RAM作为缓冲器,使用虚拟FIFO控制器从XADC获取单通道数据。我设置VFIFO的突发模式为4096字节,并分配了8192个4K页面,这应该给我32MB;从技术上讲,我

2020-05-20 14:22:46

如何吧AXI4-stream时钟转换器tkeep设置为null?

大家好,我正在两个时钟域之间穿过AXI4-Stream,并尝试使用AXI4-Stream时钟转换器核心,使用tkeep端口但是在合成时它被Vivado 2015.2在实例化时删除了!这是综合警告

2020-05-08 08:56:14

如何将AXI4-Stream与CH7301接口?

我有SP605&amp; ML506 Xilnx开发板。我想从FPGA驱动CH7301芯片。我正在寻找一些帖子或应用笔记,可以帮助我把这两件事放在一起。我一直在关注核心AXI4-Stream到视频

2020-03-20 09:04:51

如何计算异步FIFO深度和单独的时钟源

时钟,使得它们来自单独的板载振荡器。这导致了fifo溢出。我将深度更新为128,然后再次运行。如果有人可以告诉我发生了什么,以及这个FIFO设置是否可以可靠地处理来自不同来源的时钟,我真的很感激。我打算

2019-04-09 06:25:58

有人有经验AXI4-Stream到视频输出IP核吗?

无论我如何尝试,AIVO(视频,Vsync,Hsync,DE)的所有输出在模拟中始终保持为0。我检查了端口连接,并单独模拟VTC和TPG,它们都运行良好。有没有人有经验的AXI4-Stream到视频输出

2019-03-08 10:00:05

构建自定义AXI4-Stream FIR滤波器的步骤

1、构建自定义AXI4-Stream FIR滤波器 AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程

2022-11-07 16:07:43

求助verilog编写实现AXIStream-FIFO功能思路

),要用verilog实现AXI Stream的异步FIFO1、读写不同的时钟,设一个100M,另一个333M2、读写不同的位宽,设写为8bit,读为32bit3、fifo深度为324、控制信号没有

2014-02-21 16:24:45

溢出标志是否在Stream模式下不起作用?

FIFO_SRC_REG中的溢出标志。但它在代码运行期间从未设置过。所以我不应该在阅读和打印时丢失任何数据。我的问题:1.溢出标志是否在Stream模式下不起作用?即当新数据被覆盖时,它是否会保持高位

2019-05-23 08:59:20

看看Stream信号里是如何做跨时钟域握手的

popArea里stream.m2sPipe,这个版本效率相较于前者,略低一些:StreamFifoCC这个就没有什么好说的了,通过fifo来实现stream信号的跨时钟域,效率最高,资源相对也会多

2022-07-07 17:25:02

聊聊SpinalHDL中的FIFO

SpinalHDL对于Stream接口抽象的便捷性。而对于日常的逻辑电路设计而言,出现FIFO Overflow,underflow的常见原因就是我们将ren、wen声明为寄存器信号,而在处理时序上的不当导致

2022-06-30 15:28:00

请问AXI4-Stream到Video核心的技巧有什么?

大家好。我遇到了xilinx视频内核的问题,并试图解决这个问题好几周但都失败了。有人能给我一些关于AXI4-Stream到Video核心的技巧吗?我试图在我的项目中实现Video Scaler核心

2019-11-08 09:53:46

请问AXI-4流接口有没有可用的地址线?

嗨,我已经通过以太网MAC IP作为“LogiCORE IP 10千兆以太网MAC v13.1”U.G. PG072。由于我对AXI没有太多了解,因此我几乎没有查询读取AXI4-Stream接口

2020-04-28 10:00:42

请问可以使用AXI-Stream Broadcaster作为AXI开关吗?

我们可以使用AXI-Stream Broadcaster作为AXI开关吗?如果可能,我们需要控制切换哪个信号?我想开发小型应用程序,它涉及广播AXI流数据并将AXI流数据切换到特定的从站。在这个应用程序中,我们只有一个主站和8个从站。我们想在从站之间切换流数据。提前致谢。

2020-05-07 09:42:16

请问我对AXI4-Stream FIFO的理解不正确吗?

嗨,我正在研究Spartan 6的设计。数据来自PCIe IP核,频率为62.5MHz,通过AXI4-Stream FIFO同步到100 MHz系统时钟。这是一个示例波形;m_axis_tvalid

2019-08-12 07:29:20

谈谈FIFO阈值的阈值设置及深度计算

`立即学习—60天FPGA工程师入门就业项目实战特训营(3月16日开班) 谈谈FIFO阈值的阈值设置及深度计算1.什么是FIFO2.什么情况下使用FIFO3.什么FIFO的阈值4.FIFO的阈值

2020-02-19 21:09:35

异步FIFO结构

设计一个FIFO是ASIC设计者遇到的最普遍的问题之一。本文着重介绍怎样设计FIFO——这是一个看似简单却很复杂的任务。一开始,要注意,FIFO通常用于时钟域的过渡,是双时钟设计

2009-10-15 08:44:35 94

94

94

94Xilinx的LogiCORE IP Video In to AXI4

Xilinx的视频的IP CORE 一般都是 以 AXI4-Stream 接口。 先介绍一下, 这个IP的作用。 下面看一下这个IP 的接口: 所以要把标准的VESA信号 转为

2017-02-08 08:36:19 531

531

531

531

异步FIFO的设计分析及详细代码

位宽(每个数据的位宽) FIFO有同步和异步两种,同步即读写时钟相同,异步即读写时钟不相同 同步FIFO用的少,可以作为数据缓存 异步FIFO可以解决跨时钟域的问题,在应用时需根据实际情况考虑好fifo深度即可 本次要设计一个异步FIFO,深度为8,位宽也是8。

2017-11-15 12:52:41 7993

7993

7993

7993

AXI4Stream总线的FPGA视频系统的开发研究

基于AXI4Stream总线协议,在Xilinx公司提供的FPGA上实现了一个具有缺陷像素校正、色彩滤波阵列插值、图像降噪实时图像采集与显示功能的视频系统。AXI4Stream总线协议由ARM公司

2017-11-17 08:58:01 4189

4189

4189

4189如何解决异步FIFO跨时钟域亚稳态问题?

跨时钟域的问题:前一篇已经提到要通过比较读写指针来判断产生读空和写满信号,但是读指针是属于读时钟域的,写指针是属于写时钟域的,而异步FIFO的读写时钟域不同,是异步的,要是将读时钟域的读指针与写时钟域的写指针不做任何处理直接比较肯定是错误的,因此我们需要进行同步处理以后进行比较。

2018-09-05 14:29:36 5613

5613

5613

5613HLS Stream案例分析

第二步,不设置任何directive,直接执行C综合,此时会显示如下错误信息。该信息表明,在非dataflow区域使用默认的FIFO规模(这个FIFO是因为stream而生成的,默认深度

2019-04-24 17:36:14 9564

9564

9564

9564FPGA之FIFO练习3:设计思路

根据FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

2019-11-29 07:08:00 1609

1609

1609

1609一文详解ZYNQ中的DMA与AXI4总线

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI

2020-09-24 09:50:30 4289

4289

4289

4289

你必须了解的AXI总线详解

的转换 AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP-----AXI-Stream 的转换 AXI-Datamover:实现从 PS 内存到 PL 高速传输高速

2020-10-09 18:05:57 6391

6391

6391

6391

ZYNQ中DMA与AXI4总线

和接口的构架 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过

2020-11-02 11:27:51 3880

3880

3880

3880

AXI-Stream代码

突发传输规模。AXI4-Stream的核心思想在于流式处理数据。 图 4‑58 AXI-Stream Interface 全局信号 1.ACLK 全局时钟信号,在上升沿时对信号采样。所有的输入信号都通过

2020-11-05 17:40:36 2826

2826

2826

2826

如何在Altera FPGA中使用FIFO实现功能设计?

的缓存或者高速异步数据的交互。 二:FIFO有几种结构 FIFO从大的情况来分,有两类结构:单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO),其中双时钟FIFO又可以分为普通双时钟

2021-03-12 16:30:48 2796

2796

2796

2796

关于AXI4-Stream协议总结分享

XI4-Stream跟AXI4的区别就是AXI4-Stream去除了地址线,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时。由于AXI4-Stream协议(amba4_axi4_stream_v1_0_protocol_spec.pdf)没有时序图,

2022-06-23 10:08:47 1781

1781

1781

1781AXI4-Stream Video 协议和AXI_VDMA的IP核介绍

本文主要介绍关于AXI4-Stream Video 协议和AXI_VDMA的IP核相关内容。为后文完成使用带有HDMI接口的显示器构建图像视频显示的测试工程做准备。

2022-07-03 16:11:05 6846

6846

6846

6846AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI4 是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解

2022-07-04 09:40:14 5818

5818

5818

5818FIFO的阈值如何设置

FIFO是First in First out 的缩写,一般是由寄存器reg或者ram搭起来的,相对于普通存储器而言,FIFO没有地址可操作的地址总线,因而使用比较方便,但是数据只能像水流一样排队进排队出。

2022-08-19 09:02:47 1830

1830

1830

1830使用AXI4总线实现视频输入输出

Xilinx vivado下通常的视频流设计,都采用Vid In to axi4 stream --> VDMA write --> MM --> VDMA read -->

2022-10-11 14:26:03 4556

4556

4556

4556同步FIFO之Verilog实现

FIFO的分类根均FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

2022-11-01 09:57:08 1315

1315

1315

1315异步FIFO之Verilog代码实现案例

同步FIFO的意思是说FIFO的读写时钟是同一个时钟,不同于异步FIFO,异步FIFO的读写时钟是完全异步的。同步FIFO的对外接口包括时钟,清零,读请求,写请求,数据输入总线,数据输出总线,空以及满信号。

2022-11-01 09:58:16 1189

1189

1189

1189AXI FIFO和AXI virtual FIFO两个IP的使用方法

FIFO 是我们设计中常用的工具,因为它们使我们能够在进行信号和图像处理时缓冲数据。我们还使用异步FIFO来处理数据总线的时钟域交叉问题。

2022-11-04 09:14:11 3214

3214

3214

3214异步fifo详解

和写入数据(对于大型数据存储,在性能上必然缓慢),其数据地址是由内部读写指针自动加一完成的,不能像普通的存储器一样,由地址线决定读取或者写入某个特定地址的数据,按读写是否为相同时钟域分为同步和异步FIFO,这里主要介绍异步FIFO,主要用于跨时钟域传输数据。 FIFO是

2022-12-12 14:17:41 2790

2790

2790

2790Verilog电路设计之单bit跨时钟域同步和异步FIFO

FIFO用于为匹配读写速度而设置的数据缓冲buffer,当读写时钟异步时,就是异步FIFO。多bit的数据信号,并不是直接从写时钟域同步到读时钟域的。

2023-01-01 16:48:00 941

941

941

941FIFO的原理和设计

FIFO(First In First Out)是异步数据传输时经常使用的存储器。该存储器的特点是数据先进先出(后进后出)。其实,多位宽数据的异步传输问题,无论是从快时钟到慢时钟域,还是从慢时钟到快时钟域,都可以使用 FIFO 处理。

2023-03-26 16:00:21 1824

1824

1824

1824

FIFO使用及其各条件仿真介绍

FIFO(First In First Out )先入先出存储器,在FPG设计中常用于跨时钟域的处理,FIFO可简单分为同步FIFO和异步FIFO。

2023-04-25 15:55:28 2893

2893

2893

2893

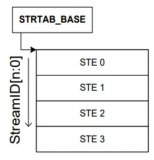

ARM SMMU Data structures之Stream Table

incoming transaction的StreamID可以找到一个STE。SMMU支持两种Stream table格式,格式由Stream table base registers设置。

2023-05-11 09:22:57 714

714

714

714

跨时钟域电路设计:多位宽数据通过FIFO跨时钟域

FIFO是实现多位宽数据的异步跨时钟域操作的常用方法,相比于握手方式,FIFO一方面允许发送端在每个时钟周期都发送数据,另一方面还可以对数据进行缓存。需要注意的是对FIFO控制信号的管理,以避免发生

2023-05-11 14:01:27 1641

1641

1641

1641

Video In to AXI4-Stream IP核知识介绍

大家好!今日分享一些关于Video In to AXI4-Stream IP 核的知识。在具体学习IP核的过程中,我也将分享一些关于如何看xilinx英文文档的技巧。

2023-05-18 14:55:16 966

966

966

966

FIFO设计—同步FIFO

FIFO是异步数据传输时常用的存储器,多bit数据异步传输时,无论是从快时钟域到慢时钟域,还是从慢时钟域到快时钟域,都可以使用FIFO处理。

2023-05-26 16:12:49 978

978

978

978

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】

从 FPGA 应用角度看看 AMBA 总线中的 AXI4 总线。

2023-06-21 15:21:44 1729

1729

1729

1729

AXI实战(二)-AXI-Lite的Slave实现介绍

可以看到,在AXI到UART中,是通过寄存器和FIFO进行中介的。因为从AXI总线往里看,其控制的是就是地址上所映射的寄存器。

2023-06-27 10:12:53 2229

2229

2229

2229

跨时钟设计:异步FIFO设计

在ASIC设计或者FPGA设计中,我们常常使用异步fifo(first in first out)(下文简称为afifo)进行数据流的跨时钟,可以说没使用过afifo的Designer,其设计经历是不完整的。废话不多说,直接上接口信号说明。

2023-07-31 11:10:19 1220

1220

1220

1220

LogiCORE IP AXI4-Stream FIFO内核解决方案

LogiCORE IP AXI4-Stream FIFO内核允许以内存映射方式访问一个AXI4-Stream接口。该内核可用于与AXI4-Stream IP接口,类似于LogiCORE IP AXI以太网内核,而无需使用完整的DMA解决方案。

2023-09-25 10:55:33 497

497

497

497

为什么异步fifo中读地址同步在写时钟域时序分析不通过?

为什么异步fifo中读地址同步在写时钟域时序分析不通过? 异步FIFO中读地址同步在写时钟域时序分析不通过的原因可能有以下几个方面: 1. 读地址同步在写时钟域时序分析未覆盖完全 在时序分析时,可能

2023-10-18 15:23:55 312

312

312

312同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用

简单的一种,其特点是输入和输出都与时钟信号同步,当时钟到来时,数据总是处于稳定状态,因此容易实现数据的传输和存储。 而异步FIFO则是在波形的上升沿和下降沿上进行处理,在输入输出端口处分别增加输入和输出指针,用于管理数据的读写。异步FIFO的输入和输出可同时进行,中间可以

2023-10-18 15:23:58 790

790

790

790AXI传输数据的过程

以AXI4为例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有关IP核中,经常见到AXI总线接口,AXI总线又分为三种: •AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

386

386

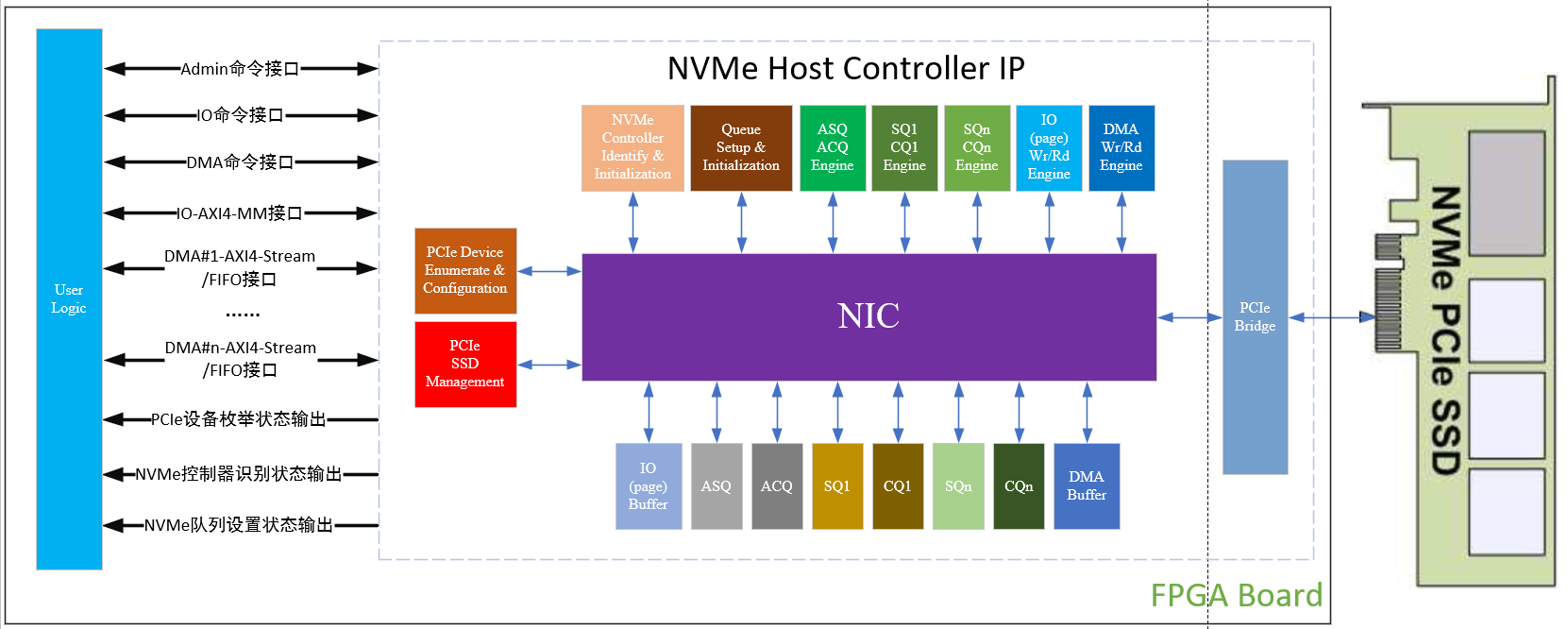

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

NVMe Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数

2024-02-18 11:27:50 219

219

219

219

Xilinx高性能PCIe DMA控制器IP,8个DMA通道

或Scather Gather DMA,提供FIFO/AXI4-Stream用户接口。

基于PCI Express Integrated Block,Multi-Channel PCIe RDMA

2024-02-22 11:11:55 156

156

156

156

电子发烧友App

电子发烧友App

评论