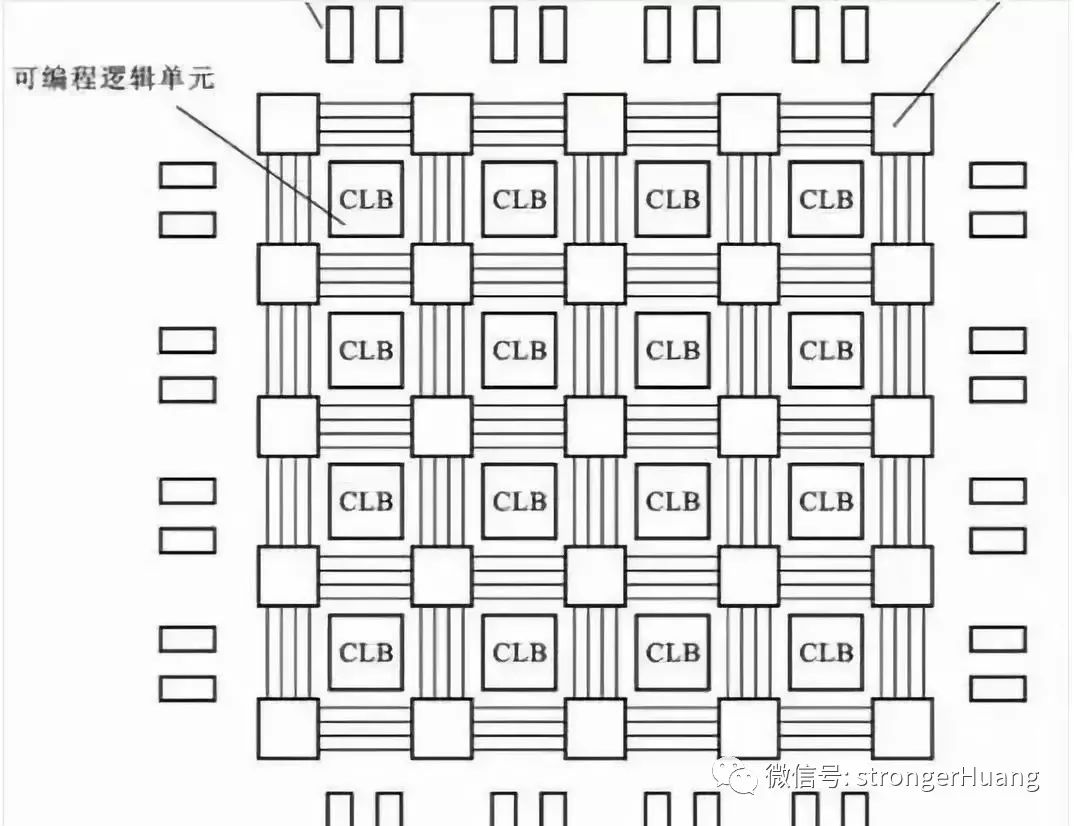

与以前的自我相比,现在的FPGA不再仅仅是查找表(LUT)和寄存器的集合,而是已经远远超出了现在的体系结构的探索,为未来的ASIC提供设计架构。

该系列器件现在包括从基本的可编程逻辑一直到复杂的SoC。在各种应用领域(包括汽车,AI,企业网络,航空航天,国防和工业自动化等)中,FPGA可以使芯片制造商以在必要时可以更新的方式来实施系统。在协议,标准和最佳实践仍在发展以及要求ECOS保持竞争力的新市场中,这种灵活性至关重要。

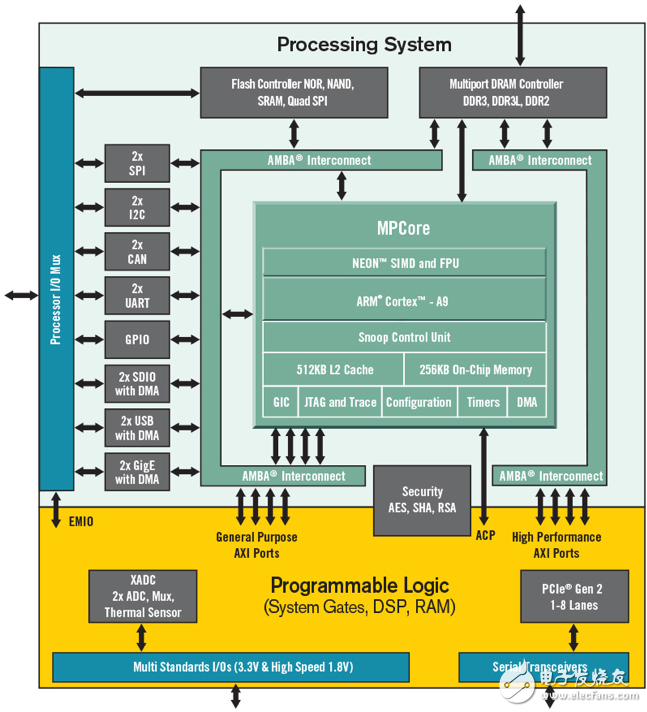

Aldec市场总监Louie de Luna表示,这是Xilinx决定为其Zynq FPGA添加Arm核心以创建FPGA SoC的原因。 “最重要的是,供应商已经改进了工具流程。这对Zynq产生了很大的兴趣。他们的SDSoC开发环境看起来像C,这对开发人员来说很好,因为应用程序通常是用C语言编写的。所以他们使用软件功能并允许用户将这些功能分配给硬件。“

Xilinx’s Zynq-7000 SoC. Source: Xilinx

这些FPGA中的一些不仅仅是类似SoC的。它们本身就是SoC。

“他们可能包含多个嵌入式处理器,专用计算引擎,复杂接口,大容量存储器等等,”OneSpin Solutions综合验证产品专家Muhammad Khan说。 “系统架构师计划和使用FPGA的可用资源,就像他们为ASIC所做的那样。设计团队使用综合工具将他们的SystemVerilog,VHDL或SystemC RTL代码映射到基础逻辑元素中。对于大部分设计过程来说,有效瞄准FPGA和瞄准ASIC或全定制芯片之间的差异正在缩小。”

ArterisIP首席技术官Ty Garibay非常熟悉这一演变。 “从历史上看,Xilinx在2010年开始走Zynq的道路,他们定义了一款产品,该产品将Arm SoC的硬宏纳入到现有FPGA中,” 他说。 “然后Intel(Altera)聘请我做基本相同的事情。价值主张是SoC子系统是许多客户想要的东西,但由于SoC特别是处理器的特性,它们不适合在FPGA上合成。将这种级别的功能嵌入到实际的可编程逻辑中是令人望而却步的,因为它几乎将整个FPGA用于该功能。但是它可以作为整个FPGA芯片的一小部分或一小部分,作为一个硬性功能。你放弃了为SoC提供真正可重构逻辑的能力,但它可以编程为软件,以这种方式来改变功能。

这意味着可以在该结构中具有软件可编程的功能,硬宏和硬件可编程功能,他们可以一起工作,他说。 “有一些相当不错的市场,尤其是在低成本汽车控制领域,无论如何,传统上都是FPGA旁边的放一个中等性能微控制器型器件。客户只会说,我只是将整个功能放到FPGA芯片的硬宏上,以减少电路板空间,减少BOM,降低功耗。”

这符合过去30年FPGA的发展,原来的FPGA只是可编程结构和一堆I/O。随着时间的推移,内存控制器与SerDes,RAM,DSP和HBM控制器一起被硬化了。

Garibay说:“FPGA供应商一直在继续增加芯片面积,但也继续增加越来越多的硬逻辑,这些逻辑被相当大比例的客户群普遍使用。” “今天发生的事情是将其扩展到软件可编程的一面。在这个ARM SoC之前添加的大多数东西都是不同形式的硬件,主要与I / O有关,但也包括DSP,通过强化它们来节省可编程逻辑门是有意义的,因为有足够的计划效用。 ”

一个观点问题

这基本上已经将FPGA变成了瑞士军刀。

“如果你缩短时间,那只是一堆LUT和寄存器,而不是门,”NetSpeed Systems市场和业务开发副总裁Anush Mohandass说。 “他们有一个经典问题。如果您将任何通用任务与其特定于应用程序的版本进行比较,那么通用计算将提供更大的灵活性,而特定于应用程序的计算则会提供一些性能或效率优势。赛灵思和Intel(Altera)试图越来越多地与其结盟,他们注意到几乎每个FPGA客户都拥有DSP和某种形式的计算。所以他们加入了Arm内核,他们加入了DSP内核,他们加入了所有不同的PHY和常用的东西。他们加强了这一点,这使得效率更高,并且性能曲线变得更好。”

这些新功能为FPGA在各种新兴市场和现有市场中发挥重要作用打开了大门。

“从市场角度来看,您可以看到FPGA肯定会进入SoC市场,”Synopsys的高级营销总监Piyush Sancheti表示。 “你是否在做一个FPGA或一个成熟的ASIC是经济的。这些线条开始模糊不清,我们当然看到越来越多的公司 - 特别是在某些市场 - 正在开展FPGA生产经济性更好的生产领域。”

从历史上看,FPGA已经用于原型制造,但对于生产用途而言,它仅限于航空航天,国防和通信基础设施等市场,Sancheti说。 “现在市场正在扩展到汽车,工业自动化和医疗设备。”

AI,这是一个蓬勃发展的FPGA市场

一些采用FPGA的公司是希望优化其IP或AI/ML算法性能的系统供应商/OEM。

“NetSpeed的Mohandass表示:”他们想要开发自己的芯片,并且其中很多人开始做ASIC,可能有点吓人。 “他们也可能不想花费3000万美元的晶圆成本来获得芯片。对他们来说,FPGA是一个有效的切入点,他们拥有独特的算法,他们自己的神经网络,他们可以看到它是否能够提供他们所期望的性能。”

西门子公司Mentor的Catapult HLS综合与验证高级产品营销经理Stuart Clubb表示,目前AI应用面临的挑战是量化。 “需要什么样的网络?我如何建立这个网络?什么是内存架构?从网络开始,即使你只有几层,并且你有很多数据有很多系数,但它很快就会转化为数百万个系数,并且存储带宽变得非常可怕。没有人真正知道什么是正确的架构。如果答案不知道,你不会跳进来建立一个ASIC。”

在企业网络领域,最常见的问题是密码标准似乎一直在变化。 Mohandass表示:“与其尝试构建ASIC,不如将其放在FPGA中,并使密码引擎更好。” “或者,如果您在全球网络方面进行任何类型的数据包处理,FPGA仍然为您提供更多的灵活性和更多的可编程性。这就是灵活性起作用的地方,并且他们已经使用了它。你仍然可以称之为异构计算,它仍然看起来像一个SoC。”

新规则

随着新一代FPGA SoC的使用,旧规则不再适用。 “具体来说,如果你在电路板上进行调试,你做错了,”Clubb指出。 “虽然开发板上的调试被认为是一种成本较低的解决方案,但这可以追溯到能够说的早期阶段:'它是可编程的,您可以在它上面放置一个示波器,您可以查看并查看发生了什么。但现在说:'如果我发现了一个错误,我可以修复它,在一天内编写一个新的比特流,然后将它重新放回到电路板上,然后找到下一个错误,'这太疯狂了。这是你在员工的时间被视为不是成本的领域看到的很多心态。管理层不会购买模拟器或系统级工具或调试器,因为'我只是付钱让这个人完成工作,而且我会尖叫他,直到他努力工作。”

他说,这种行为仍然很常见,因为有足够多的公司以每年下降10%的态度让每个人都脚踏实地。

但是,FPGA SoC是真正的SoC,需要严格的设计和验证方法。 “构造可编程的事实并不会真正影响设计和验证,”Clubb说。 “如果你制作SoC,是的,你可以按照我听到的一些客户所说的'乐高'工程。这是框图方法。我需要一个处理器,一个内存,一个GPU,其他一些零件,一个DMA内存控制器,WiFi,USB和PCI。这些都是您组装的'乐高'积木。麻烦的是你必须验证他们的工作,并且他们一起工作。”

尽管如此,FPGA SoC系统开发人员正在迅速赶上其验证方法所关注的SoC系统。

“他们并不像传统的芯片SoC开发人员那样先进,他们的处理思路是'这将花费我200万美元,所以我最好做好准备',因为[使用FPGA]的成本是更低,“Clubb说。 “但是如果你花费200万美元开发FPGA,并且你弄错了,现在你将花费三个月的时间修复这些bug,但仍然有问题需要解决。球队有多大?要花多少钱?上市时的惩罚是什么?这些都是非常难以清晰量化的成本。如果您处于消费领域,那么在圣诞节期间您真的很关心如何使用FPGA几乎不太可能,所以这有一个不同的优先级。在定制芯片中完成SoC的总体成本和风险,并拉动触发器。而且还会说:'这是我的系统,我完成了',你看不到那么多。众所周知,这个行业正在整合,而且大筹码的大牌球员越来越少。每个人都必须找出一种方法来实现,而这些FPGA正在实现这一目标。”

新的折衷选择

Sancheti说,工程团队设计意图让他们的选择对目标设备开放并不少见。 “我们看到许多公司创建RTL并对其进行验证,几乎不知道他们是否要去做FPGA或ASIC,因为很多时候这个决定可能会改变。您可以从FPGA开始,如果达到一定数量,经济可能会有利于调试ASIC。”

对于今天的AI应用空间尤其如此。

eSilicon营销副总裁Mike Gianfagna表示:“加速AI算法的技术正在发展。 “显然,人工智能算法已经存在了很长一段时间,但现在我们突然间在如何使用它们方面变得更加复杂,并且以接近实时的速度运行它们的能力,这是非常神奇的。它从CPU开始,然后转移到GPU。但即使是GPU也是一种可编程器件,所以它具有一定的通用性。虽然架构擅长并行处理,但因为这就是图形加速的全部内容,所以这很方便,因为这就是AI的全部内容。在很大程度上它是好的,但它仍然是一种通用的方法。所以你可以获得一定程度的性能和功耗。有些人接下来会转向FPGA,因为您可以比使用GPU更好地定位电路,并且性能和功效都得到提升。 ASIC在功耗和性能方面是极致的,因为您拥有完全自定义的架构,可以完全满足您的需求,不多不少。这显然是最好的。”

人工智能算法很难映射到芯片,因为它们处于几乎不变的状态。所以在这一点上做一个全定制的ASIC不是一种选择,因为它在芯片出厂时已经过期。 “FPGA对此非常好,因为你可以对它们进行重新编程,所以即使花费昂贵的价格,但它不会过时,你的资金也不会打水漂,”Gianfagna说。

这里有一些自定义的内存配置,以及某些子系统功能,例如卷积和转置存储器,这些功能可以再次使用,因此,虽然算法可能会更改,但某些块不会更改 与/或 一次又一次地使用。考虑到这一点,eSilicon正在开发软件分析的功能,以查看AI算法。目标是能够更快速地为特定应用选择最佳架构。

“FGPA 给了您改变机器或引擎的灵活性,因为您可能会遇到一种新的网络,提交一个ASIC是有很大风险的,在这个意义上,您可能没有最好的支持,所以您可以有这样的灵活性,” eSilicon知识产权工程副总裁Deepak Sabharwal说。 “然而,FPGA在容量和性能方面总是受到限制,所以用FPGA无法真正达到产品级规格,最终你将不得不去ASIC。”

嵌入式LUT

过去几年中已经取得了进步的另一个选择是嵌入式FPGA,它将可编程性集成到ASIC中,同时将ASIC的性能和功耗优势添加到FPGA中。

Flex Logix公司首席执行官Geoff Tate表示:“FPGA SoC仍然主要是处理芯片面积相对较小的FPGA。 “在方框图中,比例看起来不一样,但在实际的照片中,主要是FPGA。但是有一类应用和客户,FPGA逻辑和SoC其余部分之间的正确比例是要有一个更小的FPGA,使它们的RTL可编程性成为更具成本效益的芯片尺寸。”

这种方法正在寻找诸如航空航天,无线基站,电信,网络,汽车和视觉处理等领域的牵引力,特别是人工智能。 “算法变化非常快,以至于芯片在他们回来时几乎已经过时,”Tate说。 “有了一些嵌入式FPGA,它可以让他们更快地迭代他们的算法。”

Nijssen说,在这种情况下,可编程性对于避免重新制作整个芯片或模块变得至关重要。

调试设计

与所有SoC一样,了解如何调试这些系统以及构建仪器,可以帮助您在发现问题之前发现问题。

“随着系统FPGA变得更像SoC,他们需要在SoC中期望的开发和调试方法,” UltraSoC首席执行官Rupert Baines说。有一种(也许是天真的)认为,因为你可以在FPGA中看到任何东西,所以很容易调试。这在波形查看器的位级是正确的,但在达到系统级别时并不适用。最新的大型FPGA显然是系统级的。在这一点上,你从位探测器类型排列中获得的波形级视图并不是非常有用。您需要一个逻辑分析仪,一个协议分析仪,以及处理器内核本身的良好调试和跟踪功能。”

FPGA的大小和复杂性要求验证过程类似于ASIC。先进的基于UVM的测试平台支持仿真,通常也由仿真支持。形式工具在这里起着关键的作用,从自动设计检查到基于断言的验证。尽管确实可以比ASIC更快更便宜地改变FPGA,但在大型SoC中检测和诊断错误的难度意味着在进入实验室之前必须进行彻底的验证,OneSpin的Khan说。

事实上,在一个领域中,对FPGA SoC的验证要求可能比在RTL输入和综合后网表之间进行ASIC等效性检查的要求更高。与传统的ASIC逻辑合成流程相比,FPGA的精细化,合成和优化阶段通常对设计进行更多的修改。这些更改可能包括跨越周期边界移动逻辑,并在内存结构中实现寄存器。 Khan补充道,彻底的顺序等价检查对于确保最终的FPGA设计仍然符合RTL中最初的设计者意图至关重要。

在工具方面,还有优化性能的空间。 “有了嵌入式视觉应用程序,其中很多是为Zynq编写的,你可能会得到每秒5帧。但如果你在硬件上加速,你可能会得到每秒25到30帧。这为新型设备铺平了道路。问题是这些设备的模拟和验证并不简单。您需要软件和硬件之间的整合,这很困难。如果你在SoC中运行一切,那太慢了。每次模拟可能需要五到七个小时。如果你合作模拟,你可以节省时间,“Aldec的de Luna说。

简而言之,复杂ASIC中使用的相同类型的方法现在正用于复杂的FPGA。随着这些设备被用于功能安全类型的应用,这变得越来越重要。

“这就是正式分析的目的,以确保有错误的传播路径,然后验证这些路径,”Cadence市场营销总监Adam Sherer说。 “这些东西非常适合正式分析。传统的FPGA验证方法确实使这些类型的验证任务几乎不可能。在FPGA设计中,它仍然非常流行,假设它非常快速且容易地进行硬件测试,该测试以系统速度运行,并且只需进行简单的仿真级别即可进行完整性检查。然后你编程设备,进入实验室并开始运行。这是一条相对较快的路径,但实验室中的可观察性和可控性极其有限。这是因为它只能根据从FPGA内部到引脚的数据进行探测,以便您可以在测试仪上看到它们。”

Breker Verification Systems首席营销官Dave Kelf对此表示赞同。 “这使得这些设备得到验证的方式发生了有趣的转变。过去,通过将设计加载到FPGA本身并在测试卡上实时运行,可以尽可能多地验证较小的器件。随着SoC和软件驱动设计的出现,可以预期这种“自行设计原型”验证方式可能适用于软件驱动技术,并且可能适用于该过程的某些阶段。但是,在原型设计过程中识别问题并对其进行调试非常复杂。这个早期验证阶段需要仿真,因此SoC型FPGA看起来越来越像ASIC。考虑到这个两阶段过程,它们之间的通用性使得该过程更高效,并且包括常见的调试和测试平台。便携式激励等新进展将提供这种通用性,实际上,使SoC FPGA更易于管理。”

结论

展望未来,Sherer表示用户正在寻求将现在在ASIC领域使用的更严格的流程应用到FPGA流程中。

“有很多的培训和分析,他们希望FPGA中有更多的技术用于调试,支持这种水平,” 他说。 “FPGA社区倾向于落后于现有技术,倾向于使用非常传统的方法,因此他们需要在空间,规划和管理以及需求可追溯性方面进行培训和了解。那些来自SoC流程的元素在FPGA中绝对是必需的,并不是FPGA本身驱动它的那么多,但是最终应用中的这些工业标准正在推动它。对于一直在FPGA环境下工作的工程师来说,这是一次重新调整和再教育。”

ASIC和FPGA之间的界限正在模糊,由需要灵活性的应用程序驱动,系统架构将可编程性与硬连线逻辑结合在一起,以及现在正在应用于两者的工具。而且这种趋势不可能很快发生变化,因为许多需要这些组合的新应用领域仍处于起步阶段。

电子发烧友App

电子发烧友App

评论