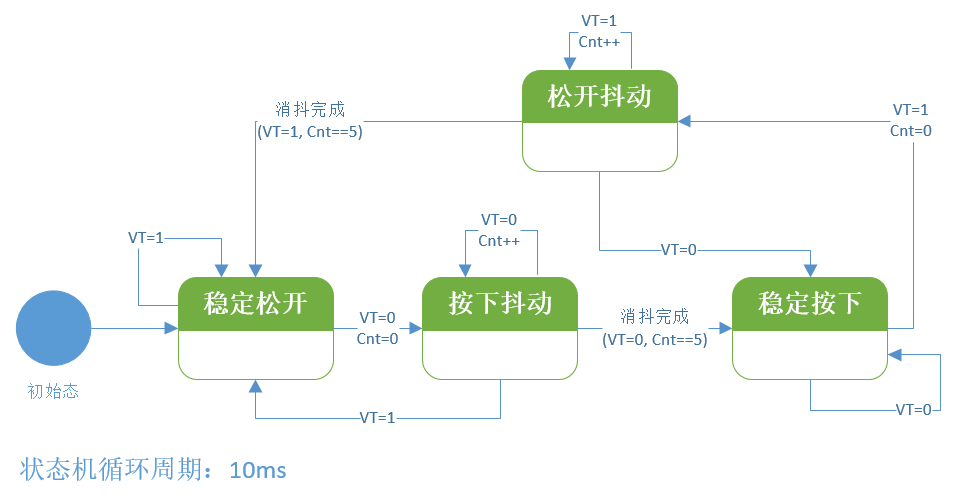

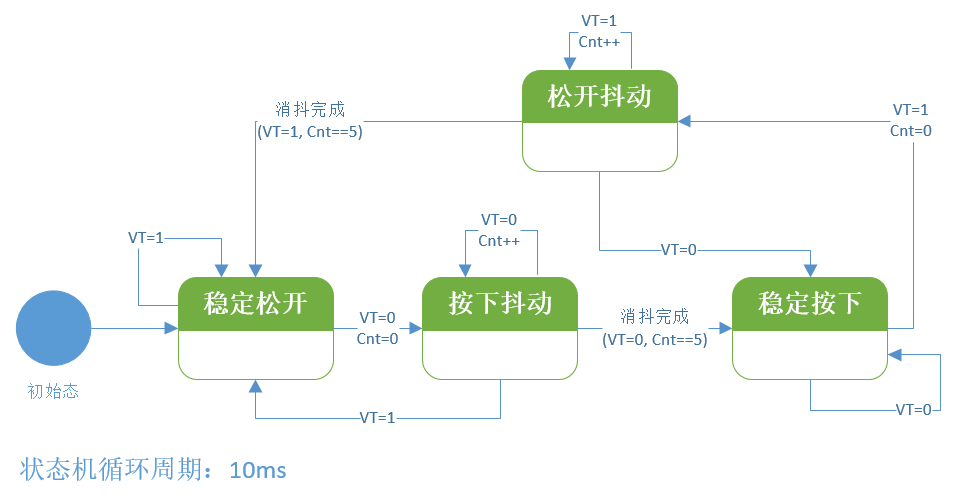

本篇继续介绍状态机的使用,在上篇的基础上,通过简化按键去抖逻辑,并增加按键长按功能,进一步介绍状态图的修改与状态机代码的实现,并通过实际测试,演示状态机的运行效果。

2022-09-03 21:26:52 3277

3277

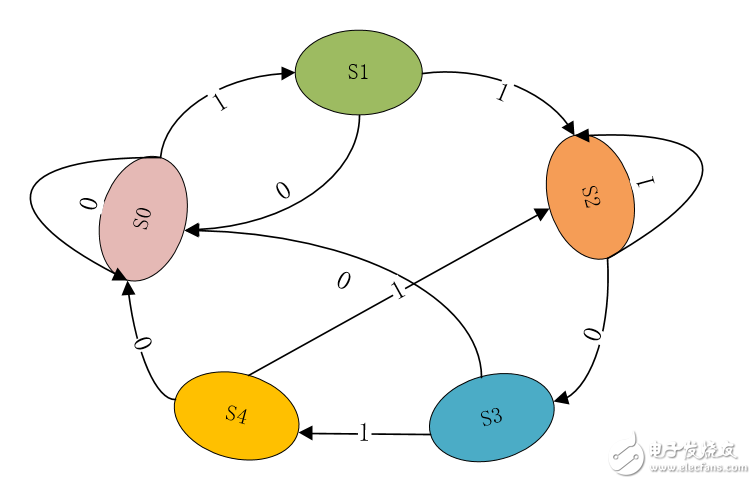

在verilog中状态机的一种很常用的逻辑结构,学习和理解状态机的运行规律能够帮助我们更好地书写代码,同时作为一种思想方法,在别的代码设计中也会有所帮助。 一、简介 在使用过程中我们常说

2024-02-12 19:07:39 1818

1818

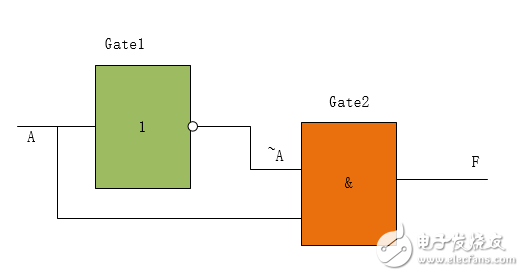

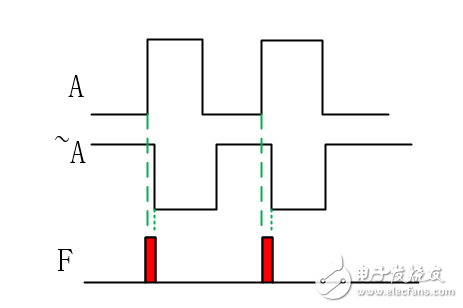

帮助。 产生原因 竞争 :在组合逻辑电路中不同路径的输入信号到达同一个门级电路时,在时间上有先有后,这种先后时间上的差异称之为竞争(Competition) 冒险 :由于竞争的存在,信号在过渡时间瞬间可能产生错误的输出,例如尖峰脉冲。成

2024-02-18 14:34:11 456

456

控制状态机控制状态机的初始化和状态转换的最佳方法是使用枚丽型输入控件。一般使用自定义类型的枚丽变量。使用子定义类型的枚丽变量可以是控件和实例乊间存在关联,使得添加或删除状态时所有的枚丽型输入控件副本自动更新。

2014-02-13 12:39:31

最实用的状态机模板

2017-06-08 15:45:18

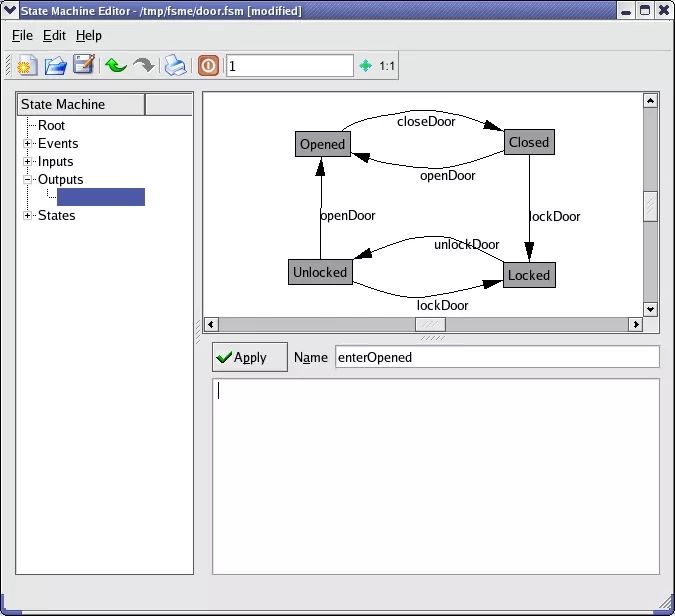

状态机 状态图

2012-08-22 19:45:36

程序一运行 就开始自动运行程序 状态机各种各种状态开始执行 我这里是布尔变量 每一秒点亮一个布尔按钮。我现在想在界面增加一个暂停按钮 当点暂停时候 此时暂停按钮文字成为继续 如果 状态机执行第二步

2018-04-09 09:23:30

刚开始学fpga,读资料,有些名词不太理解,比如状态机,我只知道fpga就是由查找表和触发器构成的,状态机这个概念是怎么提出来的,干什么使得,求大神讲解,什么情况下用到

2013-04-25 18:35:55

状态机可归纳为哪几个要素?状态机可分为哪几种?什么是消息触发类型的状态机?

2021-04-19 06:02:21

以前写状态机,比较常用的方式是用 if-else 或 switch-case,高级的一点是函数指针列表。最近,看了一文章《c语言设计模式–状态模式(状态机)》(来源:embed linux

2022-02-15 06:01:46

自己编写的状态机结构程序

2017-08-14 21:46:43

进行程序设计的基本方法与技巧。一、有限状态机分析设计的基本原理对于电子技术和电子工程类的读者,最先接触和使用到状态机应该是在数字逻辑电路课程里,状态机的思想和分析方法被应用于时序逻辑电路设计。其实

2008-07-10 18:00:24

.smp_rdy_i和rdy_i是来自其他模块的信号,它与状态机处于同一时钟域,但是从寄存器输出后,两个信号传递了一些组合逻辑。通常,关于A,B,C,D的跳跃码如下:来自A-B-C-D的状态,我认为在状态D中

2020-07-08 10:51:29

本帖最后由 inception1900 于 2015-11-16 14:51 编辑

tmp,tmp_num 是std_logic_vector(15 downto 0),tmp输入,tmp_num 输出,如何消除下面VHDL描述组合逻辑出现的竞争(不采用时钟方式)tmp_num(15)

2015-11-16 14:50:26

`对于一个组合逻辑电路,如果有两个输入端,那么只有两个输入端一个从0变1,另一个从1变0是才有可能产生竞争冒险吗,如果开始时两个输入端都是1,那么同时从1变0时会不会产生竞争。例如异或门,开始始输入

2015-12-22 18:49:44

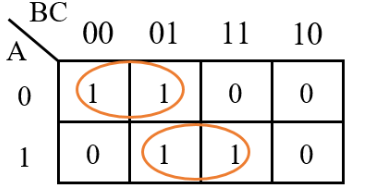

来看看三种方式是如何实现的。 (各种图片,各种坑爹啊 - -!)一段式状态机 当把整个状态机卸载一个always模块中,并且这个模块既包含状态转移,又含有组合逻辑输入/输出时,称为一段式状态机。不

2012-03-09 10:04:18

影响电路工作的可靠性、稳定性,严重时会导致整个数字系统的误动作和逻辑紊乱。下面就来讨论交流一下FPGA 的竞争冒险与毛刺问题。

在数字电路中,常规介绍和解释:

什么是竞争与冒险现象:

在组合电路中

2023-11-02 17:22:20

今天给大侠带来如何写好状态机,状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以很多公司在硬件工程师及逻辑工程师面试中,状态机设计几乎是必选题目。本篇在引入状态机设计思想

2020-09-28 10:29:23

FPGA状态机的文书资料

2014-09-14 19:01:20

FPGA中竞争冒险问题的研究

2012-08-04 16:16:06

竞争冒险:在组合电路中,当逻辑门有两个互补输入信号同时向相反状态变化时,输出端可能产生过渡干扰脉冲的现象,称为竞争冒险。那么 FPGA 产生竞争冒险的原因是什么呢? 信号在 FPGA 器件内部通过

2024-02-21 16:26:56

冒险往往会影响到逻辑电路的稳定性。时钟端口、清零和置位端口对毛刺信号十分敏感,任何一点毛刺都可能会使系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要考虑的问题。如何处理毛刺

2018-08-01 09:53:36

和二进制表示有没有什么影响?3,好的状态机写法是,在状态判断的组合逻辑always块中,最好先定义一个初始化状态,case中最好定义一个默认状态,初始化状态是不是必要,定义为全零好还是不定态“x“好呢。困扰好久了,求解答,谢谢

2014-03-06 19:49:09

摘 要:以现场可编程门阵列(以下简称FPGA)在设计中由于其内部构成,容易引起竞争问题。以我们在实验教学中的应用与实践为主线,详细介绍了消除竞争冒险的各种方法。关键词:现场可编程

2009-04-21 16:44:44

时序电路)。 在组合逻辑电路中,任何时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。这就是组合逻辑电路在逻辑功能上的共同特点。在上一节中,设计的三人表决器就是组合逻辑电路,输出与输入一一对应,和其他

2023-02-21 15:35:38

求LABVIEW状态机与队列的详细资料。

2015-12-12 15:35:01

本帖最后由 afnuaa 于 2017-5-24 11:22 编辑

状态机是一种普遍而有效的架构,我们可以利用状态机设计模式来实现状态图或流程图的算法。State Machines

2017-05-23 17:11:34

执行超时里的东西。一旦VI检测到有更新就会触发用户事件。状态机执行用户事件里的东西。(如图3)用户事件里的东西,我们就是把开始这个全局变量的值改变。当开始的值改变后就能进入逻辑判断的VI了,该VI在处理

2018-12-25 16:53:35

的逻辑时,往往能化繁为简,出奇制胜。由于状态机的特殊编程机制,状态机往往配合事件驱动机制来配合一起使用。raw os巧妙地把状态机编程引进到了空闲任务里,这样的话系统空闲的时候可以进行面向状态机的编程

2013-02-27 14:35:10

波形仿真时verilog 写的状态机被综合掉,编译没有错误,状态转移也没错,什么原因可能导致这种问题呢。

2017-10-05 11:31:26

的RTL视图中可以看出二进制比独热码使用更少的寄存器。 二进制用7个寄存器就可以实现100个状态的状态机,但是独热码就需要100个寄存器。但是另一方面,虽然独热码使用更多的寄存器但是其组合逻辑相对简单

2016-12-26 00:17:38

;(2)二段式:用两个always模块来描述状态机,其中一个always模块采用同步时序描述状态转移;另一个模块采用组合逻辑判断状态转移条件,描述状态转移规律以及输出;(3)三段式:在两个always

2015-05-25 20:33:02

稳定状态所需的时间不同,称为竞争。 逻辑门因输入端的竞争而导致输出产生不应有的尖峰干扰脉冲(又称过渡干扰脉冲)的现象,称为冒险。 在实际电路中,输入信号通过每一个门电路然后输出,它总是要有传输时间

2020-04-24 15:07:49

一. 什么是状态机我们以生活中的小区的停车系统为例:停车杆一般没车的是不动的(初态),有车来的时候需要抬杆(状态1),车通过需要放杆(状态2),如果在放杆的过程中突然有车,又需要抬杆(状态3

2022-01-06 08:01:00

目录1 前言2 状态机2.1 什么是状态机2.2 状态机的概念2.3 使用状态机写键盘的思路3 代码实例3.1 使用软件3.2 protues电路图3.2 状态机部分程序3.3 Keil工程文件

2022-01-24 06:23:02

什么是状态机?状态机是如何编程的?

2021-10-20 07:43:43

文章目录1、什么是状态机?2、状态机编程的优点(1)提高CPU使用效率(2) 逻辑完备性(3)程序结构清晰3、状态机的三种实现方法switch—case 法表格驱动法函数指针法小节摘要:不知道大家

2021-12-22 06:51:58

在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。产生毛刺叫冒险。 如果布尔式中有相反的信号则可能产生竞争和冒险现象。 解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。

2019-08-02 11:57:35

在嵌入式,机器人领域,由于多的复杂逻辑状态,我们编写程序的时候不得不考虑很多种情况,容易造成功能间的冲突。有限状态机(finite-state machine),简称状态机,是一种表示有限个状态以及状态间转移等行为的数学模型。状态机简单来说

2021-12-20 06:51:26

从事逻辑设计的小伙伴对状态机这个词并不陌生,什么两段、三段状态机耳熟能详,摩尔、米利状态机型倒背如流。然而不得不承认的是读别人的RTL代码真的是一件痛苦的事情,那状态机可否更优雅的呈现呢?状态机那些

2022-07-13 14:56:24

的输出与输入直接相关,时序逻辑的输出和原有状态也有关。●组合逻辑立即反应当前输入状态,时序逻辑还必须在时钟上升沿触发后输出新值。●组合逻辑容易出现竞争、冒险现象,时序逻辑一般不会出现。●组合逻辑的时序

2017-11-17 18:47:44

积少成多,集腋成裘,坚持!!!目录1. 进制转换2. 状态机和编码方式3. 存储器的分类4. Verilog语法中的操作符5. 对组合逻辑的认识6. 对时序逻辑的认识7. 竞争冒险的认识8.

2021-07-26 07:14:31

根据CLD的课程写的取款机的逻辑。一边看一边改,从最简单的状态机,到事件驱动,生产者消费者模型,队列状态机,最后到AMC。实现的功能基本相同,但结构各有不同。取款机的逻辑非常简单,前面板也没有美化,只是实现了逻辑。附件提供给大家,希望和大家一起讨论学习。

2017-08-01 16:25:25

状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的功底。

2012-03-12 16:30:24

一篇经典文献,详细讲解了一段、两段、三段式状态机的实现,效率、优缺点。看完后相信会对状态机有一个详细的了解。 状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以许 多公司

2011-10-24 11:43:11

; elseout=0;endendmodule在进行门级仿真的时候波形中出现了毛刺,也就是所谓的竞争冒险,如下图书上也有竞争冒险的解决办法,但具体到代码里还是不会,谁能教教我该怎么改这个代码才能消除竞争冒险?

2011-10-21 14:31:40

在实际的应用中,根据有限状态机是否使用输入信号,设计人员经常将其分为Moore型有限状态机和Mealy型有限状态机两种类型。

2020-04-06 09:00:21

不仅便于阅读、理解、维护,而且利于综合器优化代码,利于用户添加合适的时序约束条件,利于布局布线器实现设计。在两段式描述中,当前状态的输出用组合逻辑实现,可能存在竞争和冒险,产生毛刺。则要求对状态机

2014-09-25 09:35:29

问题。

竞争冒险:在组合电路中,当逻辑门有两个互补输入信号同时向相反状态变化时,输出端可能产生过渡干扰脉冲的现象,称为竞争冒险。

那么 FPGA 产生竞争冒险的原因是什么呢?

信号在

2023-05-30 17:15:28

问个关于状态机的问题,书上说的三段式状态机的第三段,同步时序的状态输出部分的状态到底是当前态还是次态啊?有的书写的是次态,case(next_state),有的写的是case(cur_state)。

2014-09-22 20:42:17

应用LabView做的连接mdb数据库,应用队列状态机

2016-02-05 22:58:25

如何写好状态机:状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以许多公司的硬件和逻辑工程师面试中,状态机设计几乎是必选题目。本章在引入

2009-06-14 19:24:49 96

96 状态机举例

你可以指定状态寄存器和状态机的状态。以下是一个有四种状态的普通状态机。 // These are the symbolic names for states// 定义状态的符号名称parameter [1

2009-03-28 15:18:28 893

893 第二十一讲 组合逻辑电路中的竞争冒险

6.7.1 竞争冒险现象及其产生的原因一、竞争、冒险1.理想情况2.实际情况3.竞

2009-03-30 16:25:35 2728

2728

组合逻辑中的竞争与冒险及毛刺的处理方法 在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。产生毛刺叫冒险。如果布尔式中有相反的信号则可能产生竞争和冒险现象。解决方法:一是添加布尔式的(冗余)消去项,但是不

2011-01-24 18:12:53 0

0 状态机代码生成工具状态机代码生成工具状态机代码生成工具状态机代码生成工具

2015-11-19 15:12:16 9

9 状态机原理及用法状态机原理及用法状态机原理及用法

2016-03-15 15:25:49 0

0 。其只有外部硬件复位采用异步方式,其余信号均用全局时钟进行同步。把状态机逻辑和算术逻辑及数据通道分开,把状态机纯粹当作控制逻辑电路来使用,从而改善其性能。

2016-03-22 16:03:03 12

12 组合逻辑中的竞争与冒险及毛刺的处理方法

2017-01-17 19:54:24 7

7 练习九.利用状态机的嵌套实现层次结构化设计目的:1.运用主状态机与子状态机产生层次化的逻辑设计;

2017-02-11 05:52:50 3126

3126

有限状态机(FSM)是一种常见的电路,由时序电路和组合电路组成。设计有限状态机的第一步是确定采用Moore状态机还是采用Mealy状态机。

2017-02-11 13:51:40 3881

3881

三段式结构中,2个时序always块分别用来描述现态逻辑转移,及输出赋值。组合always块用于描述状态转移的条件。这种结构是寄存器输出,输出无毛刺,而且代码更清晰易读,特别是对于复杂的状态机来说,但是消耗的面积也更多点。这是一种比较流行的状态机结构。

2017-09-16 09:04:54 5

5 寄存器存储状态信息、组合逻辑产生下一个状态和输出值时,大量使用了FPGA的布线、查找表、寄存器等宝贵资源。

为了实现FPGA的可编程性,在其内部使用了大量的可编程逻辑开关。由于可编程逻辑开关

2017-11-17 02:30:07 3184

3184

如何使用QII状态机向导创建一个状态机

2018-06-20 00:11:00 3940

3940

本篇文章包括状态机的基本概述以及通过简单的实例理解状态机

2019-01-02 18:03:31 9928

9928

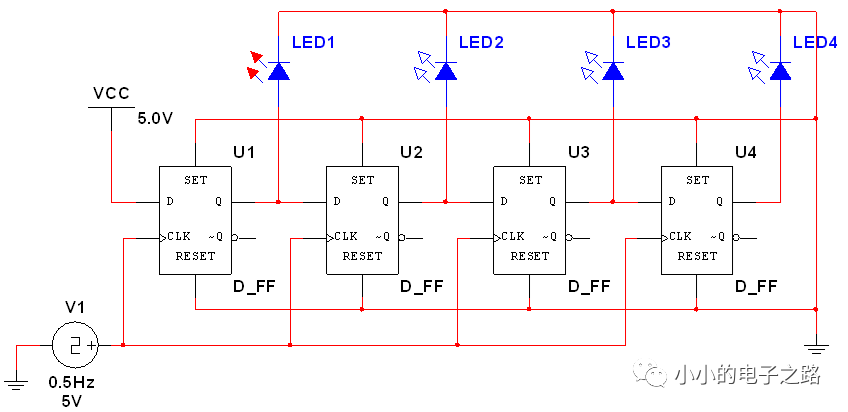

状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作,完成特定操作的控制中心。状态机分为摩尔(Moore)型状态机和米莉(Mealy)型状态机。

2019-09-19 07:00:00 2178

2178

状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作,完成特定操作的控制中心。状态机分为摩尔(Moore)型状态机和米莉(Mealy)型状态机。

2019-10-09 07:07:00 3198

3198 状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心。

2019-10-09 07:06:00 2234

2234 状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心。

2019-12-04 07:03:00 2880

2880

状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心。

2019-10-09 07:02:00 2137

2137 状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作,完成特定操作的控制中心。状态机分为摩尔(Moore)型状态机和米莉(Mealy)型状态机。

2019-05-28 07:03:49 2648

2648 简言之:在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争,竞争产生冒险。

2020-06-26 06:38:00 16665

16665 状态机 1、状态机是许多数字系统的核心部件,是一类重要的时序逻辑电路。通常包括三个部分:一是下一个状态的逻辑电路,二是存储状态机当前状态的时序逻辑电路,三是输出组合逻辑电路。 2、根据状态机的输出

2020-11-16 17:39:00 24811

24811 是FPGA设计中一种非常重要、非常根基的设计思想,堪称FPGA的灵魂,贯穿FPGA设计的始终。 02. 状态机简介 什么是状态机:状态机通过不同的状态迁移来完成特定的逻辑操作(时序操作)状态机是许多数字系统的核心部件, 是一类重要的时序逻辑电路。通常包括三个部分: 下一个

2020-11-05 17:58:47 6145

6145

状态机是逻辑单元、存储器单元和反馈的组合。状态机的输入与状态机的当前状态组合在一起,确定下一个状态。当出现状态时钟时,下一个状态成为当前状态,状态机的输出由当前状态决定。

2021-03-30 15:58:14 7

7 Synplify的优势之一是有限状态机编译器。 这是一个强大的功能,不仅具有自动检测状态机中的状态的能力源代码,并使用顺序编码,灰色编码或一键编码实现它们。但也要进行可达性分析,以确定所有可能的状态达到并优化掉所有无法达到的状态和转换逻辑。因此,产生状态机的高度优化的最终实现。

2021-04-07 09:20:51 12

12 竞争现象的组合电路中,当某个变量发生变化的时候,比如说从 1 跳到 0,或者说从 0 跳到 1,如果真值表所描述的逻辑关系或者功能遭受到短暂的破坏,在输出端出现一个不应有的尖脉冲 毛刺,这种现象就叫 冒险。 冒险是由竞争造成的,

2021-06-13 16:56:00 15806

15806 “本文主要分享了在Verilog设计过程中状态机的一些设计方法。 关于状态机 状态机本质是对具有逻辑顺序或时序顺序事件的一种描述方法,也就是说具有逻辑顺序和时序规律的事情都适用状态机描述。状态机

2021-06-25 11:04:43 2249

2249 玩单片机还可以,各个外设也都会驱动,但是如果让你完整的写一套代码时,却无逻辑与框架可言。这说明编程还处于比较低的水平,你需要学会一种好的编程框架或者一种编程思想!比如模块化编程、状态机编程、分层思想

2021-07-27 11:23:22 19223

19223

1. 前言 在数字电路课程中,老师在讲组合逻辑的时候,一般都会讲竞争与冒险。sky当时也听的云里雾里,没有想清楚如下问题: 1) 竞争与冒险究竟是什么东西?有啥物理现象? 2) 在数

2021-08-09 14:43:08 2657

2657

以前写状态机,比较常用的方式是用 if-else 或 switch-case,高级的一点是函数指针列表。最近,看了一文章《c语言设计模式–状态模式(状态机)》(来源:embed linux

2021-12-16 16:53:04 7

7 今天还是更新状态机,状态机基本是整个HDL中的核心,合理、高效地使用状态机,是数字电路中的重要技能。

2023-02-12 10:21:05 542

542 有限状态机是由寄存器组和组合逻辑构成的硬件时序电路,其状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态,究竟转向哪一状态还是留在原状态不但取决于各个输入值,还取决于当前所在状态。这里是指Mealy型有限状态机。

2023-04-07 09:52:46 909

909 和序列要求的最佳方法则是使用状态机。状态机是在数量有限的状态之间进行转换的逻辑结构。一个状态机在某个特定的时间点只处于一种状态。但在一系列触发器的触发下,将在不同状态间进行转换。理论上讲,状态机可以分为Moore 状态机和Mealy 状态机

2023-07-18 16:05:01 499

499

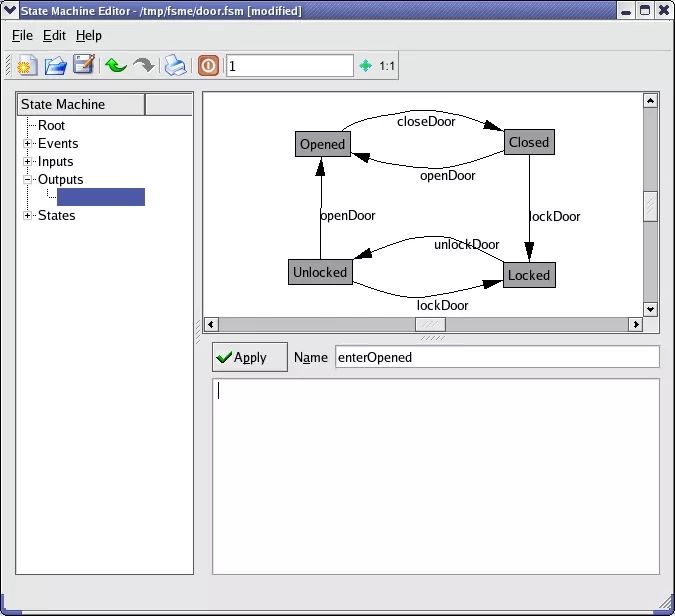

本身相关的那些处理逻辑。在FSME中,与具体应用相关的操作称为输出(Output),它们实际上就是一些需要用户给出具体实现的虚函数,自动生成的状态机引擎负责在进入或者退出某个状态时调用它们。 仍然以控制城门的那个状态机为例

2023-09-13 16:57:37 821

821

门电路的两个输入信号同时向相反的逻辑电平跳变的现象叫做 竞争 ,这种竞争可能在电路的输出端产生尖峰脉冲,这种现象称为 竞争冒险 。

2023-09-25 11:50:45 1080

1080

状态机,又称有限状态机(Finite State Machine,FSM)或米利状态机(Mealy Machine),是一种描述系统状态变化的模型。在芯片设计中,状态机被广泛应用于各种场景,如CPU指令集、内存控制器、总线控制器等。

2023-10-19 10:27:55 3405

3405

正在加载...

电子发烧友App

电子发烧友App

评论