Reconfigurable Cell Array)结构测试FPGA逻辑单元PLB(Programmable Logic Block)的方法,该方法对逻辑单元PLB 进行了分类、分阶段的测试,同时进行电路模拟实验。

2018-11-28 09:02:00 4021

4021

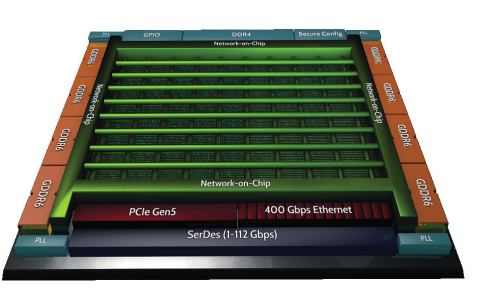

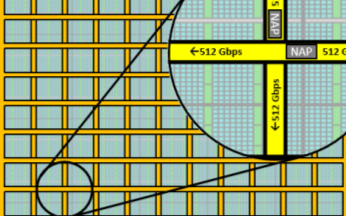

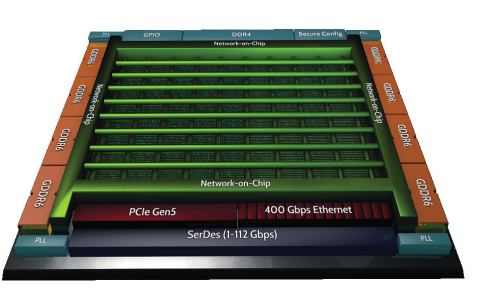

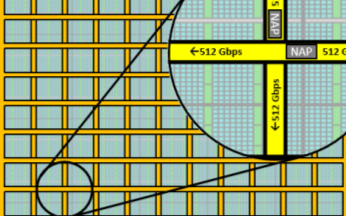

Achronix 最新基于台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器件包含了革命性的新型二维片上网络(2D NoC)。

2020-02-27 17:08:41 1774

1774 本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。 下面详细介绍第一部

2020-12-20 11:39:59 35579

35579

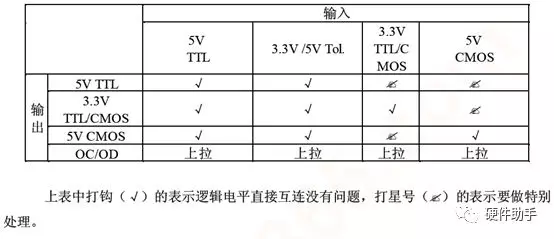

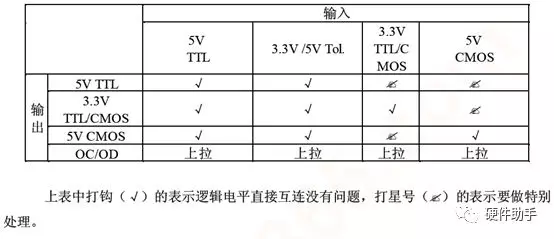

本篇主要介绍TTL/CMOS电平的互连、OC/OD的互连,其余单端逻辑电平的互连可参考相关器件规范、电平规范。 1、TTL/CMOS互连 常用的TTL和CMOS电平主要是5V TTL、5V CMOS

2020-12-23 14:15:12 5648

5648

只有在脑海中建立了一个个逻辑模型,理解FPGA内部逻辑结构实现的基础,才能明白为什么写Verilog和写C整体思路是不一样的,才能理解顺序执行语言和并行执行语言的设计方法上的差异。在看到一段简单程序的时候应该想到是什么样的功能电路。

2022-08-25 11:12:00 739

739 在FPGA设计中经常使用到逻辑复制,逻辑复制也用在很多场合。

2022-09-29 09:17:53 782

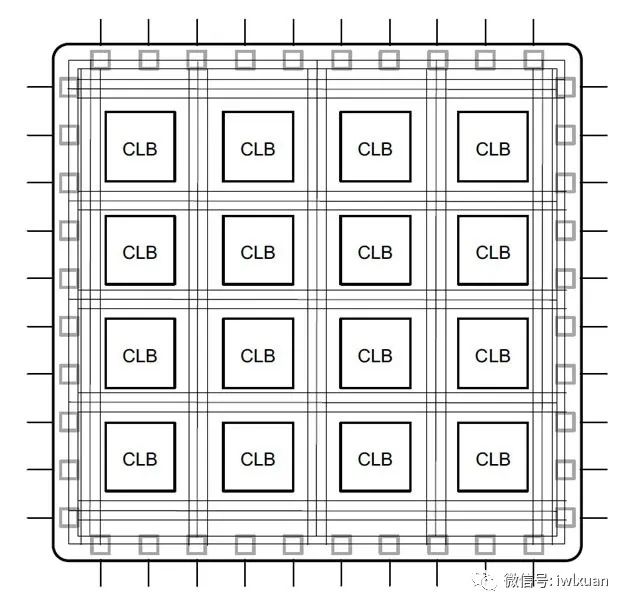

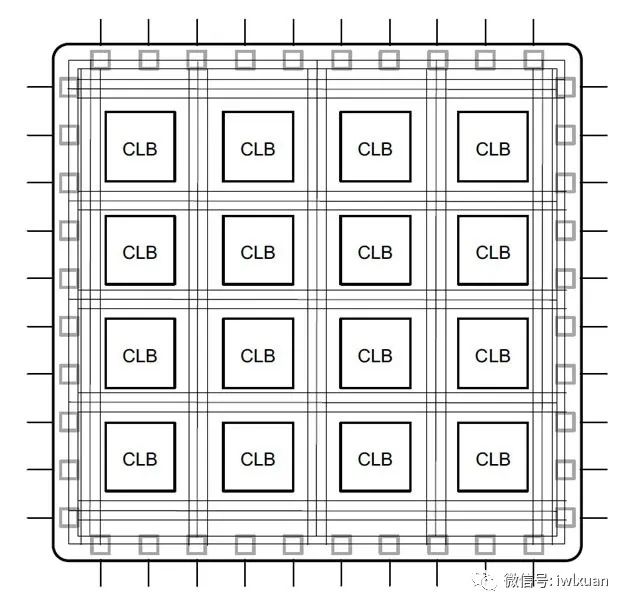

782 以Xilinx主流的7系列为例,一颗FPGA内部通常都会有数千到数十万不等的可配置逻辑块(Configurable Logic Block,简称CLB)

2023-08-15 16:09:50 509

509

逻辑单元在FPGA器件内部,用于完成用户逻辑的最小单元。

2023-10-31 11:12:12 541

541

2D NoC如同在FPGA可编程逻辑结构上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽。

2021-11-11 14:20:14 2760

2760

FPGA 内部详细架构FPGA 芯片整体架构1.可编程输入输出单元(IOB)(Input Output Block)2.可配置逻辑块(CLB)(Configurable Logic Block)3.

2021-07-30 08:10:06

,口线必定复杂而且速度有限。FPGA无需考虑这个问题,由于其内部逻辑可由设计者来设计,那么编程器可根据接口需要来定制对应的逻辑,省时省力,效率非常高。在设计过程中灵活使用FPGA这个“千手观音”,让编程器功能更灵活、更高效。

2015-10-27 15:45:15

本文采用FPGA和ARM结合设计,很好地完成了多通道高精度的数据采集与处理,并且还详细介绍了FPGA逻辑的设计方法。

2021-05-06 06:21:48

排列于芯片四周;可编程内部互连包括各种长度的连线线段和一些可编程连接开关,它们将各个可编程逻辑块或I/O块连接起来,FPGA在可编程逻辑块的规模,内部互连线的结构和采用的可编程元件上存在较大的差异.较

2020-08-28 15:41:47

的相互连接。实际情况还真不是这么简单,FPGA/CPLD里面其实也找不着多少个与门、或门、非门。那么FPGA/CPLD器件内部到底以怎样的方式来实现我们需要的逻辑电路呢?下面我们就通过剖析MAX II

2015-01-27 11:43:10

FPGA小白一枚,个人理解的FPGA本质上或者核心就是查找表(LUT),即将所有的函数/方法 转换为固定的查找表(使用DSP除外)。但是为什么所有的文章提到FPGA全部都注重逻辑门呢?其实FPGA本身内部也没有多少物理的逻辑门吧?

2019-05-30 10:53:46

的板级调试方法有很多,借助于常规的示波器和逻辑分析仪的调试方法是最典型的手段。如图10.1所示,基于传统的台式示波器或逻辑分析仪进行板级调试有着诸多的不便,相对于设计电路深藏在芯片内部的FPGA

2015-09-02 18:39:49

。(特权同学版权所有)我们都知道,硬件有着与生俱来的并行特点,它不同于软件编程的顺序特性。在FPGA器件内部,所有的硬件逻辑都可以同时工作运行,正是这样,很多需要多条软件程序指令实现的功能,用硬件逻辑

2015-03-26 11:00:19

FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种特殊的集成电路,其内部结构由大量的可配置逻辑块和互连线组成。FPGA可以通过编程来实现各种数字系统功能

2024-01-26 10:03:55

`FPGA是当前很热门的技术。发展到现在,FPGA器件由早期的纯逻辑粘合发展到如今的可编程片上系统(SOC),FPGA应用的领域愈发广泛,开发难度和复杂度也越来越大。有很多工程师都在探索FPGA技术

2017-01-11 13:58:34

的大小等。 2.基本可编程逻辑单元 FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟

2019-09-24 11:54:53

的大小等。 2.基本可编程逻辑单元 FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟

2016-07-16 15:32:39

的大小等。 2.基本可编程逻辑单元 FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟

2016-08-23 10:33:54

的大小等。 2.基本可编程逻辑单元 FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟

2016-09-18 11:15:11

的大小等。 2.基本可编程逻辑单元 FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟

2016-10-08 14:43:50

的逻辑功能创造了条件。PLD使用SRAM单元来保存配置数据。这些配置数据决定了PLD内部的互连关系和逻辑功能,改变这些数据,也就改变了器件的逻辑功能。下面我们介绍两种常用的PLD器件:CPLD和FPGA

2023-02-23 15:24:55

,加密只支持整FPGA的配置3.256bit密钥加密,fpga内部包含解码逻辑(不能其它用途)4.如烧写过密钥ram,efuse后,芯片可以正常烧写其它未加密的bitstream。5.如用bpi X16

2013-01-01 20:44:47

在超高速数据采集方面,FPGA(现场可编程门阵列)有着单片机和DSP所无法比拟的优势。FPGA时钟频率高,内部时延小,目前器件的最高工作频率可达300MHz;硬件资源丰富,单片集成的可用门数达1000万门;全部控制逻辑由硬件资源完成,速度快,效率高;组成形式灵活,可以集成外围控制、译码和接口电路。

2019-08-02 06:51:33

;可编程内部互连包括各种长度的连线线段和一些可编程连接开关,它们将各个可编程逻辑块或I/O块连接起来,构成特定功能的电路。不同厂家生产的FPGA在可编程逻辑块的规模,内部互连线的结构和采用的可编程元件上存在

2009-09-29 09:38:32

DSP的并行互连方法有哪些,其各自的优缺点是什么?如何利用TMS320C6x的HPI组成多DSP互联并行系统?如何利用ADSP2106x的Link口组成多DSP互连并行系统?

2021-04-08 06:41:13

涉及器件安装方法、布线的隔离以及减少引线电感的措施等等。 目前有迹象表明,印刷电路板设计的频率越来越高。随着数据速率的不断增,数据传送所要求的带宽也促使信号频率上限达到1GHz,甚至更高。种高频

2018-11-26 10:54:27

大家好!我想将Pandaboard与FPGA互连。在互联网上搜索我发现可以使用GPMC互连它们,但遗憾的是我没有找到任何关于USB的信息。我的问题是:是否可以通过USB互连两块板?如果是的话,必须执行哪些操作才能连接这两个板,以便它们能够彼此“交谈”?预先感谢。利玛窦。

2019-09-04 09:39:40

安装方法、布线的隔离以及减少引线电感的措施等等。 目前有迹象表明,印刷电路板设计的频率越来越高。随着数据速率的不断增长,数据传送所要求的带宽也促使信号频率上限达到1GHz,甚至更高。这种高频信号技术

2010-02-04 12:21:46

⑴ 结合Xilinx、Altera 等公司的FPGA 芯片,简要罗列一下FPGA 内部的资源或专用模块,并简要说明这些资源的一些作用或用途。(至少列出5 项,越多越好)⑵ 如果,对内部特定资源,曾有

2012-03-08 11:03:49

连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能

2019-08-11 04:30:00

互连 等。1)自由空间光互连技术通过在自由空间中传播的光束进行数据传输,适用于芯片之间或电路板之间这个层次上的连接,可以使互连密度接近光的衍射极限,不存在信道对带宽的限制,易于实现重构互连。该项技术

2016-01-29 09:17:10

,不存在信道对带宽的限制,易于实现重构互连,适用于芯片间和之间层次上的互连,不过,自由空间光互连的对准问题有待解决问题。

2019-10-17 09:12:41

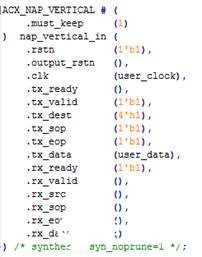

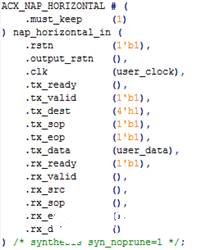

NoC 如同在 FPGA 可编程逻辑结构之上运行的高速公路网络一样,为 FPGA 外部高速接口和内部可编程逻辑的数据传输提供了大约高达 27Tbps 的超高带宽。作为 Speedster7t FPGA

2020-09-07 15:25:33

设计。FPGA是另一类可编程逻辑器件,在结构上与CPLD有很大的差别,电路设计不受与-或阵列结构的两级组合逻辑限制。芯片内部主要由许多可编程逻辑模块组成,靠纵横交错的分布式可编程互联线连接起来,可构成极其

2021-07-13 08:00:00

FPGA内部的LUT和触发器等效出来的电路。 数字逻辑电路分为组合逻辑电路和时序逻辑电路。时序逻辑电路是由组合逻辑电路和时序逻辑器件构成(触发器),即数字逻辑电路是由组合逻辑和时序逻辑器件构成。所以

2023-03-06 16:31:59

基于FPGA的超高速FFT硬件实现介绍了频域抽取基二快速傅里叶运算的基本原理;讨论了基于FPGA达4 096点的大点数超高速FFT硬件系统设计与实现方法,当多组大点数进行FFT运算时,利用FPGA

2009-06-14 00:19:55

基于FPGA的通用高速串行互连协议设计基于FPGA的通用高速串行互连协议设计

2012-08-11 15:46:52

占用1个FIFO,高32bit的数据位宽则会闲置。由此可见,MPFE在使用上十分灵活,能够适应不同的应用方式,满足FPGA内部不同逻辑模块对Memory的读写访问。3 多端口前端的调度策略MPFE本身

2019-06-13 05:00:06

1149.1(即JTAG协议)制定边界扫描方法的检测逻辑结构,是用边界扫描单元组成的边界扫描链,每个单元介于外部管脚与内部逻辑之间,并且是串行连接的,由TAP(检测口控制器)来控制数据链在边界扫描链中

2011-09-23 11:44:40

资源组成的可编程逻辑,用于实现高密度逻辑,被称为现场可编程门阵列(FPGA)。FPGA也称为可编程ASIC,由可配置逻辑块(CLB)、IO块(IOB)和可编程互连组成。现代FPGA甚至包括乘法器

2022-10-27 16:43:59

时序分析是FPGA设计的必备技能之一,特别是对于高速逻辑设计更需要时序分析,经过基础的FPGA是基于时序的逻辑器件,每一个时钟周期对于FPGA内部的寄存器都有特殊的意义,不同的时钟周期执行不同的操作

2017-02-26 09:42:48

NoC为FPGA设计提供了哪些优势?NoC在FPGA内部逻辑互连中发挥的作用是什么?如何利用片上高速网络创新地实现FPGA内部超高带宽逻辑互连?

2021-06-17 11:35:28

一定难度。而且要更改FPGA内部的逻辑也不是十分灵活。本文探讨一种在嵌入式系统中,灵活,方便地动态配置FPGA 的方法。 具有FPGA 设计能力的硬件工程师可以设计各种F...

2021-12-21 06:13:49

推动FPGA调试技术改变的原因是什么外部逻辑分析仪受到的限制是什么如何用内部逻辑分析仪调试FPGA

2021-04-30 06:44:08

cc1101占用带宽超高 "占用带宽有问题,测试结果为726KHz,要求不能大于250KHz(主频为868.25Mhz).测试结果为726KHz, 收窄为500KHz以内即可。"修改哪个参数?或者参考哪个设计文件?

2019-09-16 13:12:49

分布时钟和其他信号。图6: 用于 FPGA 器件的直接互连技术截面图输入/输出块(IOBs)在封装引脚和设备内部逻辑之间提供可编程的单向或双向接口。在一个 IOB 中存在三个信号: 输入路径将数据从输入

2022-04-03 11:20:18

运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽(~27Tbps)。图1Speedster 7t FPGA结构图NoC使用一系列高速的行和列网络通路在整个FPGA

2020-05-12 08:00:00

要使用哪种方法去验证 FPGA 的逻辑设计?FPGA的优缺点是什么?

2021-04-08 06:57:32

调试FPGA时,TD软件是否支持内部逻辑分析(抓波形)功能?

2023-08-11 10:32:27

技巧,内容涉及器件安装方法、布线的隔离以及减少引线电感的措施等等。 目前有迹象表明,印刷电路板设计的频率越来越高。随着数据速率的不断增长,数据传送所要求的带宽也促使信号频率上限达到1GHz,甚至更高

2018-09-13 15:53:21

Altera力守FPGA江山3、基于DSP和FPGA汽车防撞报警设备高级数据采集4、基于FPGA的车牌号定位与识别系统5、全面优化FPGA能耗:FPGA电源分析6、高带宽 + 联网当道,谁来狙击FPGA双雄?可编程逻辑器件特刊免费下载 `

2013-05-07 15:05:03

一种基于FPGA技术的虚拟逻辑分析仪的研究与实现:逻辑分析仪的现状" 发展趋势及研制虚拟逻辑分析仪的必要性, 论述了基于FPGA技术的虚拟逻辑分析仪的设计方案及具体实现方法,介绍

2008-11-27 13:13:04 29

29 Xilinx®7系列FPGA由四个FPGA系列组成,可满足各种系统要求,从低成本、小尺寸、成本敏感的高容量应用到超高端连接带宽、逻辑容量和信号处理能力,以满足最苛刻的高性能应用

2022-08-30 17:04:09

介绍了频域抽取基二快速傅里叶运算的基本原理;讨论了基于FPGA达4 096点的大点数超高速FFT硬件系统设计与实现方法,当多组大点数进行FFT运算时,利用FPGA内部大容量存储资源,采

2009-04-26 18:33:08 26

26 Xilinx®7系列FPGA包括四个FPGA系列,可满足整个系统要求,包括低成本,小尺寸,成本敏感的大批量应用程序,可满足最苛刻的超高端连接带宽,逻辑容量和信号处理能力高性能的应用程序。7系列

2022-11-10 15:11:11

针对FPGA 中包含三级可编程开关的互连网络测试,该文提出了一种基于匹配理论的减少配置次数并且与阵列规模无关的测试方法。该方法通过建立结构测试图,按照图的道路长进行分

2009-11-17 12:43:40 10

10 介绍了一种基于FPGA 的超高速数据采集与处理系统,给出了系统实现的方案,并详细阐述了各硬件电路的具体构成。对系统软件功能做了简要介绍,并利用嵌入式逻辑分析仪对该超高

2010-01-20 16:03:27 58

58 随着FPGA设计复杂度的增加,传统测试方法受到限制。在高速集成FPGA测试中,其内部信号的实时获取和分析比较困难。介绍了Quartus II中SingalTap II嵌入式逻辑分析器的使用,并给出一个

2010-12-17 15:25:17 16

16 内部电源用于逻辑器件内部节点的偏置和转换。内部功率包括静态功耗和动态功耗。

静态内部功耗的定义是在无负载连接、输入端处于随

2010-05-31 17:53:37 838

838

基于FPGA的通用高速串行互连协议设计。

2016-05-11 09:46:01 18

18 Virtex® UltraScale+™ FPGA VCU118 评估套件采用可在 FinFET 节点提供最高性能及各种集成功能的 Virtex UltraScale+ FPGA,是加速超高带宽应用的理想开发环境。

2017-01-13 12:52:11 2832

2832 FPGA内部的RAM M9K

2017-04-07 11:40:04 4

4 由于同步动态随机存储器SDRAM内部结构原因导致其控制逻辑比较复杂。现场可编程逻辑门阵列FPGA作为一种半定制电路具有速度快、内部资源丰富、可重构等优点。本文设计了一种基于FPGA的SDRAM

2017-11-18 12:42:03 2054

2054

从19到32Gb / s的互连宽度正在迅速扩大。

了解Xilinx UltraScale +™FPGA和MPSoC如何直接使用这些互连,以及KCU116和VCU118评估套件如何快速启动您的设计。

2018-11-22 07:21:00 2875

2875 Xilinx 7系列FPGA包括四个可满足全系列系统需求的FPGA系列,从低成本、小尺寸、成本敏感、大容量应用到超高端连接带宽、逻辑容量和信号处理能力,满足最苛刻的高性能应用。7系列FPGA包括:

2019-02-25 16:43:37 81

81 本文档的主要内容详细介绍的是FPGA教程之FPGA系统设计的主要思路和方法初探资料说明包括了:1.FPGA的适用领域及选型FPGA系统设计典型流程,2.FPGA逻辑设计方法 弓|入ASIC的设计方法,3.FPGA设计的常用技巧,4.FPGA系统设计中的对与错

2019-04-04 17:19:58 53

53 本文档的详细介绍的是FPGA设计有哪些良好的设计方法及误区内容包括了:1.FPGA的适用领域及选型,2.FPGA系统设计典型流程,3.FPGA逻辑设计良好设计方法一引入ASIC的设计方法,4.FPGA设计的常用技巧,5.FPGA系统设计中的误区

2019-04-18 17:30:04 23

23 FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

2019-12-02 07:05:00 1522

1522

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-03 07:04:00 2191

2191

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

2019-06-27 17:52:56 25584

25584 Achronix 最新基于台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器件包含了革命性的新型二维片上网络(2D NoC)。

2020-05-04 09:43:00 593

593 Achronix 最新基于台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器件包含了革命性的新型二维片上网络(2D NoC)。

2020-05-28 10:27:12 527

527

进行硬件设计的功能调试时,FPGA的再编程能力是关键的优点。CPLD和FPGA早期使用时,如果发现设计不能正常工作,工程师就使用“调试钩”的方法。先将要观察的FPGA内部信号引到引脚,然后用外部的逻辑分析仪捕获数据。

2020-09-14 15:08:00 527

527

通用FPGA架构由三种类型的模块组成。它们是I / O块或焊盘,开关矩阵/互连线和可配置逻辑块(CLB)。基本FPGA架构具有二维逻辑块阵列,其具有用于用户安排逻辑块之间的互连的装置。下面讨论FPGA架构模块的功能:

2020-09-30 14:00:33 7542

7542 本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。

2021-01-07 16:30:00 36

36 本篇主要介绍逻辑互连中的一些具有特殊功能的互连。这些特殊功能包括总线保持、串联阻尼电阻、热插拔等。

2021-01-07 16:30:00 22

22 逻辑互连之AC耦合电容综述

2021-09-10 15:08:31 4

4 FPGA CPLD可编程逻辑器件的在系统配置方法(深圳市村田电源技术有限公司)-FPGA CPLD可编程逻辑器件的在系统配置方法

2021-09-18 10:51:20 13

13 逻辑单元(Logic Element,LE)在FPGA器件内部,用于完成用户逻辑的最小单元。一个逻辑阵列包含16个逻辑单元以及一些其他资源, 在一个逻辑阵列内部的16个逻辑单元有更为紧密的联系,可以实现特有的功能。

2022-06-15 16:50:21 2604

2604 Achronix Speedster7t FPGA除了在外围Hard IP上都采用目前业内领先的大带宽高速率IP,在内部的可编程逻辑的架构中也做了大量的优化去进一步提高内部可编程逻辑的性能,从而适配

2022-07-05 15:37:41 925

925 成本、小尺寸、成本敏感的高容量应用到超高端连接带宽、逻辑容量和信号处理能力,以满足最苛刻的高性能应用,以及其它系列运用不同领域。

2022-11-03 14:39:54 1446

1446 铜的替代品,如钌和钼,可以集成使用双镶嵌。不过,它们可能更适合使用金属蚀刻的减法方案,自从铝互连的日子以来,金属蚀刻还没有在逻辑中广泛使用。

2023-02-17 11:04:11 1094

1094 FPGA设计的五个主要任务:逻辑综合、门级映射、整体功能逻辑布局、逻辑资源互连布线,最后生成FPGA的bit流

2023-04-06 09:39:45 691

691 FPGA设计的五个主要任务:逻辑综合、门级映射、整体功能逻辑布局、逻辑资源互连布线

2023-05-23 15:25:21 455

455

电子发烧友网站提供《Xilinx FPGA和SoC的超高速设计方法指南.pdf》资料免费下载

2023-09-14 09:41:06 0

0 可以商用的集成全域硬2D NoC的FPGA器件,以每通道512Gbps的速率和超过2Tbps的总带宽来与所有系统接口和FPGA逻辑阵列互连。

2023-11-24 16:19:45 185

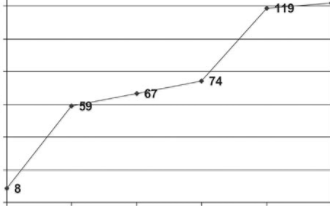

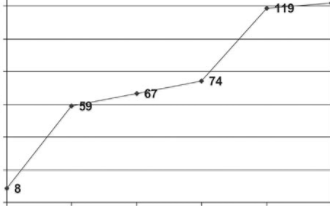

185 的FPGA内部信号引到引脚,然后用外部的逻辑分析仪捕获数据。然而当设计的复杂程度增加时,这个方法就不再适合了,其中有几个原因。第一是由于FPGA的功能增加了,而器件的引脚数目却缓慢地增长。因此,可用逻辑对I/O的比率减小了,参见图1。此外,设计很复杂时

2023-12-20 13:35:01 147

147

CPLD和FPGA都是由逻辑阵列模块构成的,但是CPLD的LAB基于乘积和宏单元,而FPGA的LAB使用基于LUT的逻辑单元。CPLD的LAB围绕中心全局互连排列,随着器件中逻辑数量的增加,呈指数

2024-01-23 09:17:04 280

280

正在加载...

电子发烧友App

电子发烧友App

评论