电子发烧友网核心提示: 根据ALTERA官方FAE(现场应用工程师)的强烈建议,请注意不要随意带电插拔JTAG下载接口,否则会损坏FPGA芯片的JTAG口信号管脚。 现象: 在排除了下载线的问题

2012-09-05 09:00:42 12784

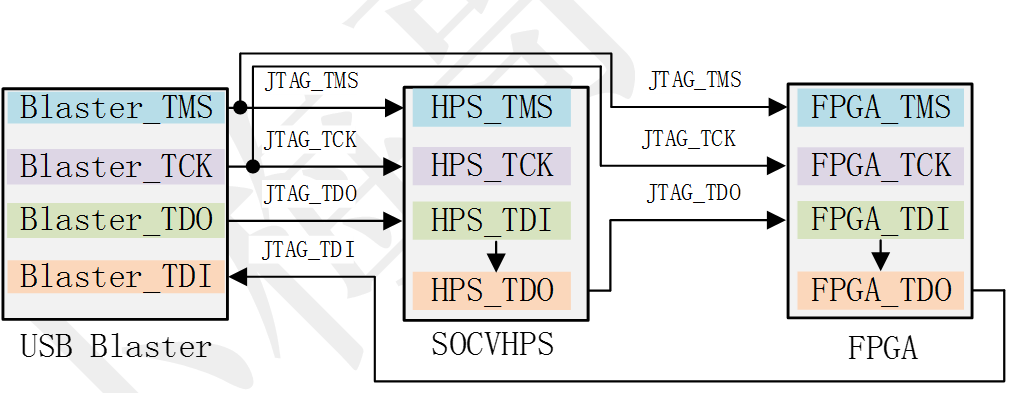

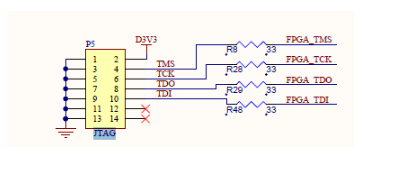

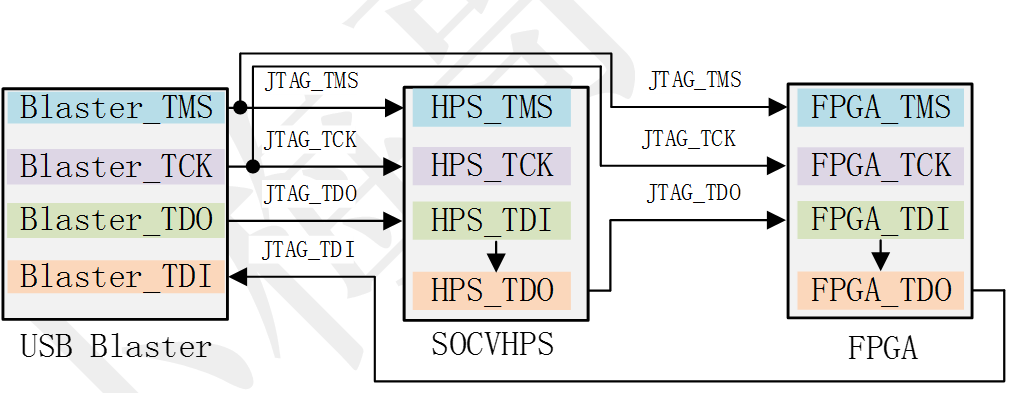

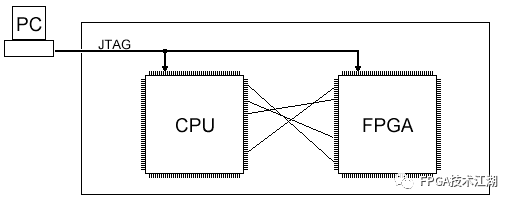

12784 SoC FPGA作为在同一芯片上同时集成了FPGA和HPS的芯片,其JTAG下载和调试电路相较于单独的FPGA或ARM处理器都有一些差异,但是同时两者又有紧密的联系。

2020-08-08 10:08:00 1633

1633

FPGA的管脚主要包括:用户I/O(UserI/O)、配置管脚、电源、时钟及特殊应用管脚等。其中有些管脚可有多种用途,所以在设计FPGA电路之前,需要认真的阅读相应

2019-09-18 07:34:49

=FLASE绕过PAR的检查,这样就只是将本该接入专用时钟管脚(或者叫做全局时钟管脚)的信号,接到了普通IO口上,但并没有做好如何用普通IO口来引入全局时钟,Xilinx官方论坛上更是有老外直接指出这只

2019-07-09 08:00:00

Buffer,支持施密特触发器的磁滞功能。20/26. nCONFIG专用的输入管脚。这个管脚是一个配置控制输入脚。如果这个脚在用户模式下被置低,FPGA就会丢失掉它的配置数据,并进入一个复位状态,并将所有

2014-12-29 11:46:33

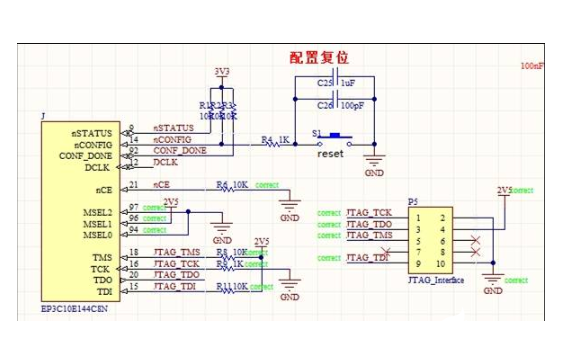

举例——altera FPGA配置全过程一个器件完整的配置过程将经历复位、配置和初始化等3个过程。FPGA正常上电后,当其nCONFIG管脚被拉低时,器件处于复位状态,这时所有的配置RAM内容被清空

2017-11-22 09:35:19

手上有一块黑金AX309的板子,Jtag口的排针间距是2.0mm,而我zturn]按道理现在板子高级了,应该都会有保护电路的吧,但是还是要谨慎啊。

2020-04-25 07:00:00

现象: 在排除了下载线的问题后,还是不能访问FPGA的JTAG口,那么很有可能你的FPGA芯片的JTAG口已经损坏。此时请用万用表检查TCK,TMS,TDO和Tdi是否和GND短路,如果任何一个信号对地短路则表示JTAG信号管脚已经损坏。

2019-05-31 07:01:06

FPGA的JTAG接口和ARM的JTAG接口线是否可以共用同一线呢?是否可以用同usb转JTAG线给ARM和FPGA以及dsp调试程序呢?

2022-08-10 14:54:43

今天下载时,下载一直失败,经测量后发现JTAG的TDI引脚与地短路了,请问这能说明是FPGA芯片内部的JTAG接口坏了吗?还是有肯能是别的问题?有谁遇见过没?

2013-04-05 22:49:11

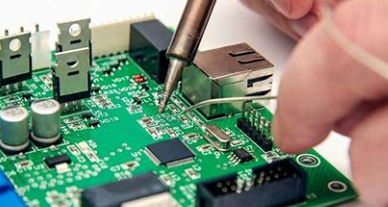

电源部分。使用万用表进行测试,排除电源短路等情况后,上电测量电压是否正确。(2)然后焊接FPGA及相关的下载电路。再次测量电源地之间是否有短路现象,上电测试电压是否正确,然后将手排除静电后触摸FPGA

2012-08-12 11:52:54

JTAG口如何配置?怎么使用?

2021-10-29 07:22:26

使用闻亭XDS560V2仿真器,自己做的F***板子,JTAG口经常烧掉,JTAG电路如图,请问是什么原因,用着用着TRST就和地短路了,已经烧了三个芯片了

2020-05-11 09:52:32

我设计的是FPGA的板子,用JTAG烧写。直接烧FPGA是没有问题的,但是烧ROM就会出错,IDCODE=ff检验不通过。网上有人说是JTAG的电平不够。求问是不是布线的时候JTAG口距离FPGA一定要近一些,线短一些才行?

2013-07-26 15:29:20

“DONE没有变高”,而当我拿出芯片内核或来自内核的一些信号时,编程成功但之后我的JTAG停止工作。如果我尝试在iMPACT中初始化JTAG链,它会询问我是否有此设备的BSDL或BIT文件,或者如果我尝试

2018-10-08 11:19:37

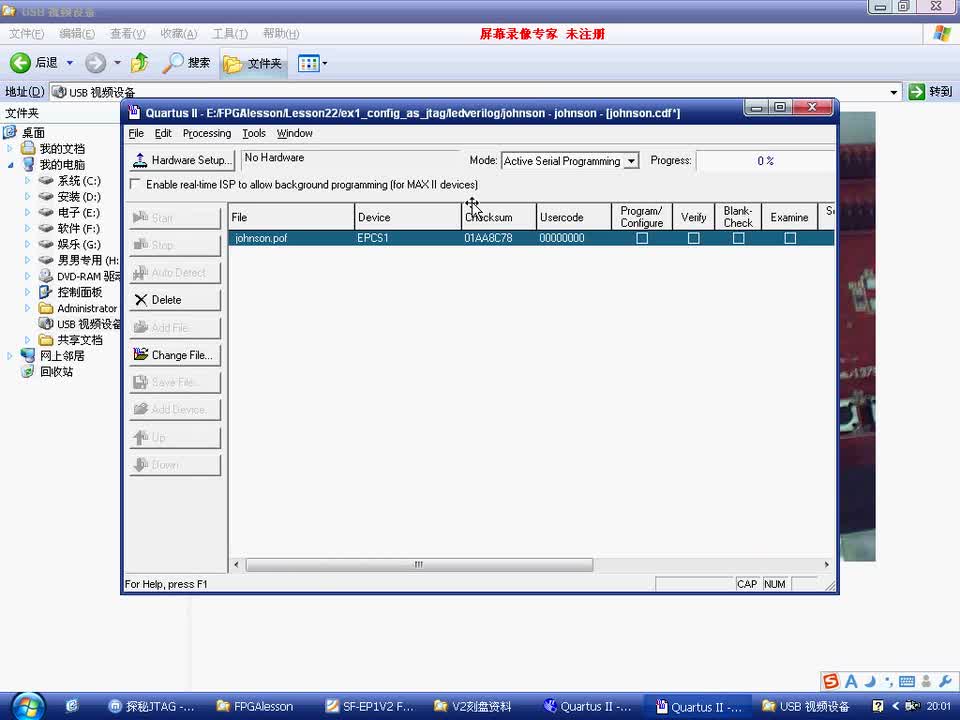

jtag口可以成功下载,as口下载成功但是程序不运行,找了好久一直没找到原因,电路配置都没有问题。

2018-01-30 21:30:04

的程序员正常工作7-I检查我的jtag链是否确保电气关闭(有一个跳线,你可以扩展你的jtag链认为FMC连接器)8-我在程序员和fpga板之间使用了两条不同的电缆(电缆没问题)解决了所有嫌疑人之后,我

2019-07-11 13:04:21

重点检查涌浪吸收电路、过电压保护电路、整流电路是否有故障。如果是行输出管击穿,可能保险电阻烧毁,这时应重点检查行逆程电容是否开焊或烧毁,+B电压是否过高等故障。烧毁:往往是由于过电流引起,或欠激励

2013-01-25 21:41:06

请教各位大神!是否可以通过FPGA内核配置的双口RAM,实现FPGA与DSP之间的数据交换?可以的话怎么实现?怎么设置FPGA的内核RAM?如何连接DSP的外部存储器XINTF的引脚和FPGA的引脚?谢谢!

2017-12-07 15:44:03

我想通过JTAG在我的设计中内部访问寄存器。1)如何挂钩fpga JTAG链?2)是否有JTAG控制器IP?我看了,没看到一个。谢谢,弗雷德

2020-05-29 06:13:24

是+ 1.8V。 BOth是相同的电压范围。但是,电压源是不同的。但是,我想在同一个JTAG链中连接两个设备。如果按照附图所述进行连接,JTAG链是否会检测CPLD和FPGA?MagalingamCPLD.docx之间的JTAG链连接图103 KB

2020-05-29 14:17:04

CYCLONE IV FPGA 想用JTAG口编程FLASH,MSEL所在BANK被用于DDR,IO电压为1.8V,手册的配置方案表中AS模式的配置电压标准没有1.8V。是否可以理解成在JTAG方式

2019-03-21 10:24:44

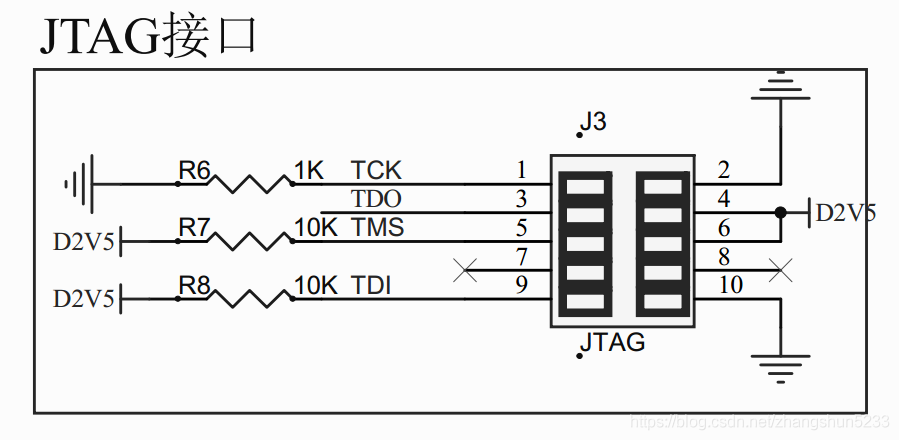

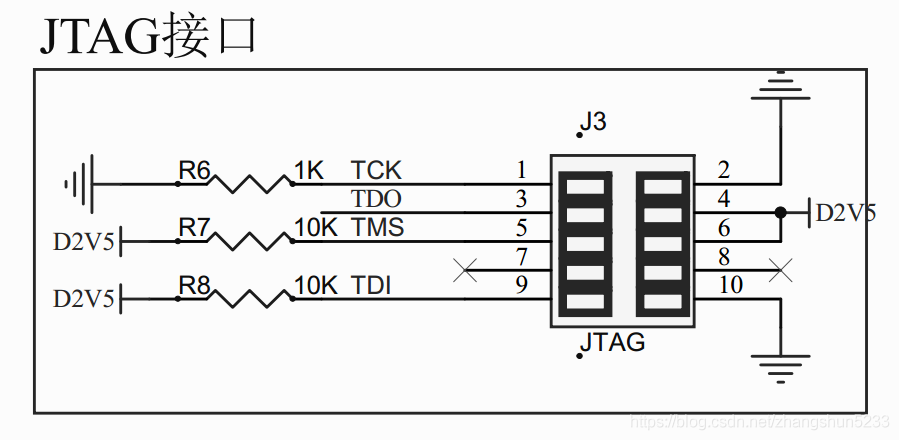

本人学生一枚,在画的第一块FPGA板上采用的EP3C25E144这个片子,实际调试中遇到了如下问题,焊上去之后整个JTAG口无法正常工作,TMS与TDI电压时钟与VCCIO存在一个压降,VCCIO用的为3.3v,而这个量管脚的电压为2.5v,各为帮忙看下JTAG口这部分电路是否存在问题,谢谢的了。

2013-03-30 21:24:12

`各位大佬们,为啥我一上电24V,电容发热,热敏电阻被击穿啊`

2019-11-16 11:02:24

您好:麻烦问一下,你们这个OKMX6UL-C2 的底板是否引出了SAI ,是和那个JTAG 口复用吗? 还是通过那个GPIO1 ,GPIO2 引出。谢谢。恩。不对吧,我都买了,销售说是和那个JTAG 管脚复用的。

2022-01-10 07:45:12

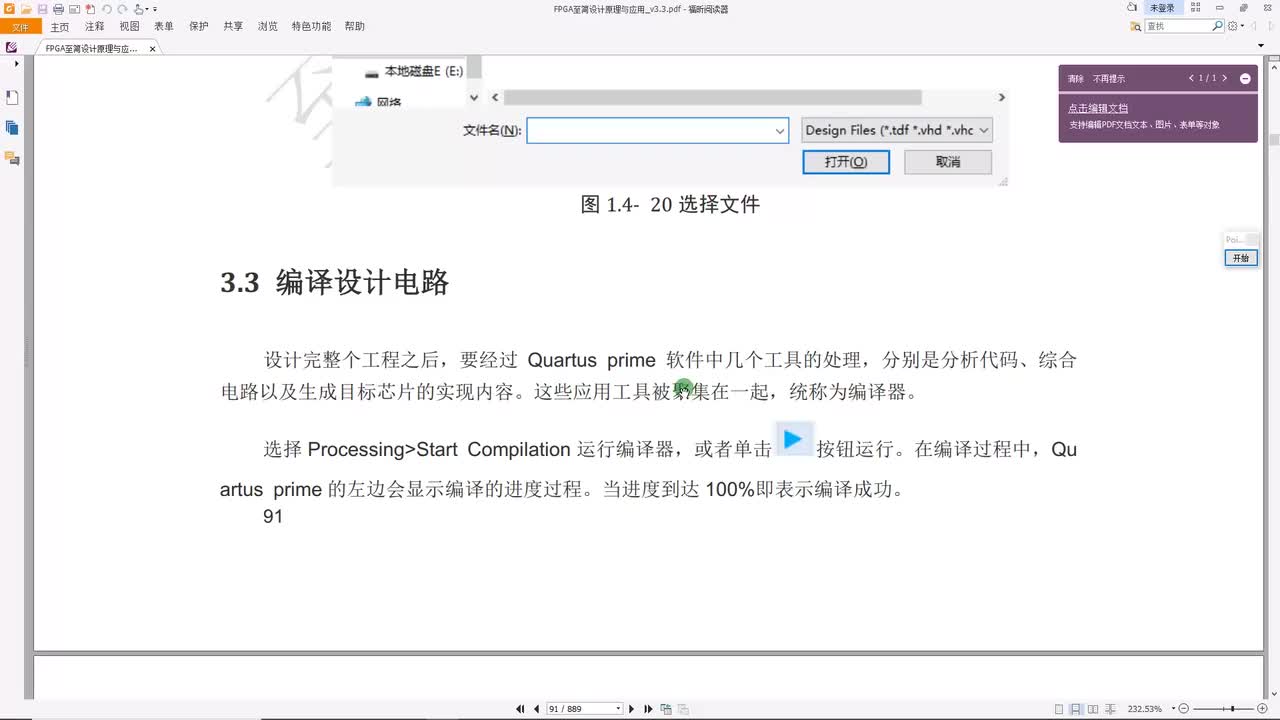

Quartus II 下FPGA管脚锁定在新建工程、编辑文件、编译、排错完成后就进入管脚锁定以及电平设置阶段。这里还是以一位全加器为例介绍管脚锁定。开发板使用FII-PRA006. 开发工具

2021-07-30 15:09:59

,FPGA无法从EEPROM-XCF32P中自动加载程序,但是通过JTAG口可以给FPGA烧些程序,而且程序也可以烧写到XCF32P中。4.用示波器测试FPGA的CCLK管脚,无法测试到CCLK。资料上

2015-08-15 09:20:26

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-05-28 09:23:25

`网上看到了各种版本,有说JTAG口要用3.3V,有说要用2.5V的。手头有个USB_BLASTER的下载器。不知道具体要用多少伏的。还有一个问题,看官方手册,说JTAG口的6脚不接。但是我手头有个开发板,JTAG的6脚与4脚接在一起了。`

2017-10-18 11:29:10

对JTAG的资料认识:(2)JTAG小知识我们经常为了方便,随意插拔JTAG下载口,在多数情况下不会发生任何问题。仍然有很小的概率因为热插拔而产生的JTAG口的静电和浪涌,最终导致FPGA管脚的击穿

2015-05-23 15:51:49

,RTCK管脚一般是用来控制是否使能JTAG接口的,请查阅数据手册;F - 如果你用的芯片比较特殊,例如STR91X,因为内部扫描链是串接的,请设置好TAP,以让仿真器知道扫描链的长度;

2011-11-30 10:18:29

本文和设计代码由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。JTAG协议制定了一种边界扫描的规范,边界扫描架构提供了有效的测试布局紧凑的PCB板上元

2020-02-25 18:40:45

将两片CPLD的jtag口级联 是否可以实现一个jtag烧写两片芯片

2017-03-31 17:31:54

什么是电容击穿?电容器被击穿的条件是什么?电容击穿是开路还是短路?电容击穿的原因是什么?如何避免介质击穿?

2021-06-18 09:59:11

下面的问题,因为热插拔而产生的JTAG口的静电和浪涌,最终导致FPGA管脚的击穿。至此,也有人怀疑是否是盗版的USB Blaster或者ByteBlasterII设计简化,去除了保护电路导致的。但经过很多

2023-05-19 19:47:36

热插拔而产生的JTAG口的静电和浪涌,最终导致FPGA管脚的击穿。至此,也有人怀疑是否是盗版的USB Blaster或者ByteBlasterII设计简化,去除了保护电路导致的。但经过很多实际情况的反馈

2024-01-19 21:19:29

右键然后点击 show IO banks,这个时候就会看到FPGA的管脚被几种颜色划分开了。一种颜色下的IO口代表一组bank。你在吧管脚的locaTIon约束完成以后。IO Bank会自动填充完毕

2019-04-03 07:00:00

,请数据流加载方向如图7.17所示。当然了,有人可能在想,JTAG在线配置是否和配置芯片加载相冲突呢?非也,JTAG在线配置的优先级是最高的,无论此时FPGA中在运行什么逻辑,只要JTAG下载启动,则FPGA便停下当前的工作,开始运行JTAG下载的新的配置数据。图7.17 FPGA离线加载原理 `

2018-03-05 16:30:35

每个单片机GPIO口都有个管脚电平标准,例如输入到管脚的电压小于1V被识别为0,大于2V被识别为1,但是如果输入的电压是在1-2V之间呢,是会被随机识别为1或0,还是会是空或者出错误?数据手册没有

2018-01-19 10:32:11

嗨,我一直在看这个问题:http://forums.xilinx.com/t5/Xilinx-Boards-and-Kits/spartan6-fpga-Jtag

2019-08-01 08:17:03

AVR单片机使用JTAG口作为普通I/O口的方法有哪几种?JTAG口的配置方式是什么?如何去使用JTAG口?使用JTAG口需要注意什么事项?

2021-07-07 06:22:05

小妹正在做一个软件,想通过编程把数据传到PC的并口在从其与jtag接口相连通过从JTAG口TDI串入数据和指令,再从TDO串出扫描结果,在主机上进行比对以实现测试,目前我主要用VC来编程。请问一下我

2008-08-15 16:21:01

我想知道是否有人能指出一份文件,该文件为Xilinx FPGA中的JTAG操作提供了深入的技术细节。我正在考虑将自己的TAP控制器构建到JTAG程序/更新FPGA。我还想了解Xilinx特定JTAG

2019-01-24 09:36:40

现在设计FPGA电路,想用EP4CE40F484,可是数据手册里没有A1、B2······这些管脚的定义,想请问一下FPGA管脚定义改怎么看啊?

2018-03-29 10:53:04

的纠纷。防护的话加齐纳稳压管保护。 现在的mos管没有那么容易被击穿,尤其是是大功率的vmos,主要是不少都有二极管保护。vmos栅极电容大,感应不出高压。与干燥的北方不同,南方潮湿不易产生静电。还有

2018-10-22 15:35:34

司用UF1M的二极管(1A1000V)接在14管脚上,低压启动100V时,二极管的电流过大1.2A会击穿二极管,高压220V时电压在1A左右没有问题,请大神分析下,在它负极端接一个10的电阻对不对,能不能起到限流的作用呢?

2019-01-11 08:00:00

是这样的。。 LPC2103的 JTAG口 也就是P0.27-P0.31口 如果想作为I/O口的话应该怎么样设置呢? 光对这几个管脚进行管脚配置好像没有用的。。是不是应该对JTAG功能进行屏蔽呢,该怎么屏蔽啊?有没有大神来指导一下。。

2014-01-14 15:06:02

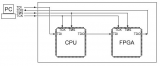

如题,怎么通过XILINX的FPGA 的JTAG 抓取CPU MPC865T的时序信号,CPU是否需要一个驱动器才可以发送片选以及读写等信号?求懂的大神说说,万分感谢!

2016-06-22 13:11:11

现在怀疑板子上的电容被击穿了,请问电容被击穿是开路还是短路?谢谢

2016-11-29 21:04:02

本帖最后由 yangk1990 于 2013-3-8 17:11 编辑

本人初学,需要设计一个示波器观测电容器被击穿的波形(或者可变电容逐渐减小到变成导体也行),但电容器的击穿着实不会...希望大神们能够指点一下!

2013-03-07 20:38:47

XAPP1251说明显示,可以在Zynq ARM处理器上运行XVC服务器来控制FPGA中的JTAG端口。但是,我不清楚,是否可以在同一个FPGA中控制PL JTAG?可以使用运行在设备PS部分上

2020-07-30 13:51:19

TM4C将jtag口锁定后解锁,就会将flash全部擦除。而在bootloader中只看到编程的命令,没有读取的命令。那这样的话是否将jtag口锁定后是否就能起到保护flash代码的作用,而不需要使用MPU。因为MPU部分没做过,看文档也是看得云里雾里的。

2019-09-09 07:43:19

本帖最后由 一只耳朵怪 于 2018-6-21 15:55 编辑

JTAG调试的下载器选用TI有配套的么?JTAG口在电路设计上可以如FPGA的JTAG口一样设计为2.54间距的排针么

2018-06-21 04:41:08

实验用到基于FPGA的数据采集板,两个月前焊好调试好了。现在拿出来用发现用不了串口通信业有问题,但是通过JTAG和AS口都能下载成功程序。在这样的情况下有没有可能板子已经坏了?求高手解答

2015-01-28 17:28:28

不出高压。与干燥的北方不同,南方潮湿不易产生静电。还有就是现在大多数CMOS器件内部已经增加了IO口保护。但用手直接接触CMOS器件管脚不是好习惯。至少使管脚可焊性变差。 MOS管被击穿的原因

2022-05-14 10:22:39

本检查清单向你揭示了如何提高你的FPGA设计的速度和可靠性,本检查清单适用于Xilinx公司的Virtex系列FPGA.采用这些技巧应该能改进你的设计性能,本检查清单应该能帮助所有的FPGA设计

2009-02-07 10:21:06 28

28 本内容向大家提供了JTAG功能及系统设计 JTAG也是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是

2011-03-30 10:04:32 0

0 通常所说的JTAG大致分两类,一类用于测试芯片的电气特性,检测芯片是否有问题;一类用于Debug;一般支持JTAG的CPU内都包含了这两个模块。

2011-09-28 10:16:17 3327

3327 如何检查光耦是否损坏?

2012-07-02 14:02:13 7265

7265 Xilinx的JTAG电缆可以通过FPGA“直接”烧写SPI/BPI。很多对xilinx开发环境不熟悉的用户,如果第一次接触这种烧写模式可能会有疑惑,FPGA是如何做到JTAG和Flash之间

2017-02-08 02:40:11 6513

6513

最近自己做了一块FPGA板子,不慎将PROM的两根引脚连错,导致在配置时无法正确识别PROM的型号,颠三倒四地排除了一个星期问题最终幸运解决。之后感叹自己实在是不小心,导致如此低级错误,不过排错

2017-02-11 06:53:11 2895

2895 同志们,根据ALTERA官方FAE(现场应用工程师)的强烈建议,请注意不要随意带电插拔你的JTAG下载接口,否则会损坏FPGA芯片的JTAG口信号管脚。

2019-07-31 17:35:00 0

0 检查文件是否存在的方法, 在Python3 文件操作中经常被用到, 因为,只有文件存在, 我们才可以对文件进行下一步处理, 那么,常用的检查文件存在的方法有哪些呢?以下是Python3 检查文件是否存在的几种方法。

2020-10-26 17:08:14 14

14 当一个电路板焊接完后,在检查电路板是否可以正常工作时,通常不直接给电路板供电,而是要按下面的步骤进行,确保每一步都没有问题后再上电也不迟。 连线是否正确 检查原理图很关键,第一个检查的重点是芯片

2022-11-16 18:26:29 2100

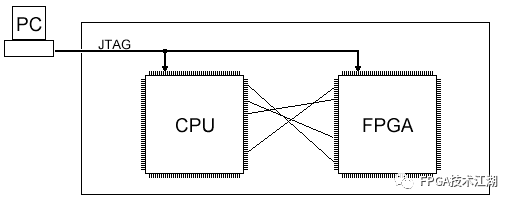

2100 JTAG可以控制(or hijack)所有IC的引脚。在图片上,也许JTAG将使所有CPU引脚输出,以及所有FPGA引脚输入。然后,通过从CPU引脚发送一些数据,并从FPGA引脚读取值,JTAG可以确保电路板连接良好。

2020-11-29 11:21:14 2280

2280

本文档的主要内容详细介绍的是FPGA JTAG工具设计的教程说明。

2020-12-31 17:30:55 18

18 赛灵思公司的FPGA芯片具有IEEE 1149.1/1532协议所规定的JTAG接口,只要FPGA上电,不论模式选择管脚M[1:0] 的电平,都可用采用该配置模式。JTAG模式不需要额外的掉电

2020-12-31 17:30:55 13

13 学习了 FPGA 一段时间,简单的设计仿真验证以及有所熟悉,今天将学习通过 JTAG 固化程序。具体步骤以及截图如下: 本教程使用的软件是:Quartus II 13.0 芯片型号

2021-03-05 15:17:50 5248

5248 在FPGA研发及学习过程中,有一个关键步骤就是下板实现,做硬件“硬现”很重要,一般来说用JTAG口比较常见一些,因此相信肯定有些大侠遇到过JTAG口失灵或者损坏无法使用的事情。

2021-03-17 14:05:33 11336

11336

开发板(在本文中将其简称为“FPGA开发板”)和专用 JTAG 调试器(在本文中将其简称为“JTAG 调试器”)。

2021-03-23 10:00:28 41

41 在stm32 IAP例程中,跳转到APP区的时候,都会检查栈顶地址是否合法,以及reset地址是否正确等信息,那么这些判断具体依据什么原理???以stm32H743为例说明↓↓↓↓检查栈顶是否合法

2021-12-16 16:58:19 10

10 对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读写测试

2022-02-16 16:21:36 1900

1900

根据查阅资料及本人的一些实践经验所得,在使用JTAG下载接口的过程中,请不要随意带电插拔,否则会损坏FPGA芯片的JTAG口信号管脚。那么如何去确认JTAG口已经损坏了呢。首先你要去排除基本的几项因素

2022-07-26 09:29:34 884

884 检查原理图很关键,第一个检查的重点是芯片的电源和网络节点的标注是否正确,同时也要注意网络节点是否有重叠的现象。另一个重点是原件的封装,封装的型号,封装的引脚顺序(切记:封装不能采用顶视图,特别是对于

2022-08-26 20:19:15 3192

3192

过压击穿是可控硅击穿的主要原因之一,可控硅对过压的承受能力几乎是没有时间的,即使在几毫秒的短时间内过压也会被击穿的,因此实际应用电路中,在可控硅两端一定要接入RC吸收回路,以避免各种无规则的干扰脉冲所引起的瞬间过压。如果经常发生可控硅击穿,请检查一下吸收回路的各元件是否有烧坏或失效的。

2022-09-15 16:58:02 5158

5158 通过JTAG接口为FPGA下载程序时遇到了速度很慢甚至ISE上配置TCK时钟最小的为250kHz时,依然无法保证下载成功。

2023-06-25 16:06:58 1130

1130

如何检查消防应急灯是否正常工作? 检查消防应急灯是否正常工作需要按照以下步骤进行: 一、查看外观是否完整 首先,要检查消防应急灯的外观是否完整,有无破损或损坏的情况。消防应急灯的外观应整洁,无裂纹

2023-11-08 16:41:32 2199

2199 如何判断故障点是否击穿放电?若故障点未击穿能否长时间带电测量 判断故障点是否击穿放电的方法通常有以下几种: 1. 视觉检查:故障点周围是否存在烧焦、熔化或溅融等现象。如果存在这些现象,说明故障

2023-12-26 16:01:51 160

160

电子发烧友App

电子发烧友App

评论