先给大家简单快速地介绍一下 Vivado 集成设计环境,即 IDE。当打开 Vivado 工程后,会有一个工程概要,向您介绍工程的设置、警告和错误信息以及工程的一般状态。

2012-04-25 09:00:43 6408

6408 LINE首度在台举办LINE Taiwan TechPulse,广邀在地开发合作伙伴共襄盛举,会中除介绍LINE平台上的五大开发套件外,也公开三大研发工程部门的团队文化,宣布扩大全球人才,希望吸引各方好手一起加入LINE为行动世代开发各种创新应用!

2016-12-27 11:36:19 887

887 世界领先的生物识别技术公司Fingerprint Cards (简称Fingerprints)宣布在中国成立客户工程部门,这个部门的研发团队主要为全球及本地的移动设备OEM客户提供服务。在此之前,Fingerprints 在全球设有四个研发中心,这个在华新设的客户工程部门是该公司在研发投入方面的重大举措。

2018-04-27 10:06:01 10499

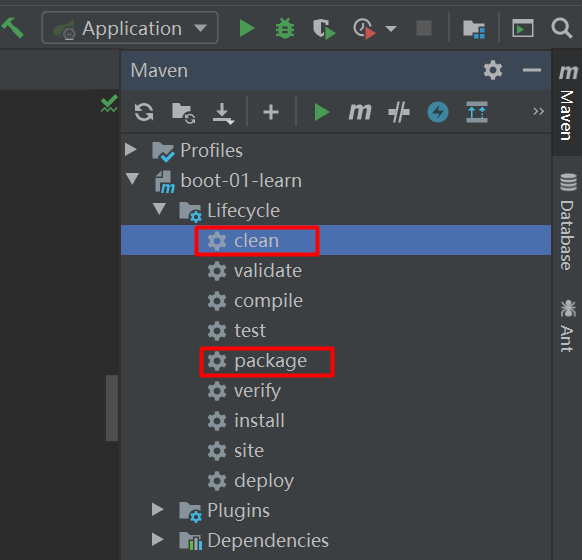

10499 01. Vivado的两种工作模式 Vivado设计有工程和非工程两种模式: 1. 工程模式: 工程模式是使用Vivado Design Suite自动管理设计源文件、设计配置和结果,使用图形化

2020-11-09 17:15:47 3884

3884

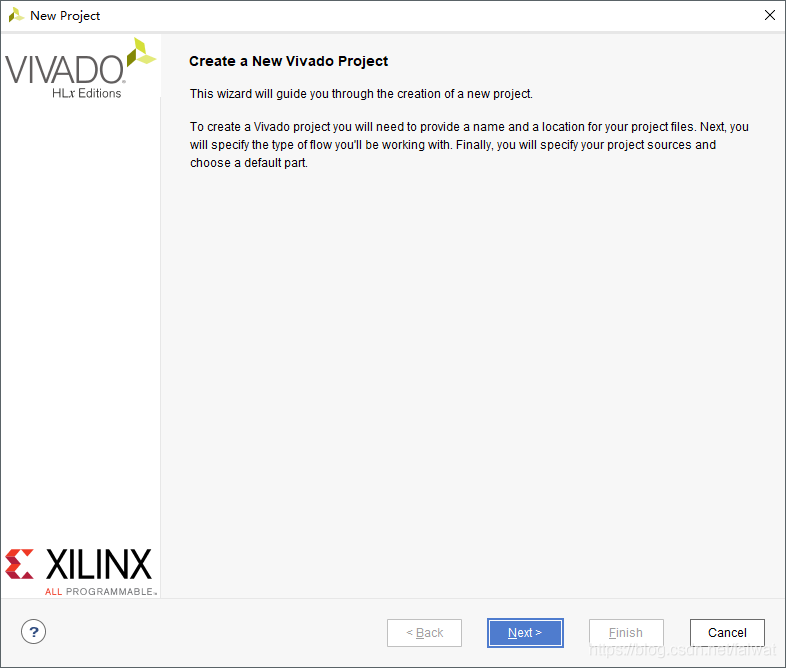

双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 403

403

大家好,我正在尝试在Vivado 2013.4上运行实施。我正在使用synplify_proI-2014.03-SP1合成我的设计。我能够合成设计并导入并正确创建一个新的vivado项目。当我尝试

2018-10-18 14:40:02

你好,我试图在SDK中运行基本的“Hello world”程序,但我不断收到错误:在vivado硬件管理器中,我看到连接的2个设备,但arm_dap_0设备具有N / A状态,而xc7z010_1

2020-04-20 09:12:04

嗨,我是新来的,这似乎论坛的这一部分是我的问题的最佳位置。如果有更好的地方发布或移动它,请告诉我。我已经购买了一个Zedboard,并尝试根据Zedboard论坛上的建议升级到更新版本的Vivado

2018-11-01 16:10:41

我已经安装了Vivado 2017.3当我打开电脑时,我收到了Vivado 2017.3.1更新的通知。按下“下一步”按钮后运行更新程序时,我进入附件中显示的页面,该页面为空白,“下一步”按钮不执行

2019-01-02 14:47:49

请问在Xilinx Vivado之中,没有PL的工程,能否直接开启SDK程序,并固化程序到ZYNQ的芯片之上

2021-03-29 17:22:00

`特权同学原创,转载请保留署名Vivado的工程文件包含了源码、IP、设置和各种编译的中间文件,动辄上百MB甚至上GB,非常占硬盘。可以通过以下步骤对编译过的工程进行瘦身,只预留必要的设置、IP

2020-08-17 08:41:25

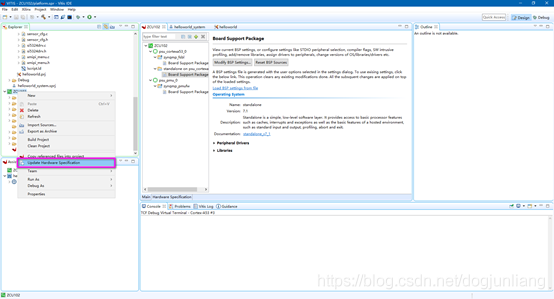

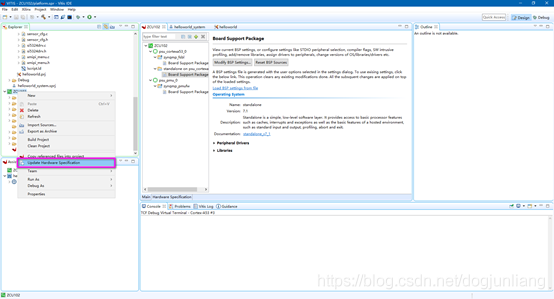

立的硬件平台上右击,选择Update Hardware Specification,选择最新导出的硬件平台文件; 在建立的应用工程上,选择应用工程对应的硬件平台,将上一个目录的硬件平台Remove,否则删除上一个VITIS目录后,目前移动以后的VITIS工程编译会出错。

2021-01-15 16:46:02

你好,我需要一些帮助。上电时,我的开发板DS1 LED发红光,Vivado硬件管理无法识别电路板。它工作正常,但在最后一次电源循环后,这个问题出现了。尝试过电源循环,闪存编程(由于vivado硬件管理不再认可电路板,因此没有成功)。我没有想法。有任何想法吗。谢谢

2020-05-25 06:33:33

适用于板卡型号: AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG 实验Vivado工程为

2021-01-22 06:46:21

的 Xilinx Platform Studio(XPS) 和 Vivado 的 IP Integrator 都是用于设计嵌入式硬件系统的环境,但是它们的用户界面迥然不同。XPS 使用一系列的下拉

2021-01-08 17:07:20

和调试PRX100-D开发板注意事项1.与Vivado软件本身相关的问题Vivado在添加新的工程/HDL文件后会自动崩溃退出这一问题出现在2018.2版本中。Xilinx官方网站上说明在2017.1版本

2021-07-31 09:09:20

我目前遇到的问题是,我的同事只给一个SDK程序,但没有给PL工程文档,打开vivado的时候是使用其他的PL工程,进去SDK程序查看程序,我纳闷的是PL的部分只给了一个.bit文档,这是几个意思,是否能实现工作、固化程序、debug已及run是否执行?

2021-03-29 17:29:14

的编译状态,以及Vivado工具的运行状态。3.2.5 流程导航器此窗口可以轻松访问指导设计从开始到结束所需的工具和命令,从项目管理开始,包括设计输入,在程序和调试部分中以比特流文件生成结束,仿真,综合

2019-07-18 15:40:33

的编译状态,以及Vivado工具的运行状态。3.2.5 流程导航器此窗口可以轻松访问指导设计从开始到结束所需的工具和命令,从项目管理开始,包括设计输入,在程序和调试部分中以比特流文件生成结束,仿真,综合

2023-09-06 17:55:44

Vivado常见问题集锦目前在学习FPGA的基本知识,之前只是在数电实验课上简单的写过几个小程序,现在属于两条腿走路,一边做硬件一边分出一定的时间做FPGA开发。我的开发板使用的是赛灵思旗下

2022-01-06 06:12:30

HI,我正在使用Vivado 2014.2和SDK 2014.2进行部分重新配置的项目。我想使用AXIHWICAP IP执行部分重新配置,我必须生成部分位文件。但是Vivado工具没有部分重新配置许可证。有没有任何方法可以生成部分位文件?谢谢,迪夫亚

2020-05-19 08:51:54

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

按照芯来官方教程使用命令make mcs 的确是可以生成mcs文件,这个文件就是helloword程序,请问如何修改makefile,将别的文件生成mcs。我的情况是将软件编译的.verilog文件

2023-08-12 07:39:10

helloword测试程序下载到开发板里面出现这种情况

2021-12-31 07:23:16

helloword测试程序下载到开发板里面出现这种情况Segmentation fault是为什么?

2022-01-13 06:29:20

时arm启动失败。两个程序都在同一硬件环境,同一sdk工程中。如果将memery_test工程里的代码换成hello world的代码,则同样能正常运行。我总结了一下,和代码没关系,和硬件环境(vivado工程)没关系,实在不清楚是哪里出问题了,还请各位能多多给点建议。谢谢了。

2016-12-20 12:38:45

请教一下,vivado怎么把带ip核的工程进行封装,保证代码不可见,可以通过端口调用。我尝试了以下方法,ippackage,如果要在另一个程序里调用,也要提供源代码;另一个方法是将网表文件edf文件与端口声明结合,这种方法只能实现不带ip核的封装

2017-07-14 09:18:30

我采用的是vivado2014.2版本,使用的是下面这个代码例程。在建立zedbord开发板例程过程中没有问题,也能通过在硬件上的测试。但是在建立基于KC705工程的时候vivado工具总是在

2018-10-08 16:37:04

Twincat是什么?一个完整的PLC工程中包括哪些部分?

2021-09-23 07:20:38

我的有部分程序是硬体SPI程序,但是51的是模拟SPI,所以需要再硬件SPI下再加模拟SPI程序,这部分程序简单吗?我是初学者,不是很懂。

2016-09-08 14:56:03

28的问题的帖子。我遇到安装问题,安装文件安装完成但安装程序在生成已安装部件列表时会挂起,安装日志的最后一行除安装程序试图调用Vivado二进制文件之外没有显示多少Tcl脚本生成已安装的设备列表。尝试

2019-01-08 10:04:15

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

一、总体流程开发工具:Vivado2020VerilogARTIX-7 FPGA AX7035这是我做的完整流程,涉及到初级开发的功能;新建工程:(RTL Project)芯片选型;编写程序:源文件

2021-07-22 07:35:26

我想编译自己的应用程序在开发板上跑,看了手册里面只写到用Qt编译helloword.bin然后在开发板上运行,但是我不想用Qt,直接makefile交叉编译要怎么操作呢

2021-12-31 07:26:31

xilinx EDF已经综合过的网表文件怎样添加到Vivado工程中?买了一个第三方的IP,给出了端口列表和核心模块发射机的.edf已经综合过的网表文件,该网表文件里面富含了大量的信息,我想知道edf文件怎样添加到Vivado工程中去?要不然的话,总是提示核心模块实例化失败!

2016-09-07 11:34:10

教程分两部分,第一部分介绍硬件FPGA程序固化,第二部分介绍嵌入式软件程序的固化。 1、 硬件FPGA程序固化: 在生成比特流文件前,需要检查一下,项目设置中Bitstream选项是否勾选了

2016-12-27 20:22:29

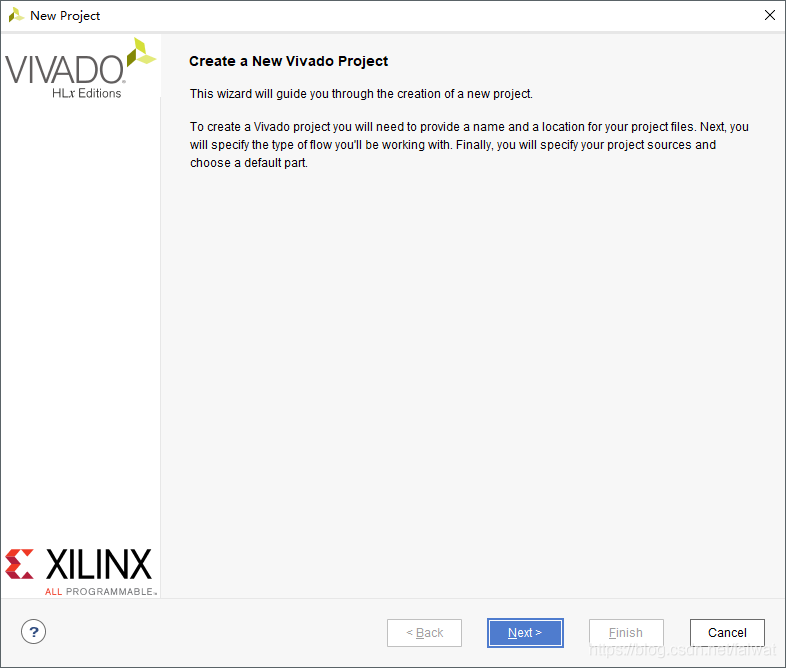

参考书上第9.1章,完成helloZynq的硬件设计部分。步骤如下1、新建工程,名字“helloZynq“,注意:工程名字及路径不能有空格,路径不能有中文。2、选择RTL project,NEXT

2015-06-25 21:31:50

今天给大家分享我们VIVADO的系列教程,内容包括:VIVADO _介绍和新建工程、VIVADO_设计输入、VIVADO_编译、配置管脚和下载、VIVADO_ILA介绍、VIVADO_固化程序的方法。

2022-01-07 09:40:11

从硬件管理器中的最后一个屏幕取消时(请参阅screen_cap.png图像),Vivado 2015.1崩溃,没有任何消息。日志文件表明它是Java的问题(请参阅hs_err_pid7988.log

2019-04-03 14:37:19

善用Vivado工程配置文件xpr快速工程创建对于第一次新建工程,没啥捷径,建议大家规规矩矩的使用Vivado的GUI创建工程。完成工程创建后,我们找到这个新建工程下的.xpr文件,它是工程配置文件

2016-10-19 18:05:13

管脚到内部的线长也需要考虑。fpga工程师可以在vivado的Tcl Console中执行tcl命令,生成对应器件的trace length文件提供给硬件工程师。具体命令如下:第一个命令为链接具体

2022-06-17 14:52:14

和IP

1. 新建工程项目

1) 双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools>

2023-08-15 19:57:56

、书籍、源码、技术文档…(2023.07.09更新)

本篇掌握基于diagram的Vivado工程设计流程,学会使用IP集成器,添加 IP 目录并调用其中的IP。本篇实现了一个简单的数字钟

2023-08-18 21:18:47

。

操作步骤

一、基于添加文件和IP

1. 新建工程项目

1) 双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design

2023-08-17 19:31:54

/Vivado_2017.2 /Vivado/2017.2并试图再次安装。但是安装程序不允许我使用之前的版本,并假装仍然安装了2017.2。必须有其他地方崩溃的安装留下一些痕迹。问题:在如此崩溃的安装后

2018-12-25 11:10:25

的使用。 1.按键硬件电路 开发板按键部分电路 从图中可以看到,电路的按键松开时是高电平,按下时是低电平。 开发板LED部分电路 而LED部分,高电平灭,低电平亮 2. 程序设计 这个程序没有

2021-01-06 17:48:21

如何在OpenMV4上运行第一个HelloWord程序呢?其实验步骤有哪些?

2022-01-27 06:08:37

如何才能成为一个硬件工程师?

2021-11-11 07:11:12

Layout设计逐渐成为主流,本系列文章同时包含有两部分内容且进行融合,欢迎大家持续关注,关注微信公众号“硬件开发不完全攻略”。 本次更新内容主要讲述如何通过Zynq 7000在Vivado下的工程文件评估芯片的各路电源功耗(电流),电源功耗(电流)评估对于电源选型、电源平面设计、电源完整仿真评估等都有很重...

2021-11-11 06:43:44

vivado_hlsip_packagexxx.zipIP核projectsolution仿真方案srcHLS工程源码test_benchHLS工程仿真程序或测试文件vivado_hls.appHLS工程文件HLS详细开发说明可

2021-11-11 09:38:32

亲爱的大家,我已成功更新了我的xilinx帐户配置文件。但是当我去下载vivado windows安装程序时,chrome会自动填写表单作为我的个人资料。当我点击下一步时,会显示此警告。“请更正错误

2020-05-27 07:17:04

Vivado硬件平台更新后Vitis工程如何快捷更新

2021-03-08 08:00:55

没有 jlink仿真器,怎么给板子烧helloword程序暂时没有仿真器

2015-09-16 11:19:41

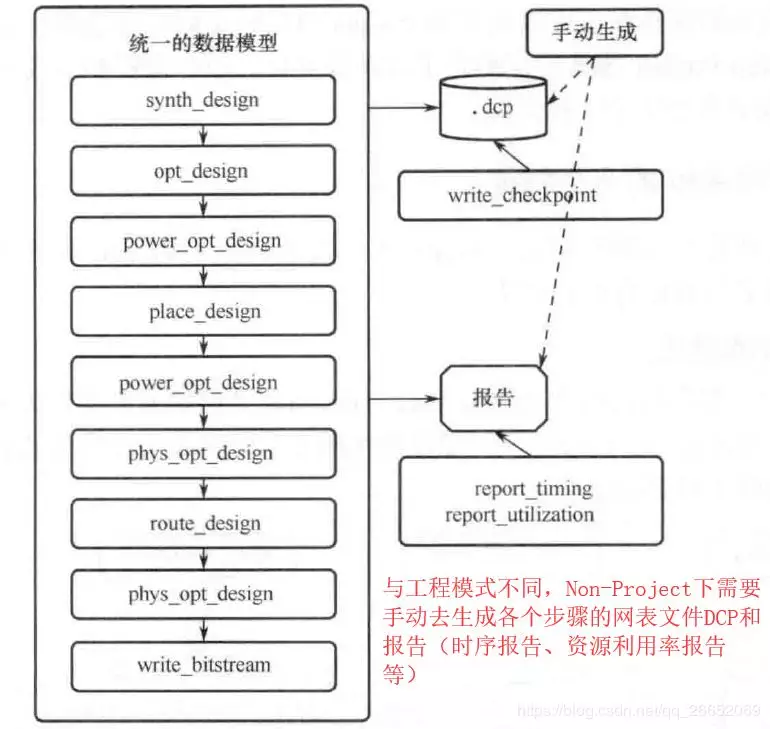

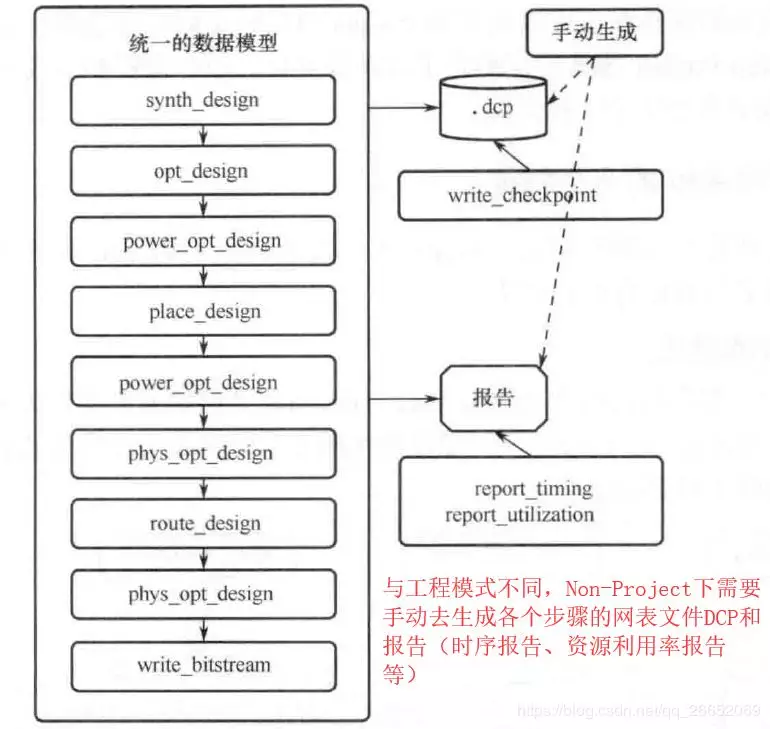

非工程模式下对应的Tcl 命令。右图所示是 Vivado 中设计实现的基本流程,蓝色部分表示实现的基本 步骤(尽管opt_design 这一步理论上不是必选项,但仍强烈建议用户执行),对应

2023-06-28 19:34:58

大家好很好地更新到Windows 10已更新至Vivado 2006我的30天许可证已激活一个问题Vivado是否内置了有线驱动程序,以便USB电缆进行交互并上传到项目板?当我的软件安装时,我注意到

2020-04-26 12:38:47

智能建筑设备招标技术文件编制手册(电气工程部分)工程建设中设备招标投标制是我国建筑业和基本管理

2008-09-06 02:02:29 0

0 智能建筑设备招标技术文件编写手册(电气工程部分)共分五章,内容有:高低压配电设备,配电变压器,发电机组成报警与消防联动控制系统,楼宇自动控制系统,综合布线系统,

2008-12-24 20:23:54 0

0 硬件工程师手册/关于硬件部分设计/单片机开发/实用开发/工程师养成

2016-07-12 16:05:52 0

0 本文主要详解Vivado中新建工程或把IP搭建成原理图,具体的跟随小编一起来了解一下。

2018-06-30 04:51:00 12345

12345

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado2016.4的性能测试

2018-07-04 11:23:00 9674

9674

无论此刻你是一个需要安装Xilinx Vivado工具链的入门菜鸟,还是已有license过期的Vivado老铁,今儿咱就借着这篇文章,把学习「Vivado如何获取License」这档子事儿给说通透咯~ 手把手教程,分三部分讲述。

2018-07-03 09:54:00 58889

58889

1 Vivado HLS简介 2创建一个Vivado-HLS工程 2.1打开Vivado HLS GUI 2.2创建新工程 在 Welcome Page, 选择Create New Project

2017-12-04 10:07:17 0

0 随着嵌入式技术的普及,硬件工程师的性质也有所改变。嵌入式硬件工程师与我们平常所说的硬件工程师不同。嵌入式硬件工程不但要求具备硬件工程师的基本技能,还必须完成部分软件工程师的工作,例如: 底层驱动

2018-04-08 08:58:55 68789

68789 了解如何在Vivado中执行工程变更单(ECO)。

本视频将向您介绍ECO的常见用例,我们推荐的完成ECO的流程,优势和局限性,并将演示功能设计的ECO。

2018-11-21 06:40:00 4647

4647

本视频介绍了UltraScale +芯片的部分重配置功能,展示了Vivado Design Suite中部分重配置的新功能,并介绍了对部分重配置的更广泛的访问权限

2018-11-20 06:25:00 3831

3831 物理优化是Vivado实现流程中更快时序收敛的重要组成部分。

了解如何在Vivado中应用此功能以交换运行时以获得更好的设计性能。

2018-11-23 06:06:00 3728

3728 了解如何使用Vivado System Generator for DSP进行点对点以太网硬件协同仿真。

System Generator提供硬件协同仿真,可以将FPGA中运行的设计直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

4262 实际上Tcl的功能可以很强大,用其编写的程序也可以很复杂,但要在Vivado或大部分其它EDA工具中使用,则只需掌握其中最基本的几个部分

2019-07-24 16:52:00 3179

3179

Vivado硬件平台更新后Vitis工程如何快捷更新

2021-01-22 05:51:23 1065

1065

本文介绍如何在 vivado 开发教程(一) 创建新工程 的基础上, 使用IP集成器, 创建块设计。

2022-02-08 10:47:39 2090

2090

本文主要介绍如何使用Vivado 开发套件创建硬件工程。

2022-02-08 10:41:59 1012

1012

Vivado硬件平台更新后Vitis工程如何快捷更新

2021-01-28 09:28:18 12

12 本文主要介绍如何使用Vivado 开发套件创建硬件工程。

2021-02-02 07:13:32 18

18 vivado搭建一个简单PS 的工程(记得勾选uart),生成bit,导出硬件,启动sdk,新建helloworld的工程就行。然后跑一下,看串口是否能打印helloworld。如果可以,这就成功搭建工程了。

2022-07-05 10:10:46 2136

2136 注意:目前这个是Micrium官网的最新版本,该版本支持Vivado2019.1。但测试使用的是Vivado2018.3。

2022-08-01 11:53:06 2218

2218 Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado 2020.2为例,讨论如何升级Vivado工程脚本。

2022-08-02 10:10:17 1542

1542 一个完整的vivado工程往往需要占用较多的磁盘资源,少说几百M,多的甚至可能达到上G,为节省硬盘资源,可以使用Tcl命令对vivado工程进行备份,然后删除不必要的工程文件,需要时再恢复即可。

2022-08-02 15:01:06 3696

3696 Spring+Vue工程部署在Linux

2023-01-13 14:19:54 689

689

版本迁移的操作想必大家已经做过不少了,其中包括从ISE转换到vivado与vivado老版本迁移到新版本。郑智海同学给大家介绍了一下如何把工程从ISE迁移到vivado中。

2023-01-30 09:11:30 3020

3020 vivado的工程创建流程对于大部分初学者而言比较复杂,下面将通过这篇博客来讲解详细的vivado工程创建流程。帮助自己进行学习回顾,同时希望可以对有需要的初学者产生帮助。

2023-07-12 09:26:57 1101

1101

电子发烧友网站提供《Vivado设计套件用户:使用Vivado IDE的指南.pdf》资料免费下载

2023-09-13 15:25:36 3

3 电子发烧友网站提供《Vivado Design Suite教程:嵌入式处理器硬件设计.pdf》资料免费下载

2023-09-15 10:12:33 1

1 Language,硬件描述语言),而SystemVerilog则是HDVL(Hardware Design and Verification Language,硬件设计与验证语言)。由此可见,SystemVerilog也是可以用于硬件设计的,也是有可综合部分的。SystemVerilog本身由3部分构成。

2023-10-19 11:19:19 342

342

电子发烧友App

电子发烧友App

评论