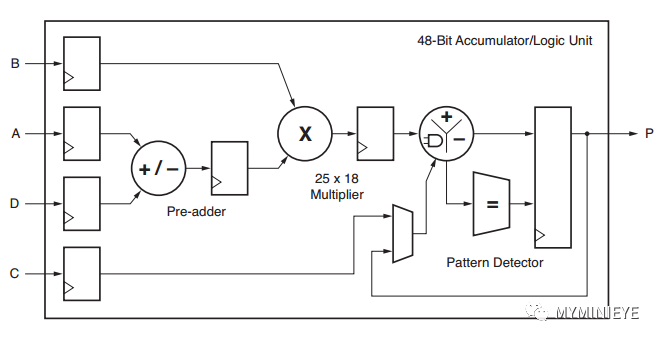

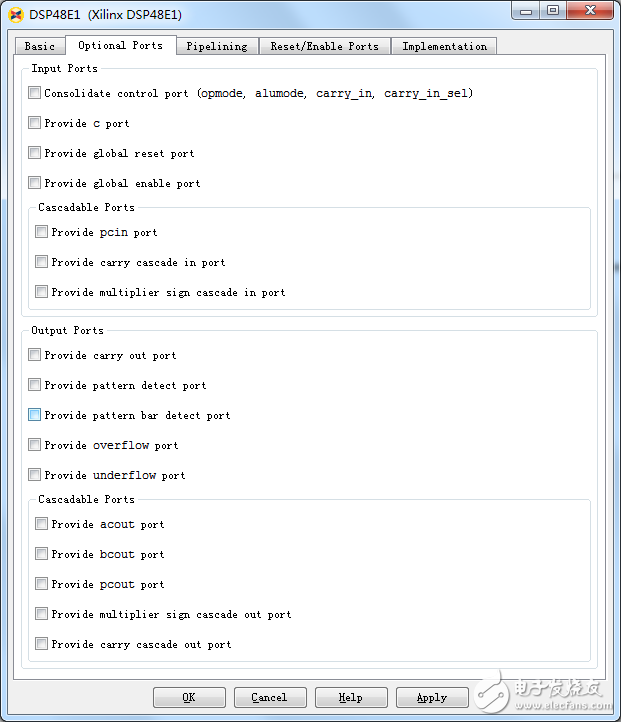

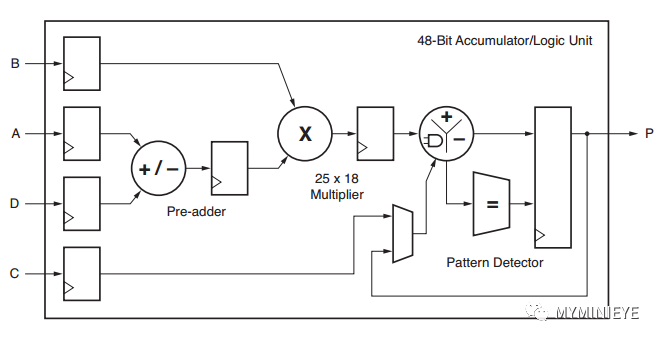

充分利用DSP资源,我们需要对DSP48E1有所了解。 1.DSP48E1介绍 DSP48E1是7系列的最小计算单元,DSP资源,支持许多独立的功能,其基本功能如下所示 DSP48E1简易模型 包括: 带有D寄存器的25位预加法器 25*18二进制乘法 48位累加 三输入加法 其他的一些功能还包括

2020-09-30 11:48:55 26617

26617

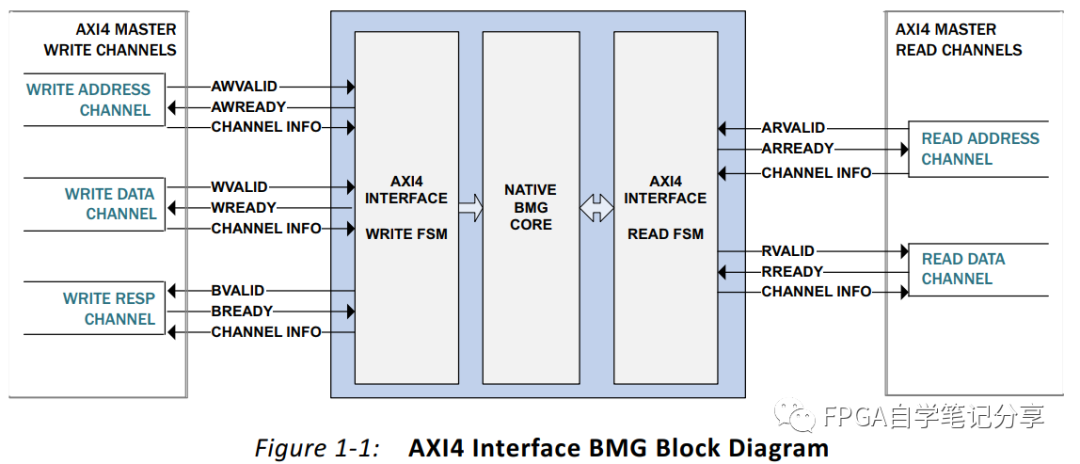

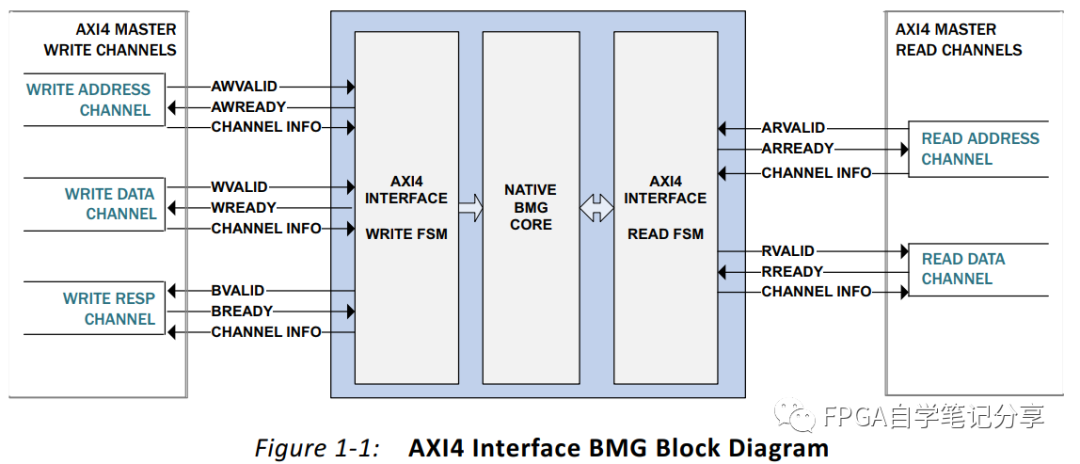

之前的文章对Block Memory Generator的原生接口做了说明和仿真,本文对AXI接口进行说明。

2023-11-14 18:25:10 685

685

和C寄存器,具有独立的复位和时钟启用。 •CARRYCASCIN和CARRYCASCOUT内部级联信号支持两个DSP48E1片中的96位累加器/加法器/减法器 •MULTSIGNIN

2021-01-08 16:46:10

7系列FPGA DSP48E1片的特点什么

2021-03-05 06:26:41

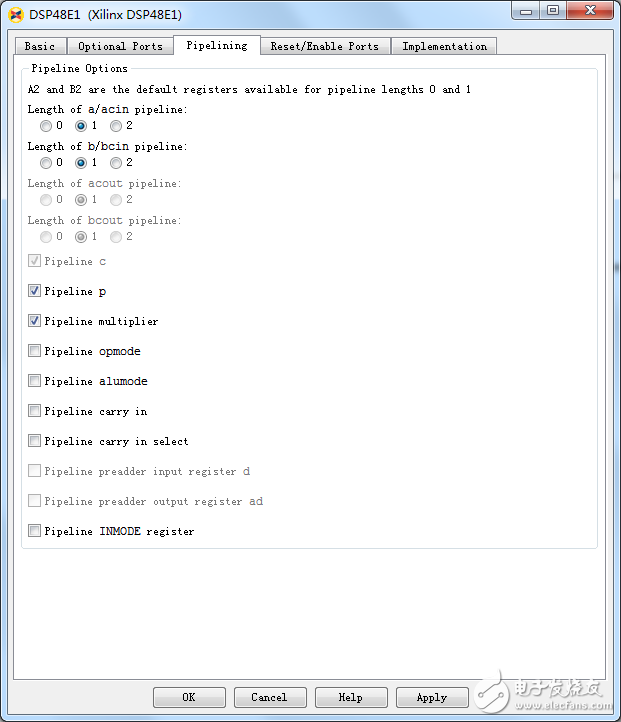

我正在实例化DSP切片并进行简单的乘法然后加法((A * B)+ C)。根据DSP48E1用户指南,当使用所有三个流水线寄存器时,它给出了最高频率为600 MHz。但就我而言,它使用流水线寄存器

2020-06-12 06:32:01

嗨,我有一个如下的指令:(D-A)* B + C.端口A,B,C,D与DSP48E1输入引脚相对应。我试图将整个操作打包在DSP单元中。 (顺便说一句,我的数据宽度是8位)在布局和布线完成后,我

2019-04-01 14:25:40

在我的设计中,我需要延迟一些数据(32位宽)一段时间。我一直在使用SRL16而不是FFs,它可以很好地延迟超过几个周期。我还注意到,使用DSP48E1片很容易将数据延迟到48位宽,延迟三个周期,因此

2019-04-18 06:40:33

DSP48E1属性

2021-01-27 06:21:23

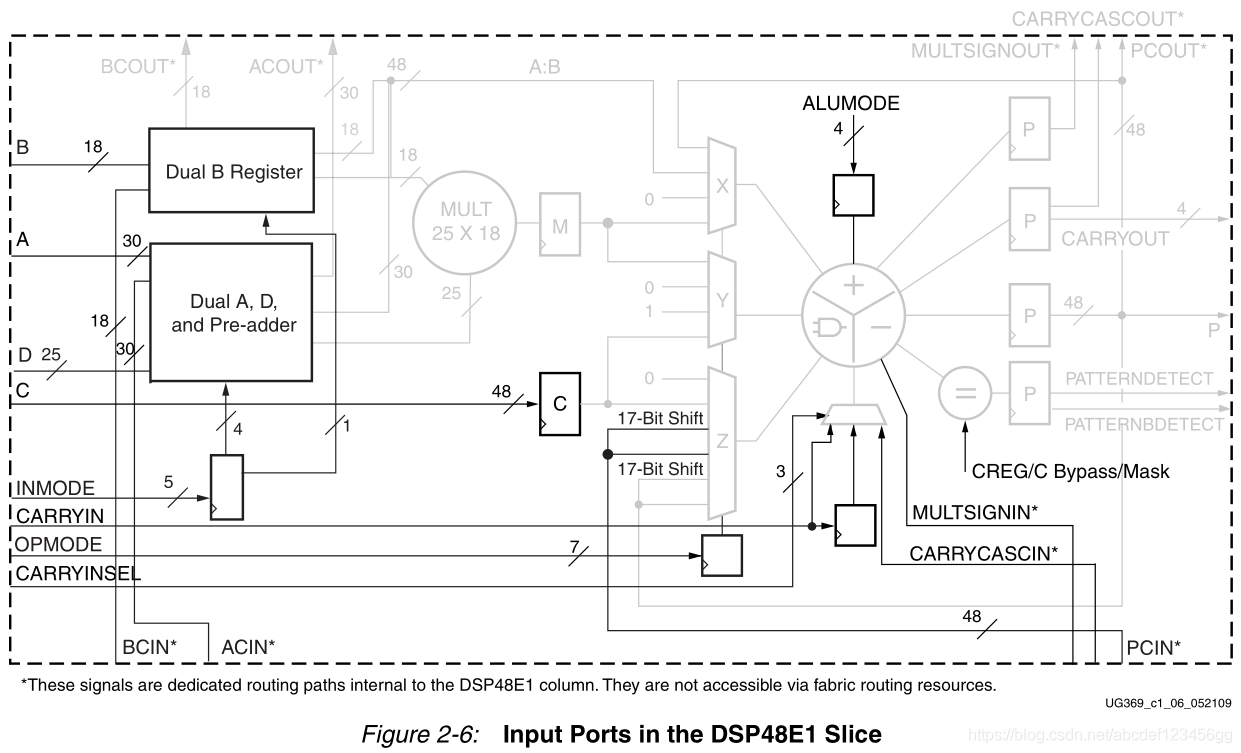

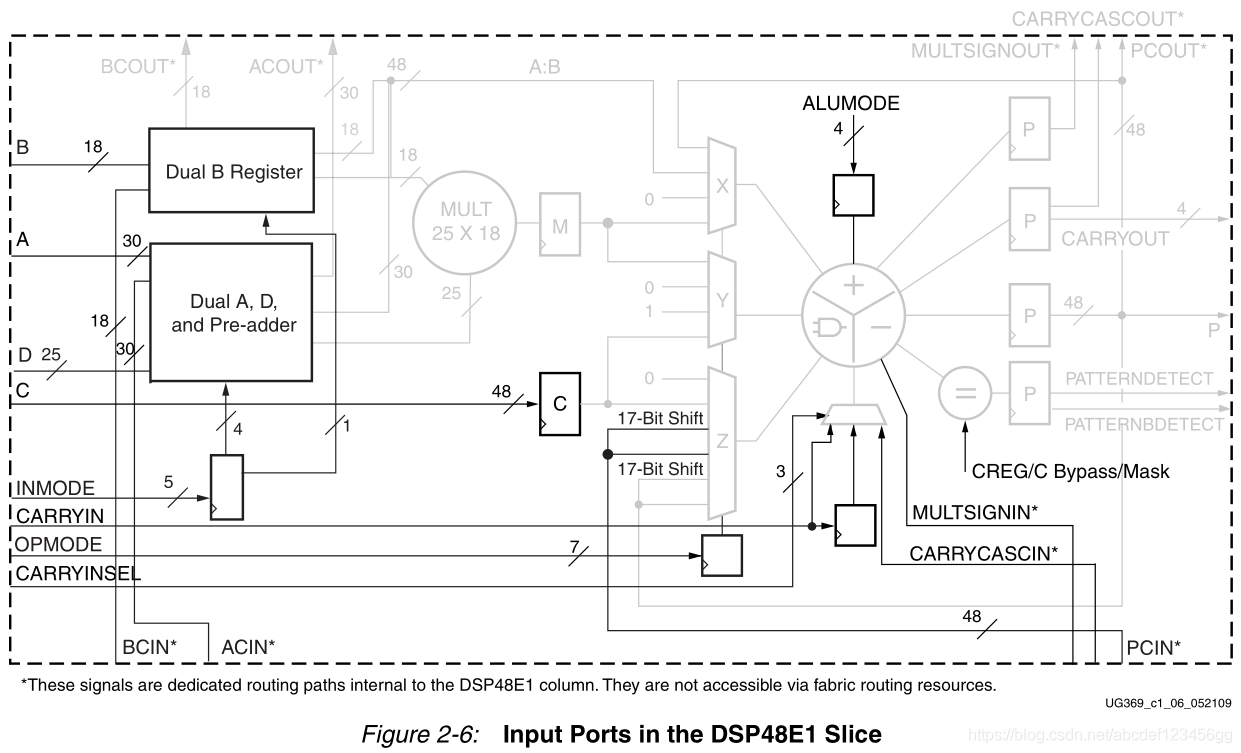

以及相应的时钟启用输入和复位输入都是保留端口。D和INMODE端口对于DSP48E1片是唯一的。本节详细描述DSP48E1片的输入端口。图2-6中突出显示了DSP48E1片的输入端口

2020-12-23 16:54:08

:System Generator for DSP(SysGen)的许可证签出失败。无法联系Xilinx许可证管理器。请检查以下内容:(1

2019-01-28 07:16:36

错误:System Generator for DSP(SysGen)的许可证签出失败。无法联系Xilinx许可证管理器。请检查以下内容:(1)XILINX环境变量指向有效的ISE安装(2

2018-12-29 10:35:12

FPGA中的数字控制器是什么?System Generator中的PID控制器是如何设计的?

2021-04-08 06:51:46

大家好,这是我第一次使用System Generator工具,如果有人能够解决一个不让我继续参与我的硬件协同仿真项目的问题,我想。我正在使用Matlab R2013b,Xilinx ISE 14.7

2020-03-23 06:53:11

根据我的理解,System Generator是MatLab到RTL的转换,因此不包括Vivado的优化过程。问题1--是真的。确实,Vivado中的优化将大大改变系统描述,而系统描述不会向后兼容

2019-04-25 12:47:45

HI,我正在使用System Generator 2014.4 30天评估包,Matalb 2014B。简单地说我想使用FIR编译器,当我尝试编辑它的参数时,我得到了两个错误: - 1.“来自MEX

2020-03-24 09:01:59

AT键盘接口说明 The AT keyboardIBM Keyboards,Not really an interesting topic,One would expect.So why would

2009-10-24 11:01:44

1、FireflyApi使用案例与接口说明FireflyApi提供了部分系统接口以及封装了部分用户需要的功能接口,主要是为了让用户容易和简单的使用系统常用接口, 此文档只是对接口进行简单的说明,具体

2022-07-19 16:16:40

1、FireflyApi接口说明FireflyApi提供了部分系统接口以及封装了部分用户需要的功能接口,主要是为了让用户容易和简单的使用系统常用接口, 此文档只是对接口进行简单的说明,具体

2022-07-13 17:26:41

/fpga-design/simulink-with-xilinx-system-generator-for-dsp.htmlhttp://www.mathworks.cn/searchresults/?c%5B%5D

2013-10-05 11:59:34

USE和System Generator何时才能胜任64位Windows 7?以上来自于谷歌翻译以下为原文When will ISE and System Generator be qualified for 64 bit Windows 7?

2018-11-26 15:05:56

最近在搞system generator仿真,发现getway in这个模块参数设置变化导致MATLAB闪退问题,贴图如下其中getway in 这个模块数据类型换成定点有符号或者无符号数都不得行,换成布尔值又会出现错误,不知为何啊!求教。

2018-01-05 21:43:53

目录OLED显示实验(8080接口方式)OLED接口说明读写流程简述SSD1306 的 8080 并口读写时序解析OLED显存的排列OLED基本操作流程OLED库函数使用说明OLED库函数使用示例

2021-12-03 06:07:01

,这样的输入选择有助于构建多种类型,高流水化的DSP应用。

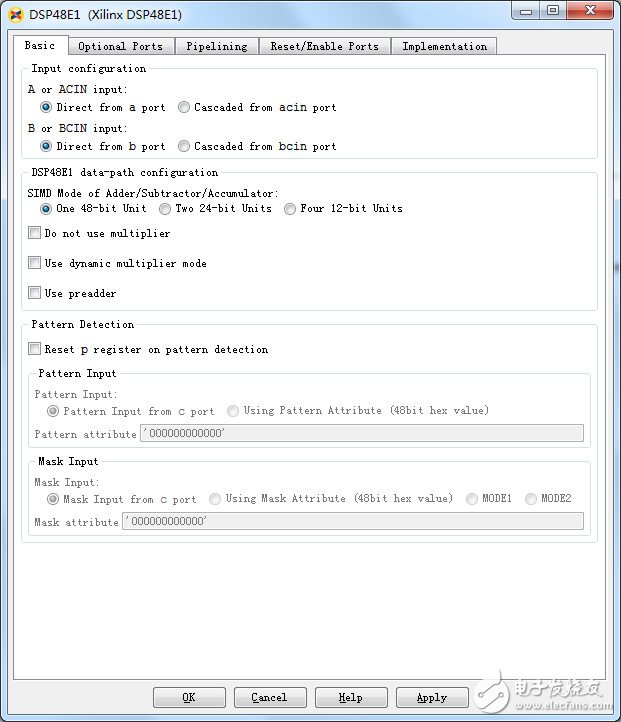

2. DSP48E1使用

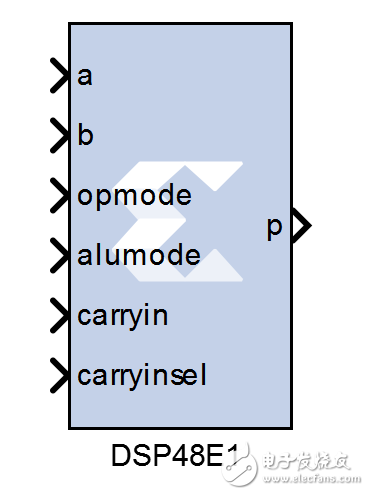

(1)DSP原语使用的每个端口及位宽如下所示:

①表示的数据通道,运算数据的输入。

②寄存器配置通道,我们可以通过

2023-06-20 14:29:51

为什么BUFG驱动DSP48E1的CE会出现问题?警告:LIT:683 - DSP48E1符号“Inst_control_loop / u_Subsystem11

2020-06-12 11:45:43

使用system generator导入xilinx模块时,只要连线两个模块,matlab就崩溃,有知道原因的大佬吗?

2018-01-19 17:54:57

.Vivado 2016.4与Spartan-6不兼容。据Xilinx称,Vivado不支持任何早于7系列的设备系列。)根据以下说明,Xilinx System Generator可以嵌套在ISE Design

2018-12-27 10:55:34

大家好,我正在使用具有Virtex-4 FX100的定制板。在内部,有一个基于VHDL的框架,它将定制板上的不同部分与“DSP内核”连接,后者是在System Generator下开发的。在这

2019-01-15 10:39:11

在system generator中,我把(-128~127),变为(-1~1),但是下载到硬件中,使用chipscope抓取到的数据确实(-128~127),请问是怎么回事

2016-08-10 15:32:38

% DSP48E1的数量:576中的6个1% EFUSE_USR数量:0 0% FRAME_ECC的数量:1 0%中的0 GTXE1的数量:24个中的0个0% IBUFDS_GTXE1s数:12个中0个0% ICAP

2020-06-12 08:35:50

有做System Generator处理图像的吗?遇到一些问题,一起商量下

2020-09-28 19:04:58

嗨,我想使用DSP45E1模块实现Multply-Add操作,其中一个要求是我需要DSP模块上的3级流水线。查看UG479 7系列DSP48E1 Slice用户指南(UG479) - Xilinx

2020-07-21 13:52:24

嗨,我正在尝试学习如何使用System Generator来创建自己的IP核。首先,我在DocNav中找到了一个ug948-vivado-sysgen-tutorial文档。我在哪里可以找到本文档中描述的示例?我在安装目录中的“examples”文件夹中找不到完全相同的示例。提前致谢马丁

2020-05-22 07:22:09

简化DSP48E1片操作

2021-01-27 07:13:57

(即(可用来防止溢出的位)是5。为了扩展MACC操作的数量,应该使用ACC_EXTEND特性,它允许MACC通过两个DSP48E1片扩展到96位。如果A端口被限制为18位(有符号扩展为25位),那么

2021-01-08 16:36:32

各位大佬,我在安装System Generator时,跟着教程走,发现在vivado中没有出现System Generator for DSP这个选项,请问是我哪里安装得不对吗?

2023-09-26 21:54:58

当我完成SDx 2017.2的安装时,没有安装System Generator的选项。我正在运行从Xilinx下载的安装程序:https://www.xilinx.com/member/forms

2019-01-07 10:59:00

你好,我叫Joaquín。有人知道,我可以在Matlab / Simulink中使用System Generator创建一个双向(inout)端口。我正在尝试为Xilinx的外部存储器创建一个接口

2019-05-09 14:36:24

我一直在尝试将DSP48E1原语用于具有自动终端计数重置的计数器。大部分工作都很好,但我看到的一个问题是我无法让DSP48E1进行模式检测0.如果我将C输入设置为48'd0,则在P =开始时

2020-07-28 10:38:40

据我所知,乘法默认由FPGA中的DSP48E1片处理。有没有什么方法可以禁用或自定义DSP48E1元素用于自己的新算法?我的目标是使用我的乘法算法,而不是使用FPGA中的现有DSP算法。请指教。谢谢。

2020-05-04 15:22:35

嘿,为了在Zynq设备上对一种算法的不同实现进行简单比较,我想为每种实现的资源使用创建一个指示符,例如CLB的使用。因此,获得基本元素CLB,DSP48E1和BRAM36K的面积指标会很好。在

2020-07-25 11:04:42

例子GPIO_DSP1中的System_printf输出到了哪里?

2022-01-06 07:28:31

xilinx公司的网络教程“利用 System Generator 进行 DSP 设计”谁有?上传一份给小弟吧

2013-03-14 12:17:03

/ Using_DSP48E.DSP48E_I1 / DSP48E1在站点DSP48_X3Y28上放置错误。该站点是分区拥有的私有区域组的一部分

2019-01-25 10:36:59

飞思卡尔单片机调试接口说明

2012-08-27 01:15:58

8针圆形接口说明:包含各种圆形接口定义说明

第四章 与PLC的连接方法... 37

2007-11-19 13:25:07 212

212

采用Gardner算法,对QPSK调制解调系统中的位同步系统进行设计与实现,大大提高了系统性能和资源利用率。重点阐述采用FPGA开发环境System Generator系统设计工具进行位同

2010-07-21 16:12:40 26

26 点击下载:8针din圆形管脚排列接口说明

2007-11-19 13:21:50 18227

18227

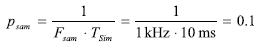

深入了解赛灵思System Generator中的时间参数

基于模型的设计(MBD)因其在缩小实时系统抽象的数学建模和物理实现之间差距方面的光明前景而备受关注。通过使用相同的

2009-12-29 11:40:30 1300

1300

HDL设计和验证与System Generator相结合

Xilinx®SystemGeneratoRForDSP是用来协助系统设计的MATLABSimulink模块集。SystemGeneratorforDSP在熟悉的MATLAB环境中引入XilinxFPGA对象,让您能够

2010-01-06 14:39:30 1181

1181

Xilinx公司推出的DSP设计开发工具System Generator是在Matlab环境中进行建模,是DSP高层系统设计与Xilinx FPGA之间实现的桥梁。在分析了FPGA传统级设计方法的基础上,提出了基于System Generator的

2013-01-10 16:51:24 58

58 Xilinx FPGA工程例子源码:System Generator的设计实例

2016-06-07 14:41:57 22

22 M12接口说明

2016-12-27 16:46:31 0

0 前段时间一直在帮本科生做电赛,需要用到FPGA笔者作为学长责无旁贷去帮忙,耽误了更新,抱歉。为了表现笔者的诚意,今天拿出干货——DSP48E1的使用,全程高能不要眨眼。 安富利的陈博士出的试用

2017-02-07 20:23:33 2159

2159 概述 利用4个dsp48e1模块,实现四路加法器,dsp48e1模块在手册中表示比较复杂,找了两个图,可以大致看懂他的基本功能。 图1 dsp48e1端口说明 图2 简化的DSP48E1结构 软件

2017-02-08 01:10:08 473

473

for DSP2015.3版,该工具可让系统工程师运用赛灵思All Programmable器件设计高性能的DSP系统。借助新的System Generator,算法开发人员可在其熟悉的MATLAB

2017-02-09 01:23:41 279

279 前一阵一直在忙,所以没有来得及写博文。弄完杂七杂八的事情,又继续FPGA的研究。使用Verilog HDL语言和原理图输入来完成FPGA设计的方法都试验过了,更高级的还有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10:11 8192

8192

为了适应越来越复杂的DSP运算,Virtex-6中嵌入了功能更强大的DSP48E1 SLICE,简化的DSP48E1模块如图5-16所示。

2017-02-11 09:17:13 1391

1391

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可是设置

2017-02-11 11:53:11 3778

3778

system generator是xilinx公司的系统级建模工具,它是扩展mathworks公司的MATLAB下面的simulink平台,添加了XILINX FPGA专用的一些模块。加速简化了FPGA的DSP系统级硬件设计。

2017-02-11 19:21:33 7386

7386

现在的FPGA算法的实现有下面几种方法: 1. Verilog/VHDL 语言的开发 ; 2. system Generator; 3. ImpulsC 编译器实现从 C代码到 HDL 语言; 4.

2017-11-17 14:29:06 7298

7298 在FPGA平台上应用System Generator工具实现了高精度频率估计Rife算法。不同于传统的基于HDL代码和IP核的设计方法,采用System Generator工具可以使复杂算法

2017-11-18 09:01:51 2208

2208

SONY LANC接口说明

2018-03-01 17:27:07 0

0 本视频产品演示介绍了 Xilinx 系统生成器(System Generator)和 Xilinx ISE® 项目浏览器(Project Navigator)设计环境之间的新整合。

2018-06-06 13:46:00 3024

3024

了解如何将Vivado HLS设计作为IP模块整合到System Generator for DSP中。

了解如何将Vivado HLS设计保存为IP模块,并了解如何将此IP轻松整合到System Generator for DSP的设计中。

2018-11-20 05:55:00 2940

2940 了解如何在System Generator中使用多个时钟域,从而可以实现复杂的DSP系统。

2018-11-27 06:42:00 3450

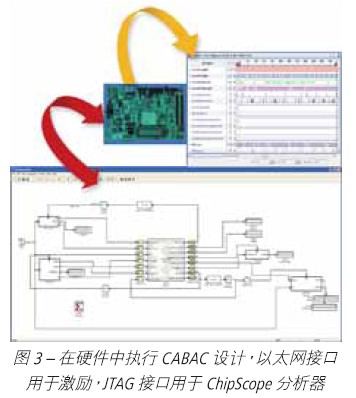

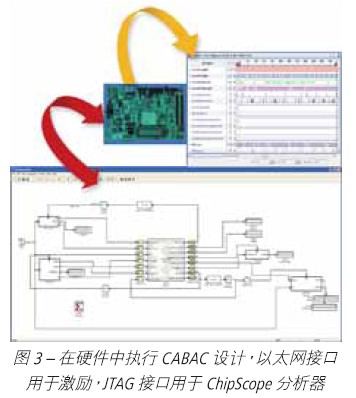

3450 了解如何使用Vivado System Generator for DSP进行点对点以太网硬件协同仿真。

System Generator提供硬件协同仿真,可以将FPGA中运行的设计直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

4262 A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相应的时钟启用输入和复位输入都是保留端口。D和INMODE端口对于DSP48E1片是唯一的。本节详细描述DSP48E1片的输入端口

2022-07-25 18:00:18 4426

4426

DSP48E1片的数学部分由一个25位的预加器、2个25位、18位的补法器和3个48位的数据路径多路复用器(具有输出X、Y和Z)组成,然后是一个3输入加法器/减法器或2输入逻辑单元(参见图2-5)。使用2输入逻辑单元时,不能使用乘法器。

2022-01-21 14:14:26 962

962 在DSP48E1列中,级联各个DSP48E1片可以支持更高级的DSP功能。两个数据路径(ACOUT和BCOUT)和DSP48E1片输出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供级联功能。级联数据路径的能力在过滤器设计中很有用。

2022-06-21 08:55:00 1882

1882 在DSP48E1列中,级联各个DSP48E1片可以支持更高级的DSP功能。两个数据路径(ACOUT和BCOUT)和DSP48E1片输出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供级联功能。级联数据路径的能力在过滤器设计中很有用。

2021-01-27 07:34:32 8

8 A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相应的时钟启用输入和复位输入都是保留端口。D和INMODE端口对于DSP48E1片是唯一的。本节详细描述DSP48E1片的输入端口

2021-01-27 08:18:02 2

2 DSP48E1片的数学部分由一个25位的预加器、2个25位、18位的补法器和3个48位的数据路径多路复用器(具有输出X、Y和Z)组成,然后是一个3输入加法器/减法器或2输入逻辑单元(参见图2-5)。使用2输入逻辑单元时,不能使用乘法器。

2021-01-29 08:19:37 13

13 RTSP协议开发接口说明书

2021-10-15 09:55:20 2

2 LCD MCU屏(I80)接口说明

2021-12-08 16:21:07 7

7 本篇博文是面向希望学习 Xilinx System Generator for DSP 入门知识的新手的系列博文第一讲。其中提供了有关执行下列操作的分步操作方法指南。

2022-02-16 16:21:36 1578

1578

正在加载...

电子发烧友App

电子发烧友App

评论