引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2022-07-25 10:13:44 4067

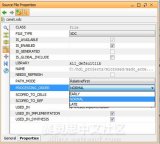

4067 I/O约束(I/O Constraints)包括I/O标准(I/OStandard)约束和I/O位置(I/O location)约束。

2023-11-18 16:42:28 507

507

IS_ROUTE_FIXED命令用于指定网络的所有布线进行固定约束。进入Implemented页面后,Netlist窗口如图1所示,其中Nets文件展开后可以看到工程中所有的布线网络。

2023-12-16 14:04:31 507

507

在进行布局约束前,通常会对现有设计进行设计实现(Implementation)编译。在完成第一次设计实现编译后,工程设计通常会不断更新迭代,此时对于设计中一些固定不变的逻辑,设计者希望它们的编译结果

2024-01-02 14:13:53 434

434

小弟的74系列的芯片资料,虽然是英文的,但基本的功能引脚还是可以看懂的。与大家分享下。

2013-08-08 09:11:13

74系列芯片总汇,

2017-03-11 11:22:56

74系列芯片的型号有哪些区别?74系列芯片的功能有哪些?

2021-08-20 06:08:21

74系列集成电路有哪些类型?

2021-11-02 09:38:00

74ls系列中文资料,打成一个压缩包,方便大家查阅74ls系列中文资料.rar (13.45 MB )

2019-05-06 23:17:18

74ls系列芯片的流水灯谁有电路图

2015-05-20 12:52:34

74、74HC、74LS系列芯片对比,

2013-11-16 14:13:25

Normal,可以通过MODBUS寄存器地址40001~40008来读取CH0~CH8的数值。更加详细的MODBUS地址对照表参见ADAM-4100系列的英文手册。Modbus协议读到的数值为16进制或

2019-07-08 06:50:35

ADAM-4117是什么?ADAM-4117测量电流的跳线该如何去设置?ADAM-4117硬件是怎样进行连线的ADAM-4117的安装、配置和测试过程是怎样的?

2021-07-26 08:16:47

如何用adam5510控制ch453数码管显示

2018-05-19 13:17:15

大家好!我是一名学生,与我的合作伙伴一起在MicroZed板上开展项目。我们正在使用Vivado 2015.4,Xilinix SDK 2015.4和Digilent USB-JTAG编程电缆(我们

2019-10-22 08:47:02

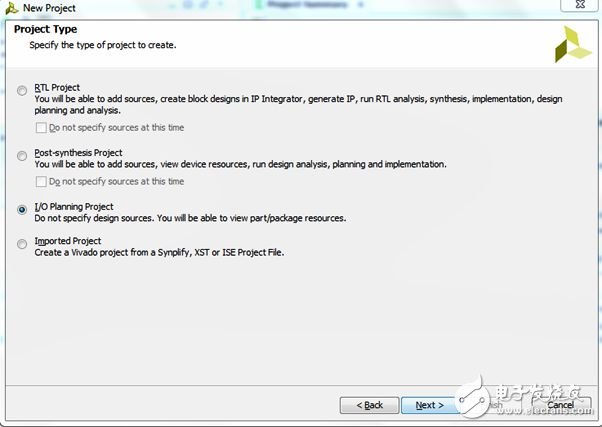

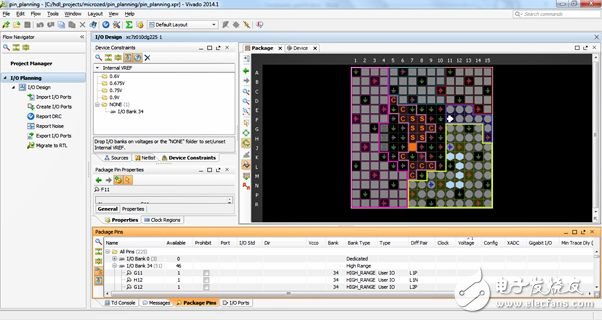

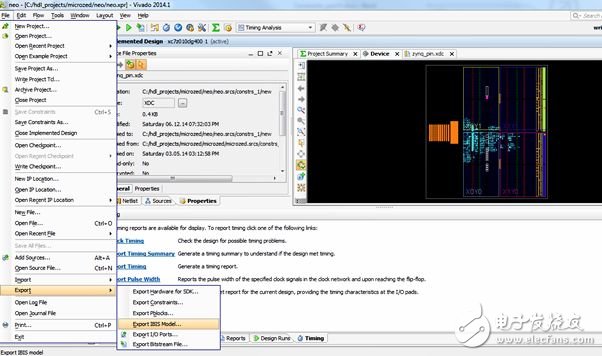

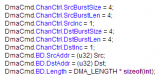

[get_ports {data_out[0]}]set_propertyIOSTANDARD LVCMOS33 [get_ports {data_out[0]}]也可在综合之后,打开右上角小窗口,选择I/O Planning进行约束。

2018-09-21 13:17:37

1. 单元布局约束set_property BELGTHE2_CHANNEL[get_cellsswitch_v2_i/srio_0/srio_gen2_0_inst

2018-09-26 15:32:20

进行约束。set_property BITSTREAM.CONFIG.CONFIGRATE 12 [current_design]set_property CONFIG_VOLTAGE 1.8

2018-09-21 13:12:24

趋势——物理尺寸减小,更多的集成——具有同等吸引力,但并不总是相辅相成。嵌入式应用程序开发人员的挑战是挑选正确的产品,以适应其物理体积和计算方面的约束。 图1:空间受限的工业无线传感器节点 MSP432

2019-03-21 06:45:10

TD 软件的物理约束功能通过 ADC 文件除了基本的管脚约束以外还可以对布局布线进行约束。不仅可以对 SLICE, PLL,DSP,ERAM 等单元的物理位置约束,还可以对代码中的模块进行布局布线

2022-10-27 06:28:51

/Adam-Taylor-s-MicroZed-Chronicles-Part-108-Creating-our-)中描述的方法进行操作。硬件/ ba-p / 665756)但我无法弄清楚HSI是什么或如何打开SDSoC提示。我只需要一个可以在SDSoC设计中使用的ADC。必须有一个更容易/更好的方法来做到这一点,但我会接受任何有效的方法!请帮忙。

2020-05-25 08:18:59

本视频是MiniStar FPGA开发板的配套视频课程,主要通过工程实例介绍Gowin的物理约束和时序约束,课程内容包括gowin的管脚约束及其他物理约束和时序优化,以及常用的几种时序约束。 本

2021-05-06 15:40:44

74LS系列芯片有哪些型号?74LS系列芯片的功能有哪些?

2021-08-20 06:47:20

想买个二手STM8S系列开发板,已经玩转了的希望转手给我,价格请加Q1922234601详谈。

2016-08-12 15:23:27

如何玩转STM32-F429系列

2021-10-13 06:45:39

如何玩转STM32-F429系列控制器?

2021-11-12 06:06:38

如何玩转STM32?

2022-01-20 07:11:33

如何玩转ZigBee?

2021-05-13 06:16:59

/Adam-Taylor-s-MicroZed-Chronicles-Part-180-All-about-the-Xilinx/ba-p/756988但该芯片自带板,Zynq 7020属于Zynq家族。是否可以在电路板上使用它?如果没有,支持reVision的官方(Xilinx / AVNet / ...)主板的最低成本是多少?筹码怎么样?

2019-10-10 06:25:58

如何轻松玩转adc?

2022-01-21 06:28:29

如何零死角玩转STM32-F429系列

2021-10-13 08:47:02

如何零死角玩转STM32-F429系列?

2021-10-12 07:43:14

我昨天才发现我的两块microZED板都有相同的MAC地址(第一次将它们同时插入网络)。通过u-boot代码,我看到MAC地址被烘焙到环境中(在zync_common.h中)。#define

2019-09-16 14:57:55

物理约束文件ADC可做哪些约束?

2023-08-11 08:37:29

常用74系列,74LS,74HC系列逻辑门电路

2009-08-06 08:42:36 491

491 研华科技近日发布新型工业级以太网远程I/O模块ADAM-6100系列。此系列包括6个支持Ethernet/IP协议的ADAM模块和6个基于PROFINET的ADAM模块

2011-08-29 09:16:38 1026

1026 74系列芯片总汇(237种)74系列芯片总汇(237种)74系列芯片总汇(237种)74系列芯片总汇(237种)74系列芯片总汇(237种)

2015-12-28 15:27:34 26

26 By Adam Taylor 到目前为止的文章中,我们已经研究了MicroZed开发板上使用以太网的数据传输问题。我们还没有涉及片上外设通信的问题:实时时钟,非易失内存以及独特的传感器。这些通信涉及到I2C或者SPI总线。

2017-01-13 11:07:11 748

748 在Adam Taylor玩转MicroZed系列的前期部分中,我们介绍了IP栈的概念。(见Adam Taylor玩转MicroZed系列第79部分:Zynq SoC以太网第3部分)接下来就是在我们的设计中使用该协议栈了。SDK开发环境允许我们创建BSP的时候包含一个轻量级的IP栈(lwIP)。

2017-01-13 11:17:11 1033

1033

By Adam Taylor 在本系列博客的前两部分中,我们研究了带有Zynq SoC PS(处理器系统)的以太网MAC(介质访问控制层),包括深入探讨了一个MAC使用范例。以太网MAC是一个基础的构建模块,它允许我们实现一个IP栈,然后因此给我们的工程创建联网条件。

2017-01-13 11:24:11 669

669 By Adam Taylor 在约束系列的最后,我们讲讲关联布局宏(RPM)的约束。RPM允许你在FPGA的布局中将DSP、FF、LUT和RAMS等资源组合在一起。与PBlocks不同,RPM并不

2017-11-10 14:49:02 748

748 By Adam Taylor 在过去一周中,我接到了很多不同人的来信,他们正在使用以Zynq为基础的开发工具。他们非常想知道怎么样去把MicroZed系列博客教程应用到他们所选择的硬件平台上。加上

2017-02-08 02:12:49 426

426

By Adam Taylor 在先前的博客中我们研究过I/O约束,下一个合乎逻辑的步骤就是研究如何在我们的设计中用FPGA进行放置和布线约束。使用放置约束的原因如下:为了帮助实现时序,或者

2017-02-08 02:22:11 238

238 By Adam Taylor 在最近的几篇博客中,我们研究了基本的时序约束。那么在设计中我们现在应该能定义时钟了,并且可以创建和声明它们的关系,还应该能在时钟和系统中声明任何缺陷。作为系统设计工

2017-02-08 03:13:11 256

256

By Adam Taylor 在之前的博客中介绍了Vivado的基本时序约束,时序约束定义了系统频率或自己所定义的时钟频率。为建立良好的时序约束,下一步是需要建立时钟路径之间关系的定义。这样

2017-02-08 03:46:35 194

194 通过前面的学习,我们已经对Zynq系列的PL和PS部分已经有了相当多的了解。其中有关约束的部分我们曾经提到过但是没有重点关注。约束可以添加特定的信息到你的设计,并在综合工具和实现工具中可以得到实现

2017-02-08 03:58:43 645

645

上周的博客中我们完成了硬件的搭建,并且把硬件部分导入到SDK,见Adam Taylor’s MicroZed Chronicles Part 67: AXI DMA II,下一步通过写一个简单的程序

2017-02-08 05:53:11 303

303

上周的博客中我们学习了Zynq SoC的AXI DMA,我解释了怎样利用AXI DMA控制器将数据从PL搬运到PS。在本期博客中我们将学习怎样完成硬件的搭建。 首先我们要更深入的了解一下AXI streaming接口。Vivado工具的AXI参考手册(用户手册1037)对我们是非常有帮助的,提供了关于Zynq SoC的AXI协议的详细信息,为了构建硬件我们将使用如下AXI协议: AXI4-Stream—使用DMA时,从Zynq SoC的XDAC流式接口到内存映射,提供高性能输出 AXI4-Lite —配置和控制XADC以及DMA控制器 AXI4 —配置

2017-02-08 08:10:39 286

286 在我最新一期发表的博客中介绍了如何通过Zynq PS(处理器系统)内部的AXI总线接口寻址Zynq SoC的XADC模块以及如何调试与分析你的应用程序。但是我们仍然没有看到Zynq SoC的一个非常有意思的方面,就是它能够将数据从PL(可编程逻辑)部分移动至存储器中——例如片上存储器或者DDR SDRAM,而存储器是映射到PS的地址空间上的。 作为工程师我们一直想这样做,将在Zynq PL部分实现的硬件存储器映射到PS部分的地址空间中,这是非常有用的,因为这样做可以允

2017-02-08 08:14:11 153

153

在本系列上一篇博客中,我们学习了解了使用XMD和XSDB来调试我们的应用和系统。然而为了确保我们的应用在性能上是优化的,另一个非常重要的方面就是对应用程序进行详细分析。 分析不同于调试,就分析功能

2017-02-08 09:53:00 130

130 在此系列博客的前面几期中,我们已经可以运行示例应用并获得用于分析的程序运行数据。运行分析器可以生成一个gmon.out格式的文件,它包含了分析数据。当应用程序运行自然结束或者通过SDK来终止应用程序

2017-02-08 09:56:49 180

180

在上一篇的MicroZed系列博客中,我们学习了两种与XADC进行通信的方法:Zynq SoC 的AXI或者DevC接口。通过在每个驱动程序中输出XADC的基地址,我演示了这两种XADC通信方法

2017-02-08 09:58:42 221

221 本周的博客内容将继续学习Zynq SoC的XADC,上周一名读者提出了一个非常有意思的问题,我觉得有必要探究一下这个关于XADC的问题,也有必要中断一下正在进行的关于PicoBlaze处理器的学习讨论,这个问题解决之后我们将回来继续学习PicoBlaze。 前面的博客中提到,有多种方式可以实现XADC与Zynq之间的交互,除了JTAG接口: 1.我们可以借助DevC接口实现XADC与PS(处理器系统)之间的直接交互,使用这种方式时,Zynq SoC的PL(可编程逻辑)部分不需要进行配置。然

2017-02-08 10:04:11 242

242 前面的几篇博客中,我们通过介绍怎样驱动CCD的一些知识了解了PicoBlaze的一些特点,同时也知道了通过Zynq PS(处理器系统)可是实现PicoBlaze的动态可重配置,我觉得在这次博客当中,我应该向大家介绍一下根据CCD的数据说明书怎样怎样创建生成我们第一个驱动CCD的波形信号。 尽管在这次设计中我们要使用两个PicoBlaze处理器,但是在这个例子当中只需要使用其中一个,因为只有四个图像时钟和四个寄存器时钟,采用一个PicoBlaze处理器就足以满足需求了。

2017-02-08 11:11:37 134

134 Wind River的 Pulsar Linux操作系统授权镜像。同时, MicroZed IIoT包含了一个可和Watson IoT通信的MQTT消息协议设计样例,可以提供注册、安全连接到云服务和包括IBM Bluemix 在内的应用。IBM Bluemix由一系列丰富

2017-02-08 11:57:12 243

243 作者:Adam Taylor 在上一篇博客中我们已经知道了如何动态更新PicoBlaze的运行程序,现在我们要学习一个完成的设计应用。一个非常相关的应用就是驱动CCD(电荷耦合元件)图像传感器,因为

2017-02-08 12:31:33 144

144 正如我上周所讲,Petalinux是Xilinx针对Zynq SoC提供的Linux官方版本。为了攫取该版本最大资源,我们需要创建自己的版本。这就需要我们在Linux环境下进行开发。现在,并不是所有人都在Linux系统环境下进行开发,然而弄一台新机器又觉得既浪费时间和浪费金钱。因此,我将用一个虚拟机来提供这个环境。我之前采取过类似的方法来使用CERN自由过滤器设计工具,一直使用的不错哦! 我决定使用Oracle VM Virtual Box虚拟机并且创建一个Ubuntu 操作系统。这个非常简

2017-02-08 13:58:08 164

164 如果在我们的虚拟机上已经安装好了SDK,我们就得使用Linux操作系统来建立我们自己的应用程序。这通常需要对 Zynq SoC的硬件重新进行定义。 首先,我们要做的就是确保将VIVADO设计套件以及SDK下载并且安装到我们的虚拟机中。因为我们需要这些工具对Zynq SoC进行硬件定制同时构建软件开发环境。 接下来我们按照下面步骤进行: 1. 按照我们的要求新建一个Zynq 硬件系统,确保我们有下面这些外设: •UART(必须的) •SD 卡配置(可选) •以太网(可选) •

2017-02-08 13:58:11 300

300 我必须承认这是一篇我从来不希望要写的博客。当我开始写玩转MicroZed时,我还不确定每周一篇写到52篇。达到这样的里程碑并拥有150,000的浏览量,我想回顾过去的一年在Zynq SoC上涵盖

2017-02-08 15:35:37 108

108 作者:Adam Taylor 在上一篇博客中我们了解了Zynq SoC的OCM(片上存储器) ,利用它可以实现在AMP模式下内部处理器内核之间的通信。现在我们将写一些程序代码将这个设备(OCM)利用

2017-02-08 15:38:12 606

606 作者:Adam Taylor 在最近的几篇博客中,我们花了主要精力讲解操作系统和AMP(非对称多进程处理),接下来我们希望看到Linux系统在microzed板上运行。我们目前还没有讨论

2017-02-08 15:42:12 529

529

作者:Adam Taylor 上篇博客中我们看到了在ZynqSoC的两块ARM Cortex-A9 MPCore处理器之间共享数据。我提到方法可以改进——使得更加高效——我们可以使用软件中断来进行

2017-02-08 15:47:34 222

222 介绍完操作系统后我将会在Zynq SoC上演示,我打算首先在MicroZed上实现的操作系统就是Micrium公司的uC/OSiii。这是一个硬式实时操作系统,可以点击这里下载。 该OS已经用于大量

2017-02-08 18:26:11 149

149 最近的几篇关于MicroZed系列的博客中我们介绍并了解了RTOS(实时操作系统)的概念,既然已经介绍了基本知识,是时候在MicroZed开发板上实现运行我们的第一个操作系统。我们将使

2017-02-08 18:27:06 323

323

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 在我前面的一篇博客(查看Adam Taylor玩转MicroZed系列40:MicroZed操作系统第二部分)中,大家已经见识

2017-02-08 18:27:11 202

202 我本来打算在这篇博客中继续介绍探讨运行于Zynq SoC上的操作系统。然而由于上周有人提问过一些关于Zynq SoC外设XADC,中断和alarms的问题,我认为我们应该快速的了解一下以及我们怎样将它们加入到系统设计中。 Zynq SoC具有检测供应电压和片上工作温度的能力,这看起来非常有趣 。我们可以利用这个功能在系统测试期间验证初始供应电压和工作温度。在我们的设计的整个测试和运行期间,我们可以定期的检查确保这些参数保持在规定的运行范围内。在

2017-02-08 18:30:02 312

312

在这期博客前面的几期,我们介绍了驱动Adafruit Neopixels设计实例的解决方案架构。我们使用Vivado方块图设计这个解决方案(具体可以查看Adam Taylor玩转MicroZed系列

2017-02-08 19:05:11 281

281

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 By Adam Taylor 我们采用基于Zynq的MicroZed板来实现Adafruit NeoPixel驱动器,前后花了

2017-02-08 19:06:11 152

152 到目前为止,我们已经从Zynq/MicroZed系列博客中看到了很多设计的例子,但是这些设计都没有使用到操作系统。裸板系统对于目前我们博客中涉及到的例子已经足够满足设计要求了,但是如果我们想使用更加

2017-02-08 19:09:11 111

111 最近我拿到了一块MicroZed I/O 扩展板卡,这个扩展板补充完善了MicroZed系统化模块(SOM)设计方法,通过分解位于MicroZed开发板背面的两个小型的I/O引脚集管上的I/O引脚

2017-02-08 20:20:29 359

359 作者是Adam Taylor,该文章发表在 第87期XCell期刊 上。Adam经常给XCell期刊投稿,在XCell日报上,他的“MicroZed Chronicles”系列文章已经发表了近30期,最近他成为了e2v科技的系统工程主管。

2019-10-06 17:09:00 3013

3013

Adam Taylor's博客系列讲解在基于ARM的Zynq SoC芯片可编程逻辑上实现定点数学函数计算。 我们已经在MicroZed 系列的前期博客中学习了在PL(可编程逻辑)内实现定点运算,现在

2017-02-09 02:07:37 210

210

在上一篇博文中,我介绍了让人着迷的Adafruit NeoPixel RGB LED,并且大概描述了NeoPixel驱动设计的基本要点。(参见” 亚当泰勒玩转MicroZed连载31:系统模块驱动

2017-02-09 03:41:03 280

280

。 与我们在本博客系列中的方法一样:加上所生成的头文件作为BSP的一部分。这些头文件提供了宏和函数,我们可以用来驱动DMA 。我们将在这个示例中加入: Xscugic.h和xil_exceptions.h

2017-02-09 05:47:33 211

211

Adam Taylor's博客系列讲解基于ARM的Zynq SoC芯片可编程逻辑实现定点算法以提高性能。 这个博客系列每周发布,迄今为止已经发布了6个月,我们在Zynq SoC处理器系统(PS

2017-02-09 07:58:12 193

193 了解Zynq PS / PL接口之后;到目前为止,我们已经分析了Zynq All Programmable SoC芯片中的PS (处理器系统)与PL(可编程逻辑)之间的接口。

2017-02-10 12:00:11 957

957

我们先来了解一下上节中介绍的Zynq SoC PS/PL接口,我创建一个很简单的外设,使用的是DSP48E1的DSP逻辑片,依靠这个外设第一个寄存器内的控制字执行乘法,加法或减法。

2017-02-10 12:04:41 469

469

到现在为止,我们知道如何在基于Zynq SoC的系统中例化PicoBlaze 软核处理器。在这篇博客,我们将继续探索更多关于如何生成PicoBlaze 程序以及如何使用JTAG接口更新程序而不是重新编译整个设计。

2017-02-11 07:01:06 926

926 Zynq SoC的处理系统提供额外功能让我们可以建立一个更加灵活的Zynq 程序下载系统以适应更多工作。

2017-02-11 07:03:11 1053

1053

在以前发布的玩转MicroZed系列博客中,我们建立了一个基于Zynq的系统,通过使用双端口RAMS和BRAM(块RAM)控制器将两个PicoBlaze处理器核连接到Zynq的PS部分,现在我们将学习一下怎样实现更新存储在双端口RAM中的PicoBlaze处理器的程序。

2017-02-11 07:05:11 943

943

如何获得FreeRTOS演示并且在MicroZed上运行。FreeRTOS由Real Time Engineering公司开发,为小容量和极快运行速度的嵌入式系统提供帮助。

2017-02-11 10:03:12 1513

1513

在上一篇博客中成功地演示了FreeRTOS并在基于Zynq的MicroZed板上运行之后,显然我们想要能够编写我们自己的应用程序。因此,我们将首先举一个简单的例子。我们将配置Zynq SoC的XADC并且在串行链路上输出结果。

2017-02-11 10:03:13 1019

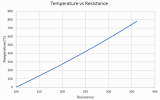

1019 基于研华ADAM模块的温度测量系统设计

2017-04-20 11:33:27 14

14 玩转西门子S7-300系列PLC的PID

2018-03-21 10:46:53 8753

8753 ADAM是全球无数专业录音室的选择,如今任何人都能轻易获得传奇的ADAM声音。

2018-05-31 08:54:56 9548

9548 观看视频,了解和学习有关XDC约束,包括时序,以及物理约束相关知识。

2019-01-07 07:10:00 5510

5510

Adam Taylor讨论了使用Zynq®和Zynq UltraScale +™SoC开发图像处理应用程序时学到的一些技巧

2018-11-30 06:37:00 2023

2023 本文档的主要内容详细介绍的是ADAM-4510I RS-422/RS-485宽温中继器和ADAM-4520I RS-232至RS-422/485宽温转换器及ADAM-4117带Modbus的8通道模拟输入模块技术数据资料免费下载

2019-01-15 08:00:00 38

38 使用Avnet MicroZed载板套件开发的原型将MicroZed系统级模块(SOM)与Arduino屏蔽的大型生态系统相结合,可用于工业控制,遥感,嵌入式视觉和许多其他物联网系统

2019-08-12 09:51:18 2131

2131 引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2021-04-27 10:36:59 3126

3126

《零死角玩转STM32》—F1系列pdf

2021-12-07 18:12:17 0

0 电子发烧友网站提供《Gowin设计物理约束用户指南 .pdf》资料免费下载

2022-09-15 16:07:35 0

0 概述 对设计中的信号施加DONT_TOUCH约束,可以避免这些信号在综合编译过程中被优化掉。例如,有些信号节点在综合或布局布线编译过程中可能会被优化掉,但是我们希望在后期调试过程中能够监控到这些

2022-11-12 14:14:52 1946

1946 约束文件是FPGA设计中不可或缺的源文件。那么如何管理好约束文件呢? 到底设置几个约束文件? 通常情况下,设计中的约束包括时序约束和物理约束。前者包括时钟周期约束、输入/输出延迟约束、多周期路径约束

2022-12-08 13:48:39 879

879 的数据交换可靠?如何使用I/O逻辑单元内部的寄存器资源?如何进行物理区域约束,完成物理综合和物理实现?为了解决大家的疑难,我们将逐一讨论这些问题。(注:以下主要设计时序约束)

2023-05-29 10:06:56 372

372

电子发烧友App

电子发烧友App

评论