FIR IP 用户手册 FIR(Finite Impulse Response),有限冲击响应滤波器,是数字信号处理里面常用的滤波器类型。

2023-08-09 06:56:01

AD采集为14位,但是在FIR IP核中将输入位宽设置为14位,IP核数据输入端依然为16位。在之后的仿真阶段会报位宽不匹配的ERROR,请问应该怎么才能把FIRIP核输入改为14位。或者怎么才能不报错

2016-09-07 10:32:22

本帖最后由 eehome 于 2013-1-5 09:59 编辑

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改

2011-07-06 14:15:52

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动。随着CPLD

2011-07-15 14:46:14

你好,我在使用Xilinx网站的IP核时遇到了一些问题。我已经下载了Vivado Webpack,也为此同时下载了IP-Core的许可证。Vivado Webpack工作正常,但我看不到我下载

2018-12-24 13:50:01

发生IP核锁定,一般是Vivado版本不同导致的,下面介绍几种方法: 1 常用的方法 1)生成IP核的状态报告 Report -》 Report IP Status 2)点击

2021-01-08 17:12:52

Vivado中xilinx_courdic IP核(求exp指数函数)使用

2021-03-03 07:35:03

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

,用户设置的调试信息会以Tcl XDC调试命令的形式保存到XDC约束文件中,在实现阶段,Vivado会读取这些XDC调试命令,并在布局布线时加入这些ILA IP核。此时,我们所做出的所有的更改和设置,都还

2023-04-17 16:33:55

,int b);最后经过编译可以生成VHDL等硬件描述文件与IP核文件.我想调用自己写的IP核(add函数)我在vivado 中添加了自定义IP核与PS(处理系统)我知道网上说用AXI Steam? 来连接

2016-01-28 18:40:28

,int b);最后经过编译可以生成VHDL等硬件描述文件与IP核文件.我想调用自己写的IP核(add函数)我在vivado 中添加了自定义IP核与PS(处理系统)我知道网上说用AXI Steam? 来连接

2016-01-28 18:39:13

大家伙,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。首先咱们来了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-15 12:05:13

vivado的三速以太网IP核接口太多了,完全不知道应该怎么用,哪位大佬能发我一份设计或者仿真吗?简单的就好

2021-04-15 12:58:00

请教一下,vivado怎么把带ip核的工程进行封装,保证代码不可见,可以通过端口调用。我尝试了以下方法,ippackage,如果要在另一个程序里调用,也要提供源代码;另一个方法是将网表文件edf文件与端口声明结合,这种方法只能实现不带ip核的封装

2017-07-14 09:18:30

vivado三种常用IP核的调用当前使用版本为vivado 2018.3vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点

2021-07-29 06:07:16

将程序从低版本的vivado搬移到高版本的vivado的时,直接在高版本的vivado下升级软核中的各个IP后,在综合过程中报错。在低版本的vivado平台下,原程序已经完成编译。

2020-11-14 20:57:13

在vivado生成ip核后缺少一大片文件,之前都是正常的,杀毒软件也一直没有开,突然就变成这样了,还请大神告知是怎么回事?

2021-05-18 20:34:08

BRAM IP核包括哪几种类型?Vivado中xilinx_BRAM IP核怎么使用?

2021-03-08 07:11:54

Gowin Advanced FIR Filter IP用户指南主要内容包括功能简介、信号定义、端口描述、时序说明、配置调用、参考设计等。主要用于帮助用户快速了解 Gowin Advanced FIR Filter IP 的产品特性、特点及使用方法。

2022-10-09 06:53:54

本次发布 Gowin Basic FIR Filter IP 用户指南。Gowin Basic FIR Filter IP 的用户指南及参考设计可在高云官网下载,其中,参考设计已配置一例特定参数,可用于仿真以及综合、布局布线后下载测试。

2022-10-09 06:00:17

很多人都说QUARYUSII中的IP核是收费的,不可以直接用的,其实不然,下面我以FIR滤波器的核的使用来给大家介绍IP核的使用,希望对大家有点帮助。 1.使用 (1)首先建立工程,这个就不

2019-06-03 09:09:51

请问一下,我使用QuartusII 13.0 生成不了Rapid IO IP核,iP核已破解,其他诸如FIR、CIC、NCO等都能正常生成,到底是怎么回事呢?是Quartus版本的问题吗?

2017-07-17 16:23:29

最近在使用altera的FIR IP核做半带滤波器,quartus ii软件也破解了,firIP核也破解了,modelsin仿真也通过了,但是下载不了.sof文件到开发板,大家有用FIR IP核成功实现下板的经验吗,求大神指点呀。谢谢!

2018-05-11 16:01:15

振动数据,想实现从等时间间隔采样到等角度采样,labview怎样实现等角度重采样,有具体算法吗?谢谢啦,声音与振动的工具包我也下了。

2016-04-20 22:47:31

testbench进行仿真分析,预计第五讲或第六讲开始编写verilog代码设计FIR滤波器,不再调用IP核。这的图发不出来。1. 添加DDS的IP核(1) 新建一个原理图文件,添加DDS的IP。(2) DDS

2020-01-18 22:05:50

各路大神,我想问一下,11.0的quartus里的FIR各个参数怎么设置,比如我要设置一个8位输入的FIR滤波器(阶数什么的已经在matlab里面生成),我记得有选项是选input width的,选

2013-08-30 11:51:48

D9B8 5C3A B8E8 4E4F CEC7 C836"其中6AF7_0012 是FIR ip核的特征码,然后tools->options->license setup中就

2016-05-19 14:13:09

quartus II 13.1调用FIR 这个IP核生成时一直卡着,怎么解决? 系统版本是win7 64位 专业版,我试过网上说的①在license中改相应IP核的序列号②在任务管理器中关闭

2017-08-08 11:42:19

请教各位大师,quartus ii 中调用fir数字滤波器IP核,可不知道如何设置参数,比如如何设置滤波器的系数

2013-11-23 20:54:41

quartus ii中的fir Ⅱ核的可重构滤波器和双通道的程序应该如何写,请问大家有这方面的例程吗

2017-09-26 16:05:55

用vivado2019.2建立工程,工程中调用cordic IP核进行atan求解,功能仿真时正常且满足要求;综合时正常;实现时报错提示多重驱动。

如果经cordic计算后的输出值不用于后续的操作

2023-06-06 17:17:37

为什么vivado2016调用MIG ip核会收到严重警告呢?这个critical warning会有影响吗,要怎么解决呢?

2021-10-18 09:41:21

本例程主要使用Vivado 调用ROM IP核,用含有正弦曲线的.coe文件初始化ROM,最终通过仿真实现波形的显示 一、首先建立工程 二、选择芯片的型号 我

2021-01-08 17:16:43

我们使用quartusII的fir ip核生成了一个滤波器,用AD采集了单频正弦信号输入,可是不管输入频率多少,滤波器的输出端口都没有输出,不知道这是为什么啊?

2013-08-12 22:49:58

请问我修改完MIG IP核以后,该如何进行更新呢?捣鼓了半天,要么更新为源代码,要么就是提示我自己添加的端口不存在

2018-11-12 19:46:15

如图,这个是我用FIR COMPILER 生成IP核生成的文件,这里想请教一下,这里面的各个文件都是干嘛的,顶层文件到底是哪个?

2018-04-14 17:15:32

请问有哪位大神,可以帮忙破解一个vivado的IP核。不胜感激,联系QQ397679468

2017-11-24 09:30:30

有找到关于添加IP的文章A simple BBP for RF Transceivers [Analog Devices Wiki] 我想直接使用Xilinx的IP核,但是vivado建立的IP核

2018-08-13 08:03:00

最近在做一个FIR低通滤波器,利用Matlab 产生滤波系数,导入到Quartus中,再利用其中的FIR IP核进行滤波器设计,在采用分布式全并行结构时,Modelsim 仿真有输出;如果改为分布式

2018-07-05 08:33:02

最近进行FPGA学习,使用FIR滤波器过程中出现以下问题:使用FIR滤波器IP核中,输入数据为1~256,滤波器系数为,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

%91/vivado2016-%E8%B0%83%E7%94%A8MIG-ip%E6%A0%B8%E4%B8%A5%E9%87%8D%E8%AD%A6%E5%91%8A-Project-1-19/m-p/884989链接不管用的话就按照下图自己找吧。回复: vivado2016 调用MIG ip核

2021-07-28 07:16:27

嗨,我在使用Vivado 2015.2.1中的FIR comipler v7.2 IP时遇到了有意义的响应我已经设置了一个非常简单的块设计来检查冷杉响应:shift_ram,16位宽,16位深,配置

2020-04-09 08:07:16

Programmable Gate Array,现场可编程门阵列)基于查找表的结构和全硬件并行执行的特性,如何用FPGA 来实现高速FIR 数字滤波器成了近年来数字信号处理领域研究的热点。目前,全球两大PLD 器件供应商都提供了加速FPGA 开发的IP(IntelligentProperty,知识产权)核。

2019-09-05 07:21:15

Viterbi译码的基本过程,接着根据Viterbi译码器IP核的特点,分别详细介绍了并行结构、混合结构和基于混合结构的增信删余3种Viterbi译码器IP核的主要性能和使用方法,并通过应用实例给出了译码器IP

2010-04-26 16:08:39

在通信、图像处理、模式识别等领域都有着广泛的应用。Vivado集成的FIR IP核可以实现如下公式所示的N级卷积运算。 FIR IP核可以根据配置实现复用的乘累加单元,以实现面积最优化的设计;当然了

2019-07-16 17:24:22

基于FPGA的IP核8051上实现TCPIP的设计

2012-08-06 12:18:28

飞舞,这里就不赘述了,以免有凑字数的嫌疑。下面我们就Matlab和FPGA两个工具双管齐下,比对Vivado的FFT IP核生成的数据。2 Matlab产生测试数据,绘制cos时域和频域波形

2019-08-10 14:30:03

当我们通过IP目录在Vivado中创建一些IP内核时,将使用xdc文件生成一些内核。在这个xdc文件中,它包括时序或物理约束。以DDR3控制器为例,用核心生成xdc文件。它包括时序约束和物理约束

2019-03-26 12:29:31

嗨,我正在尝试学习如何使用System Generator来创建自己的IP核。首先,我在DocNav中找到了一个ug948-vivado-sysgen-tutorial文档。我在哪里可以找到本文档中描述的示例?我在安装目录中的“examples”文件夹中找不到完全相同的示例。提前致谢马丁

2020-05-22 07:22:09

我正在尝试将Xilinx MIG IP Core从1.7版升级到1.9版。 Coregen UI左侧有一个方便的“升级IP核”按钮,但它显示为灰色。我需要做什么才能进行IP核升级?我在Kintex

2019-11-04 09:26:19

型结构FIR,实现时可以采用并行结构、串行结构、分布式结构,也可以直接使用Quartus和Vivado提供的FIR IP核。本篇先介绍并行FIR滤波器的Verilog设计。设计参考自杜勇老师

2020-09-25 17:44:38

怎么利用赛灵思FGPA实现降采样FIR滤波器?这种滤波器在软件无线电与数据采集类应用中都很常见。

2019-08-15 08:21:22

是对的,请纠正我,但我认为这一步只需按一个按钮)3 - 将IP内核导入Vivado并: a-生成块设计(这是我最不舒服的步骤,我会很高兴获得一些好的建议,因为算法很复杂且IP核不是基本的) b-合成,实现

2020-03-24 08:37:03

嗨,我想创建一个设计,我需要2Mhz clk,我想用16Mhz输入时钟的vivado套装中的“时钟向导”IP核生成它。根据Xilinx手册(下面的链接),这可以通过CLKOUT4_CASCADE选项

2020-07-27 06:32:48

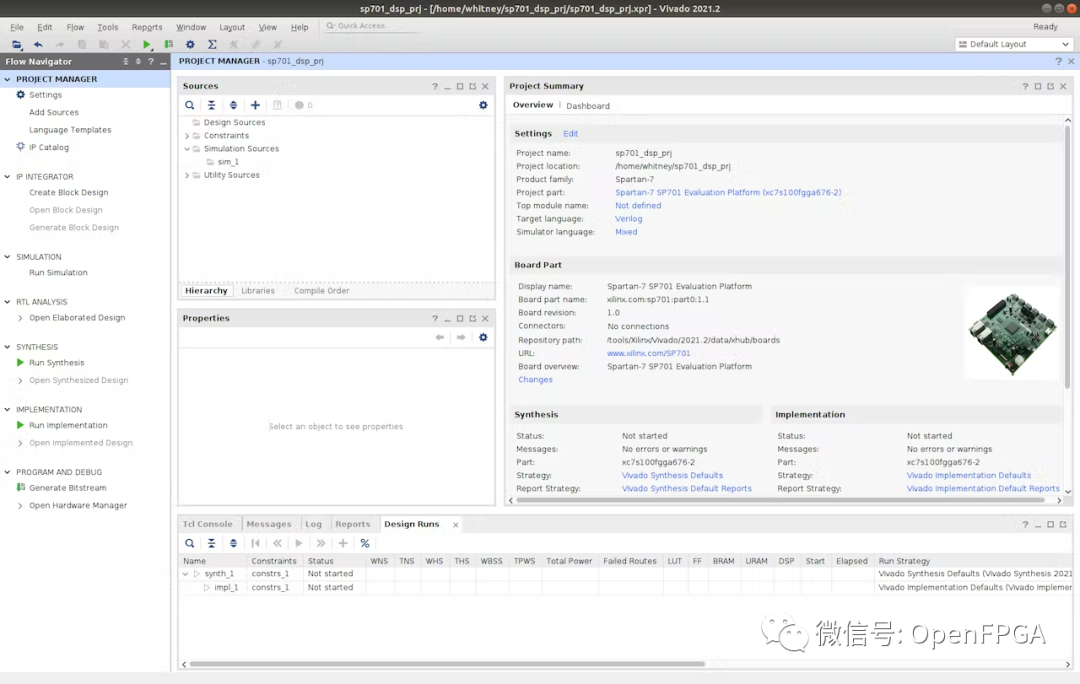

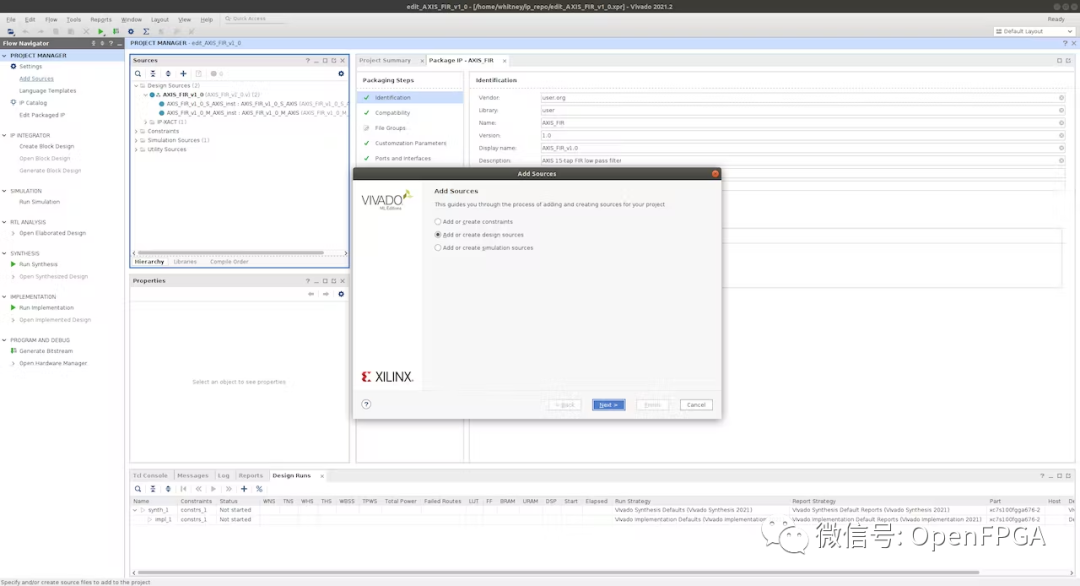

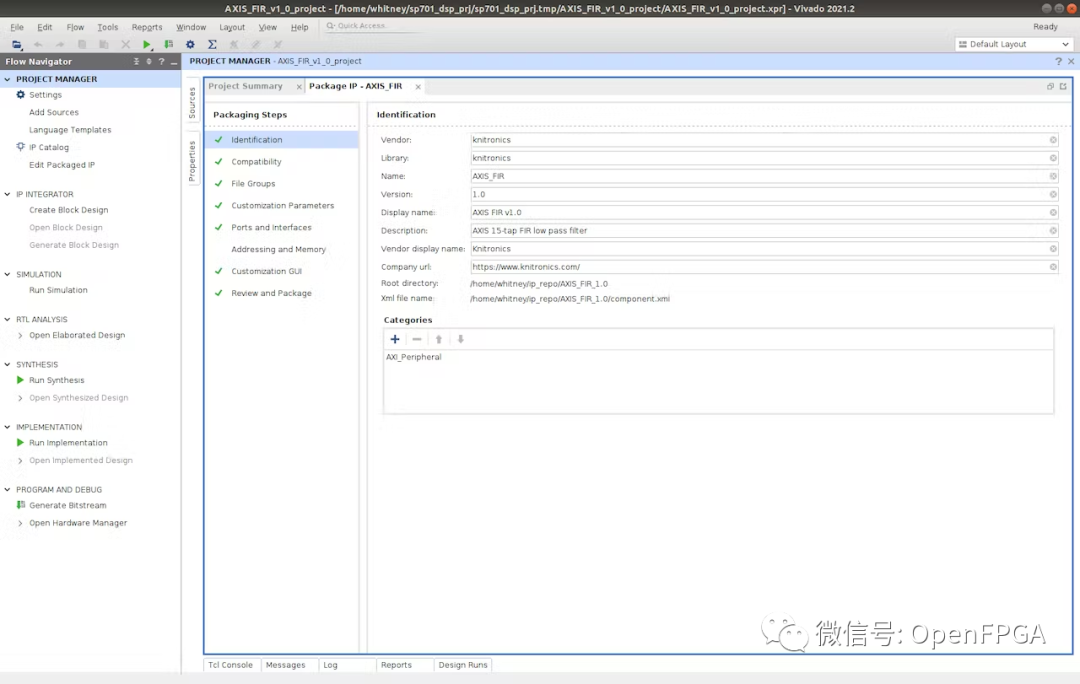

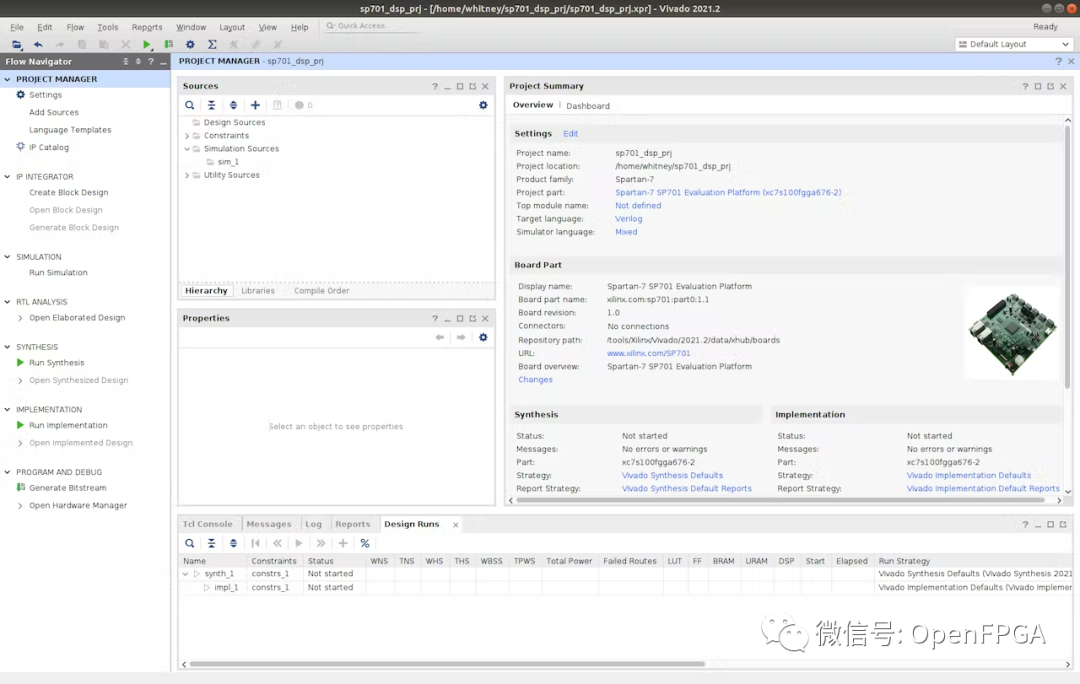

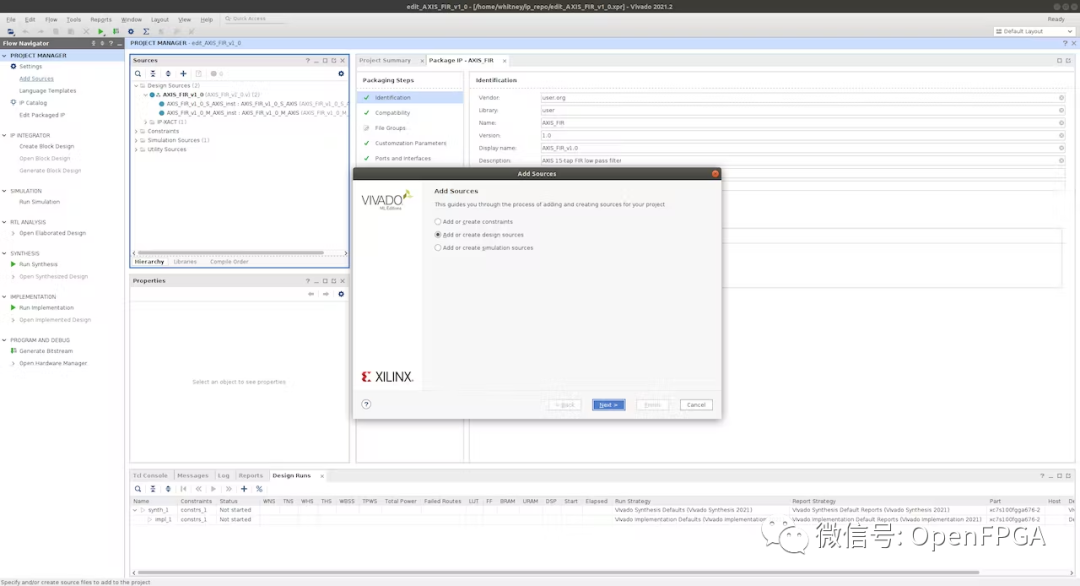

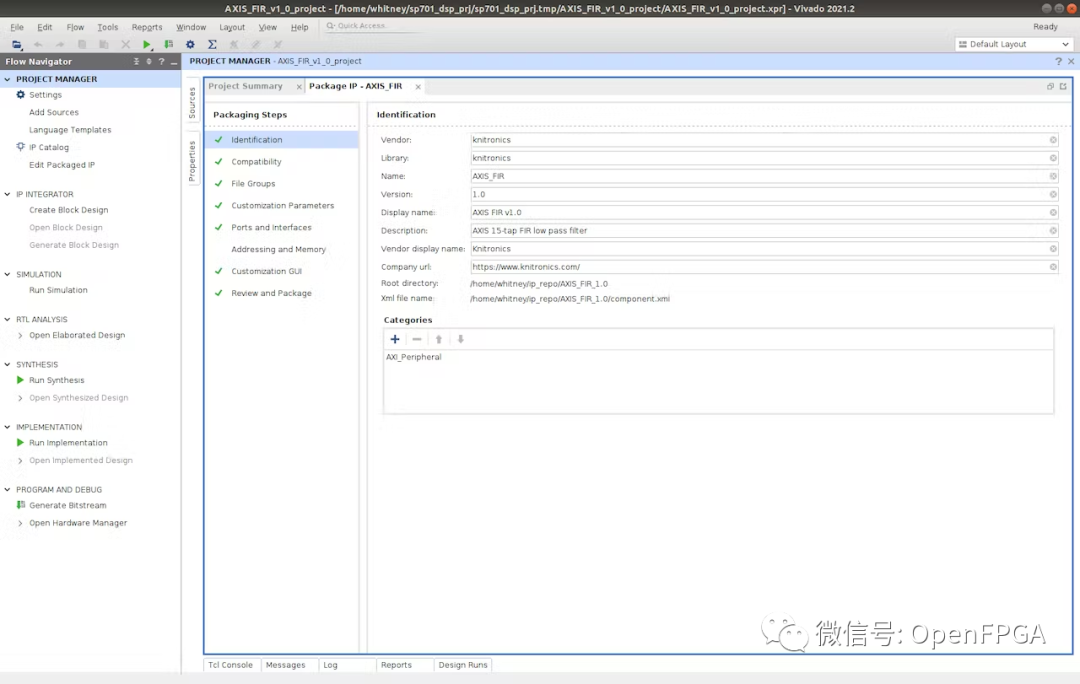

1、构建自定义AXI4-Stream FIR滤波器 AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程

2022-11-07 16:07:43

使用的是Vivado,希望使用其FIRIP核设计一个滤波器,该滤波器不是固定结构,而是可以根据项目中的变量filterselect的值选择其通带频率,例如filterselect=0,1,2,3

2017-08-10 05:49:04

目前在项目中准备使用ad7616芯片并已购买,但在FPGA的使用过程中出现了一些问题,我使用了github上的hdl核(hdl-2016_r2),但是当我在xillinx vivado2016.2中

2018-07-31 09:47:33

`玩转Zynq连载21——Vivado中IP核的移植更多资料共享腾讯微云链接:https://share.weiyun.com/5s6bA0s百度网盘链接:https://pan.baidu.com

2019-09-04 10:06:45

Vivado的FFT IP核生成的数据。 2 Matlab产生测试数据,绘制cos时域和频域波形使用projectzstar_ex67matlab文件夹下的Matlab源码fft_1line.m,运行产生1组

2020-01-07 09:33:53

具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。Vivado集成的FIR IP核可以实现如下公式所示的N

2020-01-14 09:39:45

试着做电设09年的F题呢,做了个FIR,效果还行。菜鸟一个,发上来,闹着玩,挣个积分。大哥大姐们看看,当个趣事乐乐。

2013-08-16 13:22:45

我用MATLAB设计好单位增益的滤波器系数,然后导入 FIR 的IP核里面,系数转换成定点数了,但是此时显示的滤波器幅频特性曲线却是100dB的放大倍数,求问怎么让其变成单位增益?

2018-01-27 13:53:00

大家伙,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。首先咱们来了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-16 11:42:55

你好,我希望实现带可变带宽的带通滤波器(如16k,32k,64k等)。我有各种带宽的滤波器系数。我有Vivado 2015和FIR编译器v7.2。我希望将多频段BPF协方系数用于单个IP。请指导构建此类过滤器所需的各个步骤。谢谢。

2020-05-07 08:24:48

(Intellectual Property)核。IP核由相应领域的专业人员设计,并经反复验证。IP核的拥有者可通过出售IP获取利润。利用IP核,设计者只需做很少设计就可实现所需系统。基于IP核的模块化设计可缩短

2019-07-29 08:33:45

基于FPGA实现变采样率FIR滤波器的研究

2017-01-08 15:59:09 19

19 。如果你懂得最后一句话,你会很高兴可以学到现在在赛灵思System Generator的最新发布中有一个可配置的超级采样FIR滤波器,可以在最近的Vivado 2014.3 release中找到。 原文链接: © Copyrig

2017-02-09 08:10:11 561

561

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP

2020-12-29 15:59:39 9496

9496 Xilinx FIR IP的介绍与仿真 1 xilinx fir ip 简介 1)符合 AXI4-Stream 的接口 2)高性能有限脉冲响应(FIR),多相抽取器,多相内插器,半带,半带抽取

2020-10-30 12:29:01 511

511 AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程。Vivado 中的block design是使用RTL IP形式

2023-02-10 14:50:57 747

747

AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程。Vivado 中的block design是使用RTL IP形式

2023-02-10 14:51:14 1581

1581

AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程。Vivado 中的block design是使用RTL IP形式

2023-02-10 14:51:19 735

735

在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 1240

1240

在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-20 14:23:57 622

622

Vivado IP核提供了强大的FIFO生成器,可以通过图形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1628

1628

FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

2023-08-29 16:41:49 2605

2605

Vivado是Xilinx公司2012年推出的新一代集成开发环境,它强调系统级的设计思想及以IP为核心的设计理念,突出IP核在数字系统设计中的作用。

2023-09-17 15:37:31 1060

1060

文章是基于Vivado的 2017.1的版本,其他版本都大同小异。 首先在Vivado界面的右侧选择IP Catalog 选项。

2023-12-05 15:05:02 317

317

电子发烧友App

电子发烧友App

评论