对于UltraScale/UltraScale+芯片,几乎FPGA内部所有组件都是可以部分可重配置的

2023-12-14 16:16:22 286

286

UltraScale/UltraScale+芯片开始支持BUFG_*、PLL和MMCM出现在动态区,在7系列FPGA中这些时钟资源只能在静态区。

2023-12-21 09:12:13 471

471

采用UltraScale/UltraScale+芯片进行DFX设计时,建议从以下角度对设计进行检查。

2024-01-18 09:27:10 301

301

描述PMP9475 12V 输入参考设计以紧凑高效的设计提供为 Xilinx's Virtex® Ultrascale™ 系列 FPGA 供电时所需的所有电源轨。此设计使用几个 TI 的 PMBus

2018-08-29 08:33:47

in the 16700-series logic analysis system mainframe running operating system A.02.00 or later.

2019-04-16 11:00:16

This service guide applies to a 16910A or 16911A module installed in the 16900-series logic analysis system mainframes.

2019-09-06 06:08:21

Series4的特性

2020-12-23 06:20:12

UltraScale DSP48 Slice架构的优势是什么?UltraScale内存架构的优势是什么?

2021-05-24 06:34:00

什么是闪存的布局指南,如长度要求?我在文档中看不到任何信息:UG583-UltraScale架构PCB设计和引脚规划用户指南_ 1.1谢谢以上来自于谷歌翻译以下为原文What's

2019-04-16 06:06:39

LQW Series spec!!!!!!

2015-06-24 19:35:34

] intr = 'h AA; logic [23:0] addr = 'h FF_FF_FF; } ext; module SU ( output ext extOut

2022-11-10 15:30:43

本帖最后由 一只耳朵怪 于 2018-6-14 09:08 编辑

[tr=transparent]VP868 Dual Kintex UltraScale 6U VPX板卡[/tr][tr

2018-06-13 15:28:00

Xilinx 20nm All Programmable UltraScale产品系列现已面世 Xilinx将业界最大容量器件翻番,达到创纪录的440万个逻辑单元 1. 赛灵思于2013年12月

2013-12-17 11:18:00

描述PMP10555 参考设计提供为移动无线基站应用中的 Xilinx® Ultrascale® 16nm 系列 FPGA/SoC 供电所需的所有电源轨。此设计对内核及两个多输出降压型稳压器 IC

2018-11-19 14:58:25

描述 PMP9408 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨。它利用一个 PMBus 接口来实现电流

2022-09-21 07:56:06

以ZYNQ UltraScale xczu2cg784为例最重要的是参考ug1085的第27页整理如下

2022-01-03 06:07:01

ZYNQ Ultrascale+ MPSOC FPGA教程

2021-02-02 07:53:25

of std_logic_vector(15 downto 0) to integer and then pass it or use it to a VDL module's variable?I tried

2019-04-18 06:30:20

亲爱的大家,我只是想知道如何找到Ultrascale +的PL和PS的地址转换(映射方案到DRAM-我的意思是哪个等级,库等)?

2019-10-16 08:35:37

嗨,我是jongbum。目前,MIG UltraScale DDR4支持最高2级。https://forums.xilinx.com/t5/Memory-Interfaces

2020-04-22 08:36:21

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器 Zynq UltraScale+ MPSoC VCU DDR 控制器是一款专用 DDR 控制器,只支持在 Zynq

2021-01-07 16:02:09

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

2021-01-22 06:29:21

我正在寻找Kintex UltraScale POD12输出Vol / Voh。 DS892表16显示了直流输出电平,但这些值似乎仅用于测量Rol / Roh。我应该使用表9中的LVCMOS12

2020-07-27 14:52:39

Xilinx fpga ultrascale vivado 2016.2该设计利用80%的设备,早期用于路由与合成stratagy- 流动交替可路由性& congestoion扩展逻辑高实现

2018-11-02 11:19:17

嗨,我计划在不久的将来设计一个使用Kintex Ultrascale FPGA的数据采集板。是否有推荐的PROM与Ultrascale FPGA一起使用?谢谢您的帮助!以上来自于谷歌翻译以下为原文

2019-03-14 18:49:15

你好我们正在考虑在我们的新设计中使用Zynq Ultrascale + MPSOC。我们想在我们的电路板设计中加入HDMI接口。 Zynq Ultrascale + MPSOC在PS中有一个

2019-10-14 09:17:03

PADS Logic 教程

包括:· 如何在PADS Logic 中使用工作区(Working Area)。· 如何在PADS Logic 的元件库中定义目标库(Library)。· 如何从库中搜索有关的元件(Part)。· 如何

2007-10-16 13:46:27 0

0 Standalone 1680 SeriesAgilent’s 1680 Series standalone logic analyzers feature a 12.1-inch color

2008-09-08 17:42:32 14

14 WIB200 and AIB220 Series Jumper Settings

WIB200 and AIB200 Series PC/104Plus Card

2009-03-16 09:50:15 2

2 Logic. Consisting of single gate functionspackaged in a 5 pin SOT353 package, PicoGate Logic reducesboard space requirements 10 times

2009-03-30 00:27:28 18

18 The PI74SSTV16857 is a 14-bit stub-series-terminated logic (SSTL_2)registered driver

2009-11-12 14:26:08 15

15 Zelio Logic智能继电器

2009-11-26 11:28:07 16

16 detection unit, voltage reference unit, bias unit, delay unit, and logic circuits. The BM209 series have cell-balance function and high-acc

2009-12-07 14:45:03 29

29 Introduction This Logic Cross-Reference for Buyers, Distribution Specialists and others

2010-07-09 21:19:21 9

9 ABSTRACTTI Little Logic devices are logic-gate devices assembled in a small single-, dual-

2010-07-12 16:41:27 12

12 LCD Module

2010-07-17 20:28:53 10

10 FeaturesThe Agilent W2630 Series DDR2 BGA probes for logic analyzers and oscilloscopes enable

2010-08-01 12:14:42 6

6 PROTEL TO PADS LOGIC (POWER LOGIC)

一:PROTEL TO ORCAD

转换说明:用高板本的ALTIUM DESIGNER6.0(PROTEL DXP2004以上

2008-03-06 15:38:24 1934

1934 什么是Application Logic

英文缩写: Application Logic

中文译名: 应用逻辑

分 类: IP与多媒体

解 释: 一个应

2010-02-22 10:17:18 904

904 正的逻辑探针电路,Logic Probe Plus

This project is based on a probe logic states, capable of measuring levels fr

2010-04-11 09:24:33 2023

2023

The NX8563LA Series is a 1 550 nm Multiple Quantum Well (MQW) structured Distributed Feed-Back (DFB

2011-11-12 18:39:31 15

15 Cirrus Logic(凌云逻辑)是一家卓越的无生产线半导体公司。Cirrus Logic(凌云逻辑)致力于为音频和能源市场开发高精度的模拟和混合信号集成电路。

2011-12-21 16:58:57 3705

3705 Intel 5 Series chipset and Intel 3400 Series Chipeset Datasheet

2015-11-16 11:08:48 35

35 Logic Analyser,好东西,喜欢的朋友可以下载来学习。

2016-02-22 16:07:20 0

0 basic logic cell • multiplexer-based cell • look-up table (LUT) • programmable array logic (PAL

2016-06-16 17:57:46 0

0 logic cells • Strong and weak logic levels • Pushing bubbles • Ratio of logic • Resistance per

2016-06-16 17:57:46 0

0 PADS Logic 基础,感兴趣的小伙伴们可以瞧一瞧。

2016-11-02 19:49:48 0

0 PADS Logic 原理图设计

2016-11-02 19:49:48 0

0 背景: 关于S2C公司,对于做FPGA的人来说可能比较熟悉,特别是近年来S2C和FPGA巨头Xilinx公司有了越来越多的密切合作。S2C公司是业内领先的SoC/ASIC快速原型解决方案供应商,于2003年,由一个来自硅谷的具有丰富的ASCI仿真、FPGA原型设计以及SoC验证技术经验的团队成立于美国加州圣约瑟,从它成立伊始,已经成功地发布了快速SoC原型设计解决方案。

2017-01-13 13:35:11 701

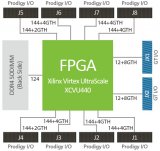

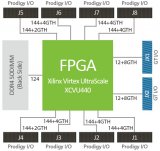

701 Single KU115 Prodigy Logic Module是采用了S2C的第六代原型技术的,基于赛灵思Kintex UltraScale XCKU115 FPGA的SoC/ASIC原型系统

2017-02-08 06:09:11 713

713 片上系统原型的预设计硬件和软件组件已超过90款。这些新的模块允许用户与 S2C 的 Prodigy Logic Module系列组合,进而快速构建其 SoC 验证系统。这些预设计的解决方案,使客户专注于 SoC 原型开发和产品的差异化,从而在当今激烈的市场竞争中获得优势。 “我们为能够提供给

2017-02-08 06:50:11 629

629

S2C的Single VU440 Prodigy Logic Module是基于赛灵思Virtex UltraScale 440 FPGA的业内最小尺寸的、通用的、独立的原型系统。该系统共有1176

2017-02-08 08:07:12 1022

1022

S2C 已宣布推出单个 KU115 Prodigy 逻辑模块。该模块将一个赛灵思 Kintex UltraScale XCKU115 FPGA(以及其他片上资源)与 5,520 个增强型

2017-02-08 12:19:14 884

884 Skyrockets with Xilinxs UltraScale Architecture)(Xilinx UltraScale 架构能够快速提升生产力),下面是我们从Metha的文章中提取出了关于

2017-02-08 12:33:07 495

495 作者:Steve Leibson, 赛灵思战略营销与业务规划总监 想开发一款能在多个地理位置处理任何设计规模的FPGA原型系统么?那么,最好拟定一个大规模的计划方案。S2C新发布的Prodigy

2017-02-09 03:49:04 437

437 Northwest Logic 的 DMA 内核现已支持 Vivado 设计套件中的 IP 集成器工具流。 IP 集成器流可为客户简化将基于 AMBA® AXI4 接口的 IP

2017-02-09 08:12:36 319

319

)440 FPGA的Quad VU440 Prodigy Logic Module。Quad VU440 Prodigy LM是由单板组成的全用途FPGA原型系统,同时Quad VU440 LM的大量的物理互连线以及超大的逻辑容量特别适合超大规模设计,进而减轻了设计分割的负担。

2018-06-29 08:09:00 4932

4932 不知道在什幺时候,Linux 出现了 module 这种东西,的确,它是 Linux 的一大革新。有了 module 之后,写 device driver 不再是一项恶梦,修改 kernel

2017-11-07 11:37:13 0

0 的用武之地。在最新的Ultrascale系列FPGA中,IODelay这一单元的具体用法,跟7Series中相比产生了一些变化。本文总结下,供读者参考

2017-11-16 01:26:01 5512

5512 Dual V7 TAI Logic Module 可在单板上提供高达4000万ASIC门容量以及1,200个外部I/O。而如此高的门容量,使其成为世界上最紧凑的原型验证硬件。

2018-07-02 11:50:00 1269

1269 了解UltraScale DSP架构及其如何帮助降低设计功耗,以及UltraScale时钟架构中的省电功能。

您还将学习估算DSP和时钟的功率......

2018-11-29 06:45:00 2877

2877 Zynq®UltraScale+™MPSoC,现已开始发售。视频向您重点介绍了Xilinx UltraScale +产品组合的第一位成员

2018-11-27 06:47:00 3262

3262 了解Xilinx如何在UltraScale器件中推进其突破性的部分重配置技术。

该视频全面介绍了20nm UltraScale FPGA的新功能,扩展功能和系统要求。

2018-11-26 06:45:00 1988

1988 了解XPE for UltraScale和UltraScale +器件的关键精度改进之一。

从XPE 2015.4开始,将“扇出”逻辑表示替换为“路由复杂度”算法,以解决逻辑与信号之间的功率相关性问题。

2018-11-23 06:00:00 3075

3075 了解如何使用Vivado存储器接口生成器(MIG)创建UltraScale存储器接口设计。

本视频将向您展示如何为UltraScale器件配置MIG IP内核,包括MIG IP I / O的I / O Bank规划。

2018-11-22 07:13:00 2633

2633 了解如何在UltraScale +设计中包含新的UltraRAM模块。

该视频演示了如何在UltraScale + FPGA和MPSoC中使用UltraRAM,包括新的Xilinx参数化宏(XPM)工具。

2018-11-22 05:50:00 7646

7646 23,2016 /PRNewswire/- 基于FPGA的快速原型开发解决方案的领先供应商--S2C,Inc。宣布推出其PCIe VU440 Prodigy Logic Module(LM)的可用性

2019-08-07 16:06:53 4045

4045 S2C公司宣布推出其全新的基于英特尔Stratix 10 GX 10M FPGA的S10 10M Prodigy逻辑系统,其配置包括单颗、双颗以及四颗FPGA。

2019-11-20 11:36:02 2443

2443 了 Xilinx 的 Virtex® UltraScale+™ FPGA,在性能和易用性上也进行了优化。此系列产品具有高比率的 DSP 和内存数量,对于验证高速连接和密集计算应用来说,是理想的原型验证平台。S7系列首先推出的前两款产品是 Prodigy™ S7-9P 和 Prodigy™ S7-13P。

2020-07-13 09:32:30 709

709 Tachyum创始人兼CEO Radoslav Danilak博士说。“Prodigy能够正确运行软件--甚至是x86、ARM或RISC-V处理器的传统代码--的这一演示表明,我们将使客户

2020-08-10 11:52:29 779

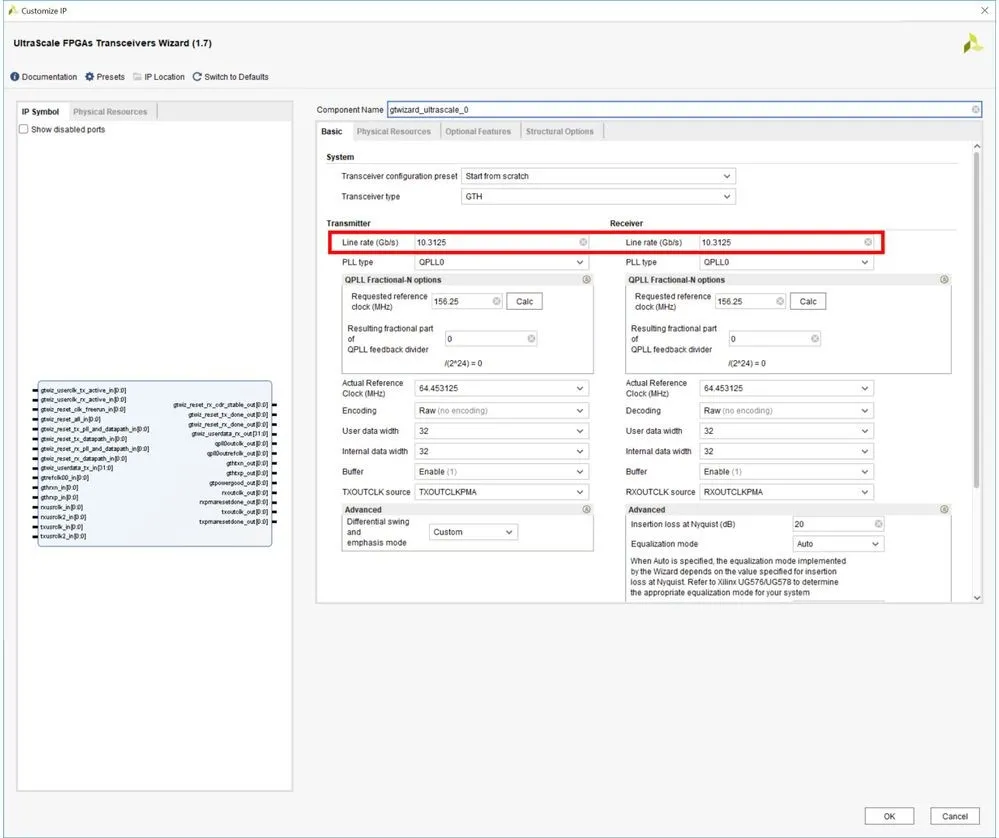

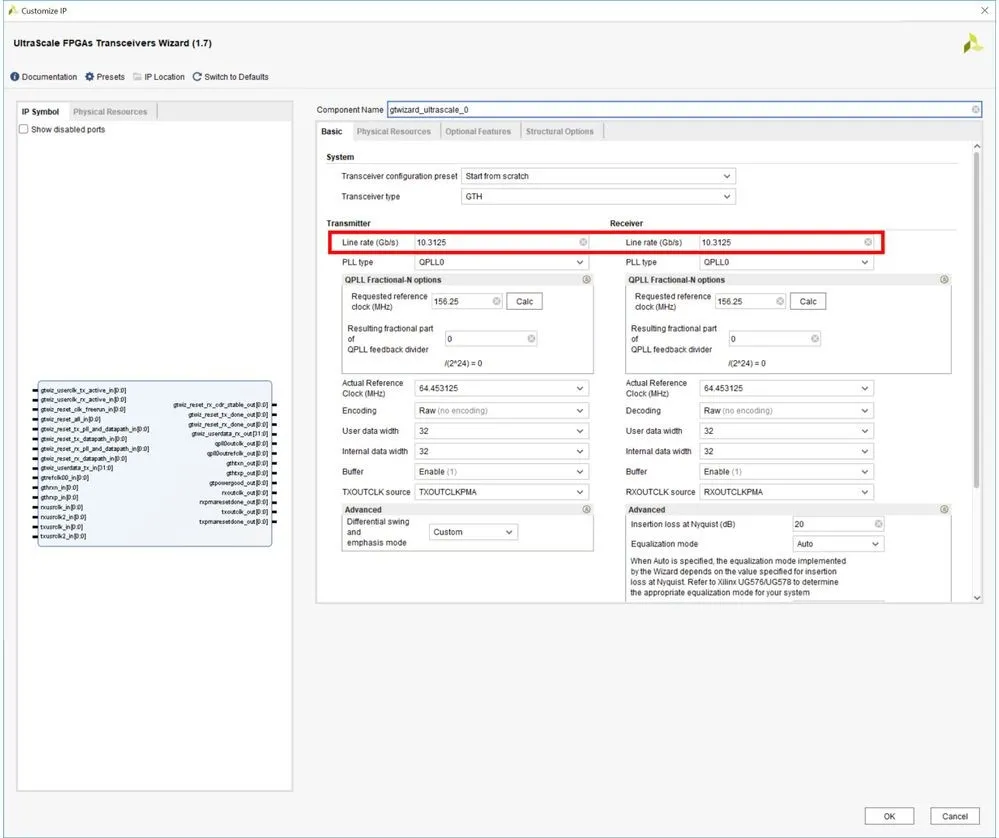

779 由于 UltraScale/UltraScale+ GTH/GTYTransceiver Wizard 不允许更改线速率设置,因此必须由收发器用户手动执行更改。

2020-09-03 10:04:29 4583

4583

本篇博文主要讲解了动态更改 UltraScale/UltraScale+ GTH/GTY 收发器线速率设置的方法。 您是否曾想过要使用 UltraScale/UltraScale+ GTH/GTY

2020-11-04 14:48:20 7158

7158

μModule Design and Manufacturing Resources

2021-02-04 09:44:08 7

7 以ZYNQ UltraScale xczu2cg784为例最重要的是参考ug1085的第27页整理如下

2022-01-12 11:42:53 1

1 UltraScale和UltraScale+进一步增强了Clock root的概念,从芯片架构和Vivado支持方面都体现了这一点。为了理解这一概念,我们先看看UltraScale/UltraScale+的时钟资源。

2022-05-12 15:34:31 1380

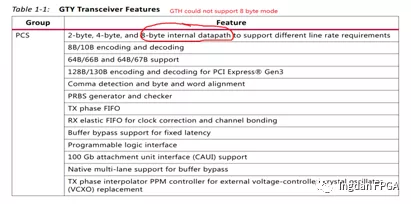

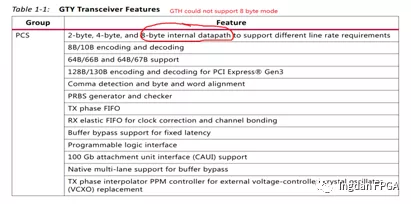

1380 的速率和带宽效率。 今天我们来聊一聊7 Series、Ultrascale系列GTH与Ultrascale+ GTY的内部区别。

2022-08-02 11:28:14 4854

4854

Zynq UltraScale+ Use Case 4.4 原理图s

2023-02-03 18:47:07 2

2 原理图 Silex Pmod Module

2023-03-14 20:04:33 1

1 Zynq UltraScale+ Use Case 1.1 原理图s

2023-03-22 19:16:27 0

0 Zynq UltraScale+ Use Case 1.4 原理图s

2023-03-22 19:17:16 0

0 Zynq UltraScale+ Use Case 3.2 原理图s

2023-03-22 19:18:54 0

0 原理图 Silex Pmod Module

2023-07-05 20:31:29 1

1 Zynq UltraScale+ Use Case 4.3 原理图s

2023-07-10 18:35:38 0

0 Zynq UltraScale+ Use Case 1.3 原理图s

2023-07-10 18:36:16 0

0 Zynq UltraScale+ Use Case 2.3 原理图s

2023-07-10 18:37:26 0

0 电子发烧友网站提供《使用加密和身份验证来保护UltraScale/UltraScale+ FPGA比特流.pdf》资料免费下载

2023-09-13 17:14:11 0

0 电子发烧友网站提供《使用UltraScale和UltraScale+FPGA开发防篡改设计.pdf》资料免费下载

2023-09-13 15:32:29 0

0 电子发烧友网站提供《UltraScale和UltraScale+ FPGA封装和管脚用户指南.pdf》资料免费下载

2023-09-13 10:29:25 1

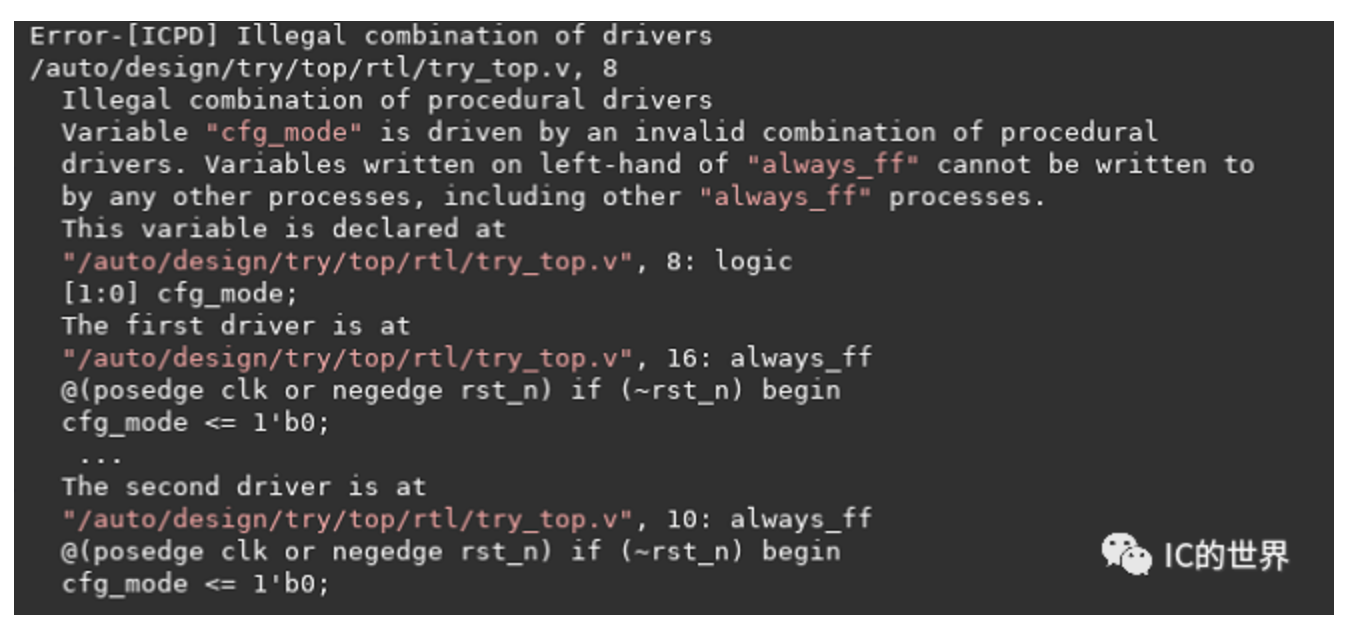

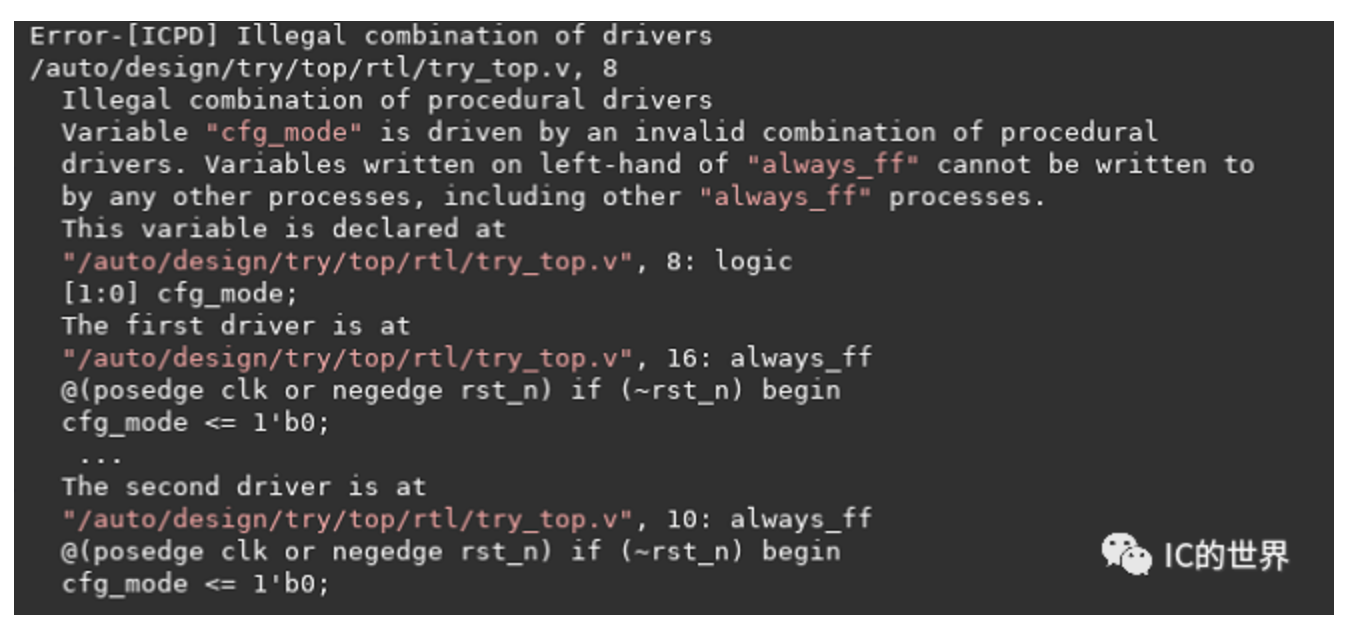

1 在systemverilog协议中,logic定义四态值,即向量(vector)的每个位(bit)可以是逻辑0, 1, Z或X,与verilog协议中的reg很接近。但是logic有个很明显的优势,不允许多驱动。

2023-09-28 17:34:37 1928

1928

什么是Logic Synthesis?Logic Synthesis用于将输入的高级语言描述(如HDL、verilog)转换为门级电路的网络表示。

2023-10-24 15:56:04 484

484

在systemverilog协议中,logic定义四态值,即向量(vector)的每个位(bit)可以是逻辑0, 1, Z或X,与verilog协议中的reg很接近。但是logic有个很明显的优势,不允许多驱动。

2023-10-26 09:32:24 325

325

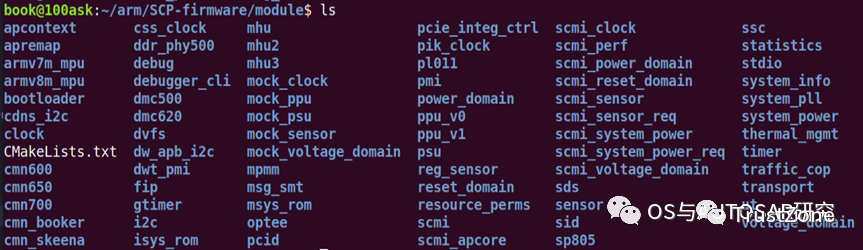

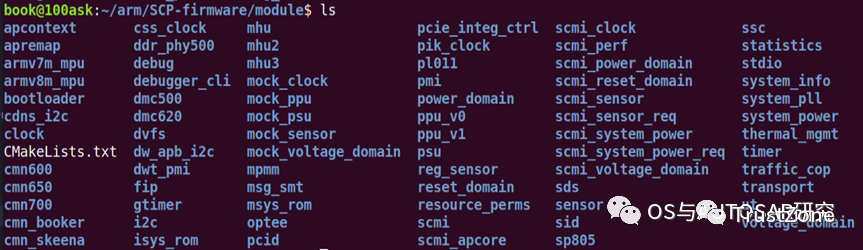

module介绍 SCP的每个功能都实现为一个单独的module,module间耦合性尽量低,确保安全特性,通常固件所需的整体功能应来自模块之间的交互。module间隔离就像上图中的狗咬架,一旦伸手

2023-11-02 17:12:41 345

345

AMD 已经拥有 Zynq UltraScale+ 和 Artix UltraScale+ 系列,而 Spartan UltraScale+ FPGA 系列的推出使其不断现代化。

2024-03-18 10:40:27 34

34

正在加载...

电子发烧友App

电子发烧友App

评论