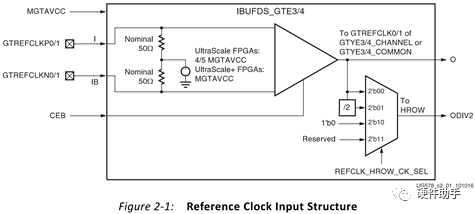

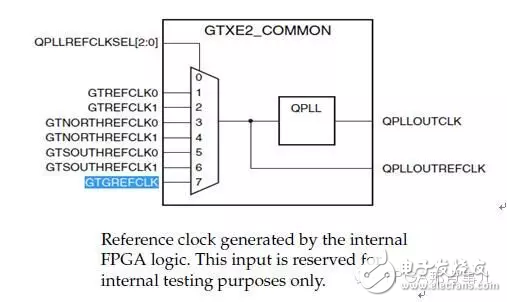

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。 参考时钟的模式 参考时钟可以配置为输入模式也可以是输出模式,但是在运行期间不能切换。作为

2020-11-14 11:39:15 13866

13866

引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。

2022-07-14 09:15:35 1538

1538 7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求。选择合适的时钟资源可以改善布线、性能和一般FPGA资源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 1276

1276 锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 655

655

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1956

1956

Xilinx7系列普及讲座内容请下载附件pdf,更多内容请登录www.rocetech.com

2013-03-31 14:20:25

Xilinx7系列普及讲座内容请下载附件pdf,更多内容请登录www.rocetech.com

2013-03-31 14:27:04

Xilinx7系列普及讲座内容请下载附件pdf,更多内容请登录www.rocetech.com

2013-03-31 14:09:45

7系列FPGA DSP48E1片的特点什么

2021-03-05 06:26:41

你好我尝试使用xilinx 7系列收发器IP生成器示例(Vivdao提供)Thegt0_qplllock_in,gt0_qplloutclk_in,gt0_qplloutrefclk_in

2018-11-05 11:34:22

嗨,我想了解7系列收发器的Kintex xc7k325tffg900-2 FPGA。https://www.xilinx.com/support/documentation/user_guides

2020-05-11 08:09:08

各路大神你们好!我想向各位咨询下:当采用BPI模式配置Xilinx V7系列FPGA时,程序是如何下载到BPI FLASH中去的?我看了V7的配置技术手册,发现里面只介绍了一种间接编程方式:由

2015-08-26 15:34:44

Xilinx 7系列FPGA简介--选型参考

2021-02-01 06:10:55

1特点 Xilinx 7 系列的提供的bank分为HP(High-performance)和HR(High-range)。HP主要为了满足高速内存的性能要求以及其他chip-to-chip接口

2020-12-23 17:17:47

200MHz、125MHz与之类似。我想问的是能不能有方法通过1个晶振给所有该频率的FPGA管脚提供时钟。第一次见发帖,求大神解答

2015-10-09 21:35:56

:Xilinx 7系列FPGA管脚是如何定义的原理图设计时如何下载FPGA管脚文件(Pinout文件)1.Xilinx7系列FPGA管脚定义表1-1、Xilinx 7系列FPGA管脚定义FPGA的器件管脚

2021-05-28 09:23:25

:Xilinx 7系列FPGA管脚是如何定义的原理图设计时如何下载FPGA管脚文件(Pinout文件)1.Xilinx7系列FPGA管脚定义表1-1、Xilinx 7系列FPGA管脚定义FPGA的器件管脚

2021-07-08 08:00:00

描述与 Xilinx MGT 表征板结合使用时,PMP6577 是一套完整的电源解决方案,适用于 Xilinx 7 系列 GTX/GTH收发器。提供高达 12A (1V AVCC)、高达 8A

2018-09-11 08:56:59

`Xilinx Kintex-7 XC7K325T-2FFG676I嵌入式核心板简介图1Xilinx Kintex-7核心板简介创龙科技SOM-TLK7是一款基于Xilinx Kintex-7系列

2020-11-23 15:51:33

前言TLK7-EVM是一款由广州创龙基于Xilinx Kintex-7系列FPGA自主研发的核心板+底板方式的开发板,可快速评估FPGA性能。核心板尺寸仅80mm*58mm,底板采用沉金无铅工艺的6

2020-09-24 14:39:36

Xilinx 20nm All Programmable UltraScale产品系列现已面世 Xilinx将业界最大容量器件翻番,达到创纪录的440万个逻辑单元 1. 赛灵思于2013年12月

2013-12-17 11:18:00

`描述PMP10600.2 参考设计提供为 Xilinx® Zynq® 7000 系列 (XC7Z015) FPGA 供电时所需的所有电源轨。此设计使用多个 LMZ3 系列模块、多个 LDO 和一个

2015-05-08 16:17:26

`描述PMP10601 参考设计提供为 Xilinx® Zynq® 7000 系列 (XC7Z015) FPGA 供电时所需的所有电源轨。此设计使用多个 LMZ3 系列模块、多个 LDO 和一个

2015-05-08 16:08:58

描述 PMP10601 参考设计提供为 Xilinx® Zynq® 7000 系列 (XC7Z015) FPGA供电时所需的所有电源轨。此设计使用多个 LMZ3 系列模块、多个 LDO 和一个

2022-09-28 06:24:34

描述此 PMP10600.1参考设计提供为 Xilinx® Zynq® 7000 系列 (XC7Z015) FPGA供电时所需的所有电源轨。此设计使用多个 LMZ3 系列模块、多个 LDO 和一个

2022-09-23 07:43:32

Xilinx_A7_K7_V7系列Cadence符号库及PCB库

2021-01-28 06:39:41

xilinx公司的7系列FPGA应用指南

2012-08-14 12:17:40

,FPGA上的全局时钟管脚用完了就出现不够用的情况。FPGA全局时钟约束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

连接器,稳定可靠,防反插和保证信号完整性;工业温度等级-40℃~85℃。图 1 核心板正面图图 2 核心板背面图SOM-TLK7是一款由创龙基于Xilinx Kintex-7系列FPGA自主研发的核心板

2020-09-18 09:57:03

大家好,关于STM32 H7系列:我打算使用 H7 系列芯片的 SDMMC 模块,通过我自己的 C 代码,不使用任何操作系统(如果可能的话)。当我思考芯片的手册参考时,我注意到

2023-02-03 07:02:09

ADAPTER TC2050 FOR XILINX CABLE

2023-03-22 19:59:52

1.开发板简介基于Xilinx Artix-7系列FPGA处理器;FPGA芯片型号为XC7A100T-2FGG484I,NOR FLASH 256Mbit,DDR3 512M/1GByte可选,兼容

2020-09-04 11:33:24

前言TLK7-EVM是一款由广州创龙基于Xilinx Kintex-7系列FPGA自主研发的核心板+底板方式的开发板,可快速评估FPGA性能。核心板尺寸仅80mm*58mm,底板采用沉金无铅工艺的6

2020-09-24 16:46:18

TLK7-EVM是一款由广州创龙基于Xilinx Kintex-7系列FPGA自主研发的核心板+底板方式的开发板,可快速评估FPGA性能。核心板尺寸仅80mm*58mm,底板采用沉金无铅工艺的6层板

2020-09-16 10:40:31

:1、Xilinx A7系列FPGA芯片与S6系列FPGA芯片的对比2、Vivado软件安装与介绍3、使用Vivado 编写Verilog代码进行开发数字逻辑开发和验证的全流程4、使用Vivado软件

2016-10-11 18:15:20

了Xilinx Artix-7FPGA的基本结构和性能,在此基础上,就可以充分发挥该器件的特性,设计实用的系统了。 到此为止,关于7A50T开发板上的硬件资源就已经基本学习完成,下一节,将开始Xilinx 的FPGA开发流程的学习。 小梅哥2016年11月1日星期二于成都市电子科技大学

2016-11-01 15:52:18

丑。大神勿喷。因有小伙伴想学习Xilinx的FPGA,现在打算拿出两块板子,和有需要的朋友交换一下。现在只打算换Xilinx的FPGA的板子,这里再简单介绍一下板子上面的资源,或者可以实现的资源:1

2015-06-19 21:38:36

Xilinx Kintex-7 XC7K325T-2FFG676I嵌入式核心板简介图 1Xilinx Kintex-7核心板简介创龙科技SOM-TLK7是一款基于Xilinx Kintex-7系列

2021-12-20 06:47:57

我有一个关于多个Xilinx芯片时钟的问题。我正在审查另一位数字工程师的设计。有多个机箱,每个机箱都有自己的Xilinx芯片(XC9500)。一些Xilinx芯片正在与其他芯片进行交互。但是,每个

2019-01-09 10:41:26

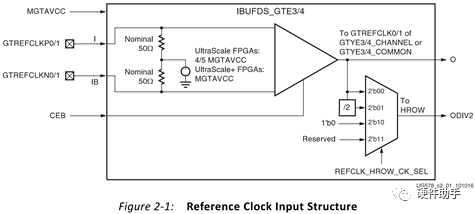

引言:本文我们介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题,指导硬件设计人员进行原理图及PCB设计。本文介绍以下内容:GTX/GTH收发器管脚概述GTX/GTH收发器时钟

2021-11-11 07:42:37

,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。赛灵思现有的FPGA中没有一款同时包含这四种资源(见表1)。 这四大类中的每一种都针对特定的应用。例如,数字时钟管理器

2020-04-25 07:00:00

全局时钟资源怎么使用?全局时钟资源的例化方法有哪几种?

2021-05-06 07:28:18

RAM)的时延和抖动都为最小。为了适应复杂设计的需要,Xilinx的FPGA中集成的专用时钟资源与数字延迟锁相环(DLL)的数目不断增加,最新的Virtex II器件最多可以提供16个全局时钟输入端口和8

2019-10-22 06:01:34

前言TLA7-EVM开发板是一款由广州创龙基于Xilinx Artix-7系列FPGA自主研发的核心板+底板方式的开发板,可快速评估FPGA性能。核心板尺寸仅70mm*50mm,底板采用沉金无铅工艺

2020-09-23 16:27:12

`基于Xilinx Kintex-7系列FPGA高端设计的TLK7-EVM评估板简介 TLK7-EVM评估板简介创龙科技TLK7-EVM是一款基于XilinxKintex-7系列FPGA设计的高端

2020-11-24 11:31:51

嗨,我是FPGA编程的新手。我在Xilinx ISE中使用VHDL进行设计。我的综合结果包括:FF,LUT,内存LUT,I / O,BRAM,DSP48,BUFG。我非常感谢能够帮助我解释每个资源

2020-03-24 10:14:15

如题:想买个xilinx7系列开发板,有没有人推荐个,最好不超过2000块,有没有

2018-01-13 21:56:36

嗨,我似乎无法在任何地方找到有关7系列硬件的目标发布日期的信息(或者如果它们已经发布)。特别是,当我可以获得Zynq或任何7系列fpgas的开发板时,我很想知道。谢谢。

2019-08-28 10:51:52

赛灵思(XILINX)全新7系列FPGA详述

2012-08-14 12:20:22

典型应用以及芯片未来展望等方面,深入阐述工程师选择Xilinx FPGA芯片的理由。 理由1 业界性价比之王 赛灵思的最新7系列FPGA芯片包括3个子系列,Artix-7、 Kintex-7

2012-09-06 16:24:35

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2010-11-03 16:24:44 121

121 本文是关于 xilinx公司的7系列FPGA应用指南。xilinx公司的7系列FPGA包括3个子系列,Artix-7、 Kintex-7和Virtex-7。本资料就是对这3各系列芯片的介绍。 下表是xilinx公司的7系列FPGA芯片容量对比表

2012-08-07 17:22:55 201

201 Xilinx FPGA系列入门教程(二)——Xilinx FPAG开发环境的配置

2016-01-18 15:30:20 32

32 Xilinx FPGA系列入门教程(一)——如何搭建Xilinx FPGA开发环境

2016-01-18 15:30:32 45

45 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 使用, 而且从性能上讲也比消耗逻辑资源的FIFO性能要好一点。XILINX 7系列中的FIFO是支持同步和异步读写操作,不需要时钟和数据之间有一个相位的便宜。空信号,满信号,和可以编程的空满信号都可以被用作控制FIFO的信号,从而可以实现不同的功能。同步FIFO可以消除异步FIFO的固有的

2017-02-08 08:18:37 278

278

时钟设施提供了一系列的低电容、低抖动的互联线,这些互联线非常适合于传输高频信号、最大量减小时钟抖动。这些连线资源可以和DCM、PLL等实现连接。 每一种Spartan-6芯片提供16个高速、低抖动的全局时钟资源用于优化性能。

2018-07-14 07:07:00 6504

6504

1. Xilinx 时钟资源 xilinx 时钟资源分为两种:全局时钟和第二全局时钟。 1. 全局时钟资源 Xilinx 全局时钟采用全铜工艺实现,并设计了专用时钟缓冲与驱动结构,可以到达芯片内部

2017-02-09 08:43:41 1315

1315 在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配

2017-11-22 07:09:36 8891

8891

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2017-11-25 01:43:01 1411

1411 Xilinx大部分的开发板上都集成了Si570时钟芯片,该时钟的性能指标比较好,可以满足大部分高速串行接口应用对于参考时钟的要求。同时该时钟还可以通过I2C接口配置其输出频率。 该专题详细介绍如何给Xilinx 7系列以及Ultrascale系列开发板上的Si570重新配置频率。

2021-08-27 14:38:54 8530

8530

这一次给大家分享的内容主要涉及Xilinx FPGA内的CLBs,SelectIO和Clocking资源,适合对FPGA设计有时序要求,却还没有足够了解的朋友。

2018-03-21 14:48:00 4672

4672

介绍赛灵思为各企业提供的专业的关于Xilinx的资源培训,以及课程内容

2018-05-22 13:47:33 3154

3154

Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。

2018-12-16 11:31:21 12305

12305

Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。 在用Vivado建立

2019-09-15 12:21:00 4826

4826

命名规则 5.7系列资源概括 1.Xilinx的四个工艺级别 Xilinx目前主要产品有四个工艺等级,通常情况下,Xilinx的产品每个工艺都会有Spartan、Artix、Kintex和Virtex

2020-11-13 18:03:30 14065

14065 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-09 14:49:00 24

24 区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA

2020-12-09 14:49:03 20

20 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-09 15:31:13 9

9 Xilinx7系列FPGA的体系结构具有灵活的内部内存资源,可以配置为各种不同的大小。本白皮书详细介绍了可用的功能,说明了各种可用内存大小,并显示了使用不同资源执行不同大小内存功能的利弊。

2020-12-09 16:15:00 8

8 FPGA时钟资源主要有三大类 时钟管理模、时钟 IO 、时钟布线资源。

2020-12-09 18:14:00 13

13 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-10 14:20:00 18

18 本章介绍了高云半导体FPGA 产品的时钟资源,包括专用的时钟输入、缓冲区和布线资源。时钟的基础设施提供了一系列低电容、低偏移互连线,非常适合承载高频信号,最大限度地减少时钟偏差和提高性能,可应用于所有的时钟信号。

2020-12-10 14:20:13 9

9 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-10 15:27:48 23

23 全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

2020-12-29 16:59:35 8

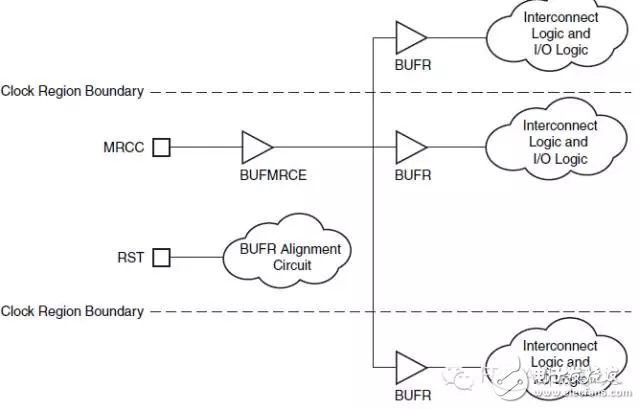

8 源同步接口设计特别有用。7系列器件中的I/O Bank与时钟区域的大小相同。为了理解区域时钟是如何工作的,理解区域时钟信号的信号路径是很重要的。7系列设备中的区域时钟资源和网络由以下路径和组件组成: 时钟输入I/O I/O时钟缓冲器:BUFIO 区域时

2021-03-22 09:47:30 4631

4631

也被设计成支持非常高频率的信号。了解全局时钟的信号路径可以扩展对各种全局时钟资源的理解。全局时钟资源和网络由以下路径和组件组成: 时钟树和网络:GCLK 时钟区域 全局时钟缓冲器 1. 时钟树和网络:GCLK 7系列FPGA时钟树设计用于低偏差和低功

2021-03-22 10:09:58 11527

11527

引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。为了最好地利用时钟路由资源,必须了解如何从PCB到FPGA获取用户时钟,确定哪些时钟路由资源

2021-03-22 10:16:18 4353

4353

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 4326

4326 解析MSP430系统时钟资源

2021-09-26 11:39:09 1

1 HROW:水平时钟线,从水平方向贯穿每个时钟区域的中心区域,将时钟区域分成上下完全一致的两部分。全局时钟线进入每个时钟区域的逻辑资源时,必须经过水平时钟线。

2022-06-13 10:07:26 1481

1481 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2592

2592 电子发烧友网站提供《Logos系列FPGA时钟资源(Clock)用户指南.pdf》资料免费下载

2022-09-26 10:15:21 1

1 电子发烧友网站提供《Compact系列CPLD时钟资源(Clock/PLL)用户指南 .pdf》资料免费下载

2022-09-26 10:03:33 2

2 业界高端FPGA的卓越性能和高口碑声誉都有哪些因素了?其中很重要的一个因素就是FPGA内部丰富的时钟资源使得FPGA在处理复杂时钟结构和时序要求的设计中具有很大优势。设计师可以更好地控制和管理时钟信号,提高时序性能、减少时钟相关问题,并满足设计的高性能和稳定性要求。

2023-08-31 10:44:01 530

530 Xilinx是一家专业的可编程逻辑器件(PLD)厂商,其产品包括FPGA、CPLD、SOC等。Xilinx的FPGA产品线有多个系列,其中7系列和Ultrascale系列是比较常见的两种。那么,这两个系列有什么区别呢?

2023-09-15 14:44:54 1776

1776

Xilinx 7系列芯片应用非常广泛,具有成本低、性能强悍、成熟稳定的特点,目前Xilinx(AMD)已延长该系列芯片的生命周期至少到2035年。

2023-11-27 09:26:10 418

418

Xilinx 7系列 芯片 应用非常广泛,具有成本低、性能强悍、成熟稳定的特点,目前Xilinx( AMD )已延长该系列芯片的生命周期至少到2035年。 本文主要介绍Xilinx 7系列 FPGA

2023-11-28 10:20:02 392

392

Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 215

215

正在加载...

电子发烧友App

电子发烧友App

评论