作者:Mculover666 1.实验目的 用HDL语言+Vivado创建一个挂载在AXI总线上的自定义IP核 2.实验步骤 2.1.创建一个新的项目 2.2.调用Create

2020-12-21 16:34:14 3088

3088

FPGA设计中,BRAM是一项非常关键的内置存储资源,FPGA开发需要熟练使用BRAM,今天再复习一下BRAM的知识,包括BRAM的定义、组成、应用等等。

2023-08-15 15:44:16 1889

1889

当我改变.elf文件时,Vivado(2014.4)重新合成和重新实现的原因是什么?对我来说,比特流再生就足够了。

2020-05-14 09:03:04

你好,在Vivado 2016.4中运行Synthesis功能时,我收到了有效的许可证错误[Common 17-345]。请参阅附件和帮助。谢谢,Gursimar合成日志file.txt 2 KB

2019-01-04 11:22:27

电路全局复位来定义初始化内容。触发器控制信号的输入应总是高电平有效。如果设置为低电平有效,会插入一个反相器,对电路性能会产生不利影响。Vivado综合工具根据HDL代码会选择4种寄存器原语:FDCE:带有

2020-09-29 10:08:57

大家好,我在Vivado中为您的FPGA合成处理器及其存储器。在写入(然后读取)内存时,我在此处理器上执行程序时遇到问题。存储器由Verilog RTL合成为BRAM,具有位写使能。程序指令序列

2018-11-08 11:35:23

我在SUSE 11.3,64位上运行vivado。我能够成功地合成设计但是当我点击打开合成设计时,vivado关闭显示引擎内存不足的详细信息:Vivado v2013.4(64位)SW Build

2019-03-13 13:47:01

大家好,我想知道Vivado生成的HDL代码是否在Vivado自带的许可证之上有任何特殊的许可。考虑为AXI奴隶生成的代码,有什么阻止我在设置中使用它大学课程的论文?如果代码刚刚生成并从设计诉讼中

2018-12-20 11:23:27

请问存储器的容量有N个字节,是不是就可以定义N个char型的变量

2012-11-30 13:23:13

存储器映射是什么意思?其映射过程是怎样的?

2022-01-21 07:39:51

-----ROM Read Only Memory,顾名思义,它是一种只能读出事先所存的数据的固态半导体存储器。ROM中所存数据稳定,一旦存储数据就再也无法将之改变或者删除,断电后所存数据也不会消失

2021-12-10 06:34:11

存储器的分类存储器是计算机系统中的记忆设备,用来存放程序和数据,从不同的角度对存储器可以做不同的分类。1、按存储介质分半导体存储器(又称易失性存储器):体积小,功耗低,存取时间短,电源消失的时候,所存的信息也随之消失。磁表面存储器(...

2021-07-26 08:30:22

规定好的,用户只能用而不能改。用户只能在挂外部RAM或FLASH的情况下可进行自定义。ARM7TDMI的存储器映射可以有0X00000000~0XFFFFFFFF的空间,即4G的映射空间,但所有器件

2014-03-24 11:57:18

大家有谁知道AT89C52怎么选择外部存储器,我之前用的是P89V51,选择外部存储器是定义AUXR=0x02;,但是现在想用AT89C52单片了,程序该怎么改了啊??AT89C52手册上找不到怎么选择外部存储器说明,各位高手有谁知道啊 ?

2023-10-26 06:11:25

库的慢-慢工艺点对块进行合成,以200 MHz的目标速度确认时序特性。

接口存储器端口上的信号符合RAM编译器为TSMC CL013G工艺技术生产的单端口同步存储器组件所要求的时序要求

2023-08-21 06:55:33

本章教程讲解DMA存储器到存储器模式。存储器到存储器模式可以实现数据在两个内存的快速拷贝。程序中,首先定义一个静态的源数据,存放在内部 FLASH,然后使用DMA传输把源数据拷贝到目标地址上(内部SRAM),最后对比源数据和目标地址的数据,判断传输是否准确。

2023-04-17 15:28:08

STM32学习笔记(7)——DMA直接存储器访问一、DMA简介二、DMA功能框图1. DMA请求2. 通道3. 仲裁器二、DMA的结构体定义和库函数定义1. DMA初始化结构体2. DMA库函数3.

2022-01-26 07:54:39

问题一:位图都存储在哪了?都在程序存储器里吗问题二:能不能将位图存储到外部内存中?问题三:F429的程序存储器和数据存储器有多大?

2020-05-20 04:37:13

FIFO存储器是系统的缓冲环节,如果没有FIFO存储器,整个系统就不可能正常工作,它主要有几方面的功能:1)对连续的数据流进行缓存,防止在进机和存储操作时丢失数据;2)数据集中起来进行进栈和存储,可

2022-01-18 10:03:06

Flash存储器分为哪几类?Flash存储器有什么特点?Flash与DRAM有什么区别?

2021-06-18 07:03:45

的、针对嵌入式应用的文件系统,实现Flash存储器的损耗均衡,并且实现数据的有效管理,对于提高其使用寿命具有一定的意义。

2019-08-16 07:06:12

。 MPAX 单元将存储器保护和地址扩展结合成一步完成。正如对局域存储器的访问一样,MPAX 的运行基础为每个交易事务承载的特权 ID,用以代表存储器的请求者。对于每个 PrivID,相关联的 MPAX

2011-08-13 15:45:42

当系统运行了一个嵌入式实时操作系统时(RTOS),操作系统通常都是使用非易失的存储器来运行软件以及采集数据。存储器的选择面很广阔,其中包括电池供电的SRAM(静态随机访问储存器),各种各样的闪存以及串口EEPROM(电可擦的,可编程的只读存储器)。

2019-06-28 08:29:29

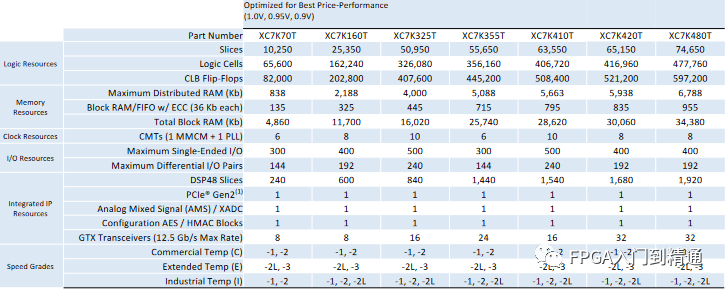

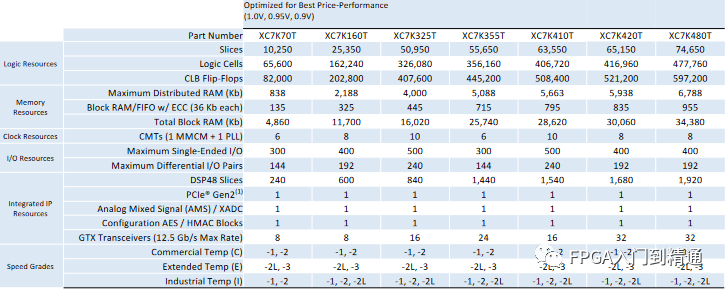

是我们所说的URAM。BRAM和URAM都是重要的片上存储资源,但两者还是有些显著的区别。 容量 BRAM的容量为36Kb,且可当作两个独立的18Kb BRAM使用。对于一个36Kb的BRAM,其最能

2020-12-23 16:57:28

为什么有的电子设备用eMMC存储器 ?而有的用DDR存储器呢?这两者有什么区别吗?

2021-06-18 06:13:25

题目是一个停车场计时系统,用74系列之类的芯片。我们用6116存储器来存地址信号,通过刷卡产生脉冲,经过延时出现两个相邻的脉冲分别代表读和写信号,用来读取存储器中对应车的状态(在不在车库内),再将

2016-07-23 00:01:59

连接情况直接关系到STM32存储器的结构组织;也就是说,Cortex-M3的存储器结构决定了STM32的存储器结构。这里可能说的比较笼统,可以这样理解:Cortex-M3是一个内核,自身定义了一个存储器

2018-08-14 09:22:26

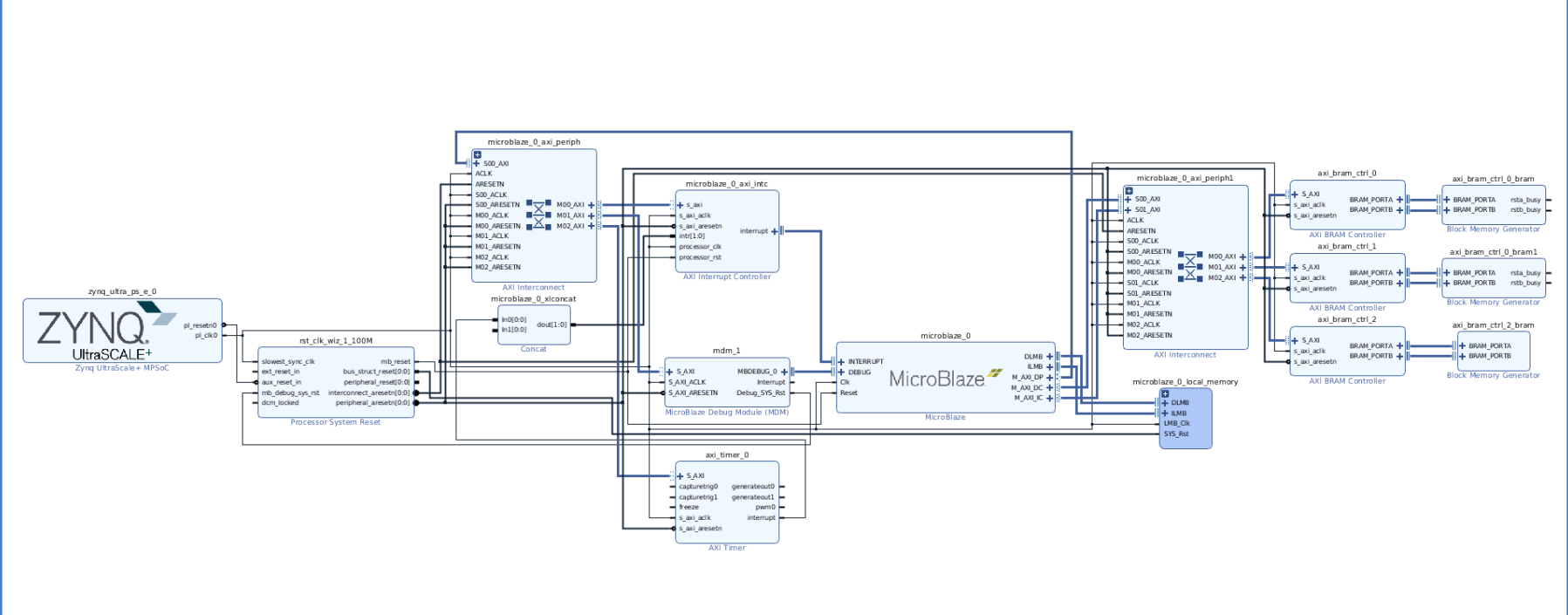

几个部分:1414.1简介14.2实验任务14.3硬件设计14.4软件设计14.5下载验证14.1简介BRAM(Block RAM)是PL部分的存储器阵列,PS和PL通过对BRAM进行读写操作,来实现

2020-09-04 11:08:46

为什么单片机定义的数组是存放在数据存储器中,而不是存放在程序存储器中,这样断电,那数组里面的数据不就丢失了吗,实在不解,请大神指教。

2016-08-14 16:41:53

什么是EEPROM存储器?

2021-11-01 07:24:44

早安Xilinx Communitry,我有一个关于VIVADO IP中心设计流程的问题。设计针对Xilinx fpga的数字逻辑不仅仅有一种方法。您可以使用HLS和HDL进行设计。您可以使用纯

2019-03-29 09:14:55

的bootloader,使用特定软件通过串口等方式下载二进制文件到单片机的内置flash,这种方法的局限性是只能下载到厂家bootloader定义的存储器上;2,使用调试器通过SWD/JTAG接口...

2021-07-16 07:29:52

vivado可以生成的.ll内容看不太懂,例如 Bit lines have the following form:; Bit 51598948 0x0042011f68 Block

2015-11-19 20:41:54

相同的-bd选项。这将替换相同的BRAM内容,而是在位文件创建过程中。所以我似乎也不能使用data2mem来编程这些闪存阵列的部分。此外,2个内存核心没有用户可见的地址空间。这些存储器用于配置和出厂设置

2020-07-26 10:04:09

大家好,我搜索了几个关于初始化BRAM的线程,但我找不到答案。我使用的是Vivado 2015.4。我写了一个coe文件,想把coe文件加载到BRAM中。首先,我添加一个BRAM IP,然后加载

2019-04-17 09:47:17

在vivado中bram加载coe文件数据仅在instatntiation中生成datain,但没有datain

2020-04-15 10:12:41

CO_SIMULATION获取所有信号。我在SYSTEM C中用verilog HDL和Firmaware编写了RTL。但我没有得到任何适用于HW / FW协同仿真的文件。请帮我解决这个问题。谢谢

2020-04-17 10:09:54

你好,我在FPGA(ISE14)中有一个部分重配置设计,它包含一个由coregen生成的BRAM存储器块。在整个设计布线后,我需要能够改变这些存储器的内容。我知道data2mem程序可以完成类似

2018-10-16 06:40:10

外部数据存储器的扩展一、实验目的二、实验内容三、实验步骤四、C代码如下五、实验结果六、实验体会一、实验目的掌握单片机系统外部存储器电路的扩展方法掌握单片机外部存储器中变量定义和读/写编程熟悉在仿真

2021-12-07 11:24:17

嗨朋友们,我正在尝试使用块内存生成器访问存储在ROM中的.coe文件。我想为此编写一个verilog代码。如何以verilog代码访问存储在BRAM中的像素值?提前致谢。以上来自于谷歌翻译以下为原文

2019-02-26 09:48:33

如何使用KEIL下载文件到单片机外置存储器?

2021-11-04 06:49:59

如何利用Xilinx FPGA和存储器接口生成器简化存储器接口?

2021-05-06 07:23:59

你好如何在不使用DDR内存控制器的情况下设计FPGA BRAM(或任何其他内存模块_SD,DDR以外的本地等)大容量存储单元?当我通过示例设计“VC707_bist”替换DRAM控制器和BRAM

2019-04-04 15:10:55

如何实现扩展存储器的设计?

2021-10-28 08:08:51

嗨 - 正如其他地方所提到的,我正在移植自己,以及从Altera到Xilinx的设计。这种设计有一些奇数尺寸的1R1W存储器(64 x 80,1024 x352)。对于初学者,我只是用

2019-10-29 08:55:19

影响存储器访问性能的因素有哪些?DSP核访问内部存储器和外部DDR存储器的时延有什么不同?

2021-04-19 08:32:10

我有一个程序文件,在模拟开始时必须存储在BRAM中。要加载BRAM,我无法重复使用我的传统测试平台任务,因为内存组织不同,因为这些任务是为ASIC RAM IP编写的。我们正在尝试使用Xilinx

2019-04-22 07:41:01

STM32的存储器由哪些组成?怎样去启动STM32存储器?

2021-09-24 07:03:23

嗨,大家好,我有一个Zynq 7020设计,在某处使用两个块公羊;使用Vivado(2016.2)块内存生成器生成(每个内存为32位宽,100k深)。合成后,利用率如下:这是我所期待的。但是,在实现

2018-10-26 15:08:30

存储器的复用 复用SPI Flash是指既用它来保存硬件配置文件、Bootloader引导程序还用来保存用户应用程序。在加载阶段,FPGA自动从SPI Flash中读取硬件配置bit文件

2020-05-02 07:00:00

嗨,我想在我的VHDL代码中使用fsm_style属性来在SpartanXC3S200AN设备中的BRAM中实现我的状态机。我在综合后得到的代码和警告如下:HDL代码arcihtecture bla

2019-04-01 12:36:46

存储器可分为哪几类?存储器有哪些特点?存储器有哪些功能?

2021-10-20 06:46:21

数据存储器 FLASH程序存储器 FLASH数据存储器 片内RAM数据存储器16M字节外部数据存储器各有什么区别?特点?小弟看到这段 很晕。ADuC812的用户数据存储器包含三部分,片内640字节的FLASH数据存储器、256字节的RAM以及片外可扩展到16M字节的数据存储器。求助高手。解释一下不同。

2011-11-29 09:50:46

求助:数据存储器6116和程序存储器2817怎么搜,在altium designer。貌似不太会用搜索功能。我总是搜不出来不知道为什么,求解答。单片机存储电路里的数据存储器6116和程序存储器

2014-07-22 23:10:03

程序存储器ROM和数据存储器RAM分开编址,属于“哈佛”结构。程序存储器ORM用于固化程序,常数和数据表。数据存储器用于存放程序运行中产生的各种数据并用于堆栈。51单片机存储器结构如图所示:51单片机存储器在物理结构上分成四个空间:片内程序存储器、片外程序存储器、片内数据存储器和片外数据存储器。从

2021-12-01 08:24:14

存储器的一般用途是代码储存。系统需要一个相对较小进的存储,大约小2Gb. 这样 .代码可以从NOR闪存直接执行,这种存储器也常用于嵌入式文件系统的存储器,这些类型的系统中 DRAM 常用便签式存储器。在这

2018-05-17 09:45:35

单片机中数据存储器片内的地址是00--7FH,程序存储器的片内地址是0000H--0FFFH,请问这两部分是不是有重叠?请具体详解!~{:1:}

2013-01-15 09:01:22

的.bit文件对其进行编程时,它不起作用。我们查看了Init_B引脚,它每2-3秒重置一次。为什么?我们已经尝试使用Vivado / SDK 2015.2和2016.4生成.bit文件,并使用Vivado

2019-04-22 13:19:03

虚拟地址物理地址等众多地址及MMU相关知识先聊聊存储器STM32单片机存储器关于编译器生成的文件数据在存储器上的存储结构物理地址、虚拟地址、线性地址和逻辑地址物理地址虚拟地址逻辑地址线性地址这些地址

2022-02-11 07:51:30

你好,我有一个与switch语句的合成有关的问题。我开始使用Vivado HLS并且我已经创建了一个小的file.cpp,仅用于学习,但是当Vivado HLS合成文件时,我没有得到任何开关语句

2019-11-05 08:21:53

嗨,我的设计在合成中使用141.5 BRAM瓦片。但是,在Zynq中可以使用140 BRAM瓦片。实施后,这个数量下降到133瓦。我的问题是vivado如何减少这一数量?实施?这点可以导致未来

2018-10-31 16:17:40

大家有谁知道AT89C52怎么选择外部存储器,我之前用的是P89V51,选择外部存储器是定义AUXR=0x02;,但是现在想用AT89C52单片了,程序该怎么改了啊??AT89C52手册上找不到怎么选择外部存储器说明,各位高手有谁知道啊 ??[/mw_shl_code]

2019-03-29 01:54:26

我使用Vivado Doc的BRAM模板开发了我的项目,如下所示//单端口Block RAM写入优先模式(推荐模板)//文件:rams_sp_wf.v模块rams_sp_wf(clk,we,en

2020-05-25 16:08:34

嗨,大家好,我想用coe文件初始化BRAM,但有两个问题。首先,当我加载coe文件时,存在文件不存在的错误。见下图:有人可以帮我解决问题吗?其次,我删除了错误文件,因为“文件组”下有两个coe文件

2019-04-18 11:27:07

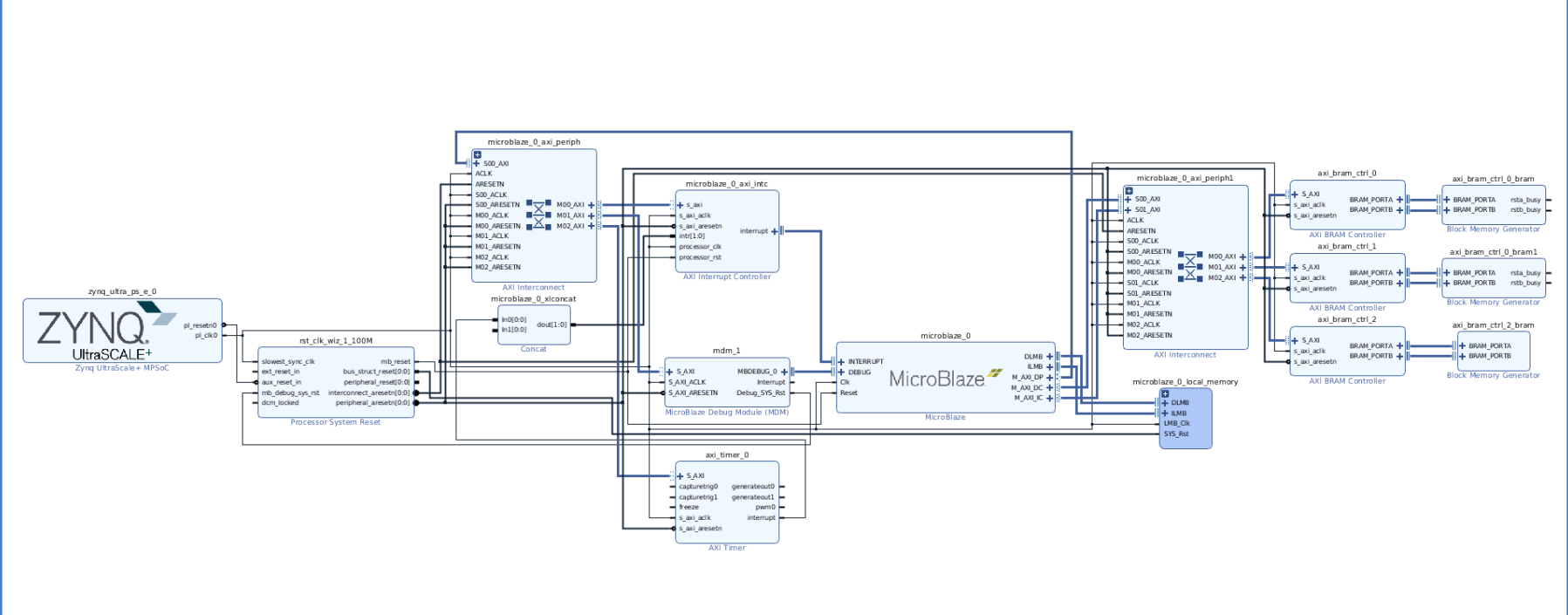

嗨, 我使用带有AXI BUS接口的Vivado 2016.1构建了我的设计。我使用了2个BRAM控制器,1个Microblaze处理器。设计成功合成。但是Vivado工具并没有走出ROUTING过程。任何人都可以帮助我们走出路由流程。下面我附上了警告信息截图。

2020-05-13 08:49:52

嗨,如何在Vivado项目中实例化hdl系统生成器输出的多个实例?在vivado项目中很容易实例化一个hdl系统生成器输出。当我想将另一个实例实例化到同一个项目时,我在合成状态下面临一些错误。最好的祝福

2020-07-31 10:38:59

嗨,大家好,我正在研究Vivado 2014.4,Xilinx KC705。我需要通过Microblaze读取存储在BRAM(coe文件)中的数据进行计算。我是微博阅读部分的新手。有人可以建议我

2020-05-20 08:38:21

存储器芯片是什么?存储器可分为哪几类?存储器术语的定义有哪些?如何去测试存储器芯片的功能?测试向量是什么?它的执行方式以及测试目的分别是什么?

2021-04-15 06:18:54

闪速存储器根据单元的连接方式,如表所示,可分成NAND、NOR、DINOR(Divided bit Line NOR)及AND几类。NAND闪速存储器单元的连接方式如图 1 所示,NOR闪速存储器

2018-04-09 09:29:07

了解如何使用Vivado存储器接口生成器(MIG)创建UltraScale存储器接口设计。

本视频将向您展示如何为UltraScale器件配置MIG IP内核,包括MIG IP I / O的I / O Bank规划。

2018-11-22 07:13:00 2633

2633 了解如何使用Vivado Device Programmer创建和配置配置存储设备。

首先,我们将学习如何设置正确的比特流属性并生成配置存储器文件。

2018-11-22 07:11:00 7095

7095 在调试Vivado 过程中,由于生成的BIT文件过大,而我使用的FLASH又是32MBIT的,出现了FLASH过小,无法烧录的情况。

2018-12-22 14:21:58 8700

8700 中国大学MOOC

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-08-06 06:12:00 3450

3450

本文档的主要内容详细介绍的是Vivado的安装生成bit文件及烧录FPGA的简要流程教程免费下载。

2019-06-18 08:00:00 25

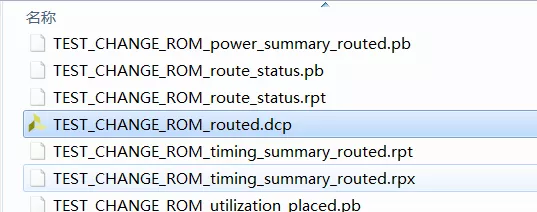

25 、实现、生成bit文件,其中,综合与实现耗时十分严重,设计规模越大,消耗的时间越长,而生成bit文件消耗的时间则相对固定。针对上述问题,本文探究一种避免综合与实现,直接修改BRAM初始化值的方法,可以避免综合、实现两个步骤,修改BRAM初始值后,

2020-11-30 15:37:43 2196

2196

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP

2020-12-29 15:59:39 9496

9496 Vivado2017.2 中BRAM版本为 Block Memory Generator Specific Features 8.3。BRAM IP核包括有5种类型:Single-port RAM 单端口RAM,Simple Dual-port RAM 简单双端口RAM(A写数据B读数据)

2021-03-10 06:15:56 19

19 Vivado中BRAM IP核是经常会用到的,而一种比较简便的给RAM赋初值的方式就是通过一个coe文件进行加载,那么如何用matlab来产生这样一个可直接使用的coe文件呢? COE文件的通用格式

2021-06-07 11:52:33 4995

4995 的bootloader,使用特定软件通过串口等方式下载二进制文件到单片机的内置flash,这种方法的局限性是只能下载到厂家bootloader定义的存储器上;2,使用调试器通过SWD/JTAG接口...

2021-11-17 11:21:06 11

11 MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM个数,决定了AXI BRAM的大小。

2022-08-02 10:09:05 2423

2423

该问题是因bit文件和ltx文件不对应导致。后来在我的调试生涯中经常遇到这个问题,当然,最简单的解决方法,就是文件没找对嘛,找对正确的ltx文件就行。

2022-08-10 11:58:44 4790

4790 在 Vivado 中进行HDL代码设计,不仅需要描述数字逻辑电路中的常用功能,还要考虑如何发挥Xilinx器件的架构优势。目前常用的HDL语言有三种。 (1)VHDL 语言的优势有: 语法规则更加

2022-12-28 17:05:01 2375

2375 本文主要介绍Vivado布线参数设置,基本设置方式和vivado综合参数设置基本一致,将详细说明如何设置布线参数以优化FPGA设计的性能,以及如何设置Vivado压缩BIT文件。

2023-05-16 16:40:45 2957

2957

Vivado 软件提供了HDL编写中常用的示例,旨在帮助初学者更好地理解和掌握HDL编程,这里分享一下verilog代码示例。

2023-05-16 16:58:06 627

627 FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

2023-08-29 16:41:49 2605

2605

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317

电子发烧友App

电子发烧友App

评论