基于FPGA vivado 17.2 的数字钟设计

2018-06-08 09:41:47 10186

10186

上篇主要是分享了Vivado编译软件远程调试的方法。杰克使用Vivado软件进行远程连接,主要是用于固化程序以及FPGA(PL端)的异常排查。而本篇主要内容是对使用Vitis软件远程调试的方法进行总结和分享。

2023-05-25 14:36:58 1685

1685

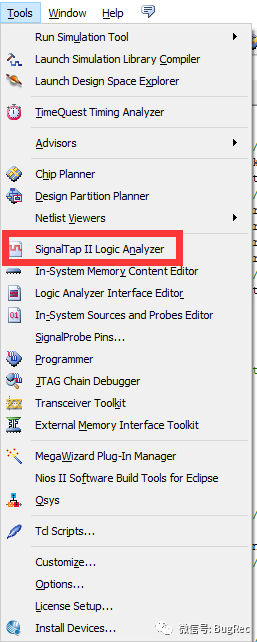

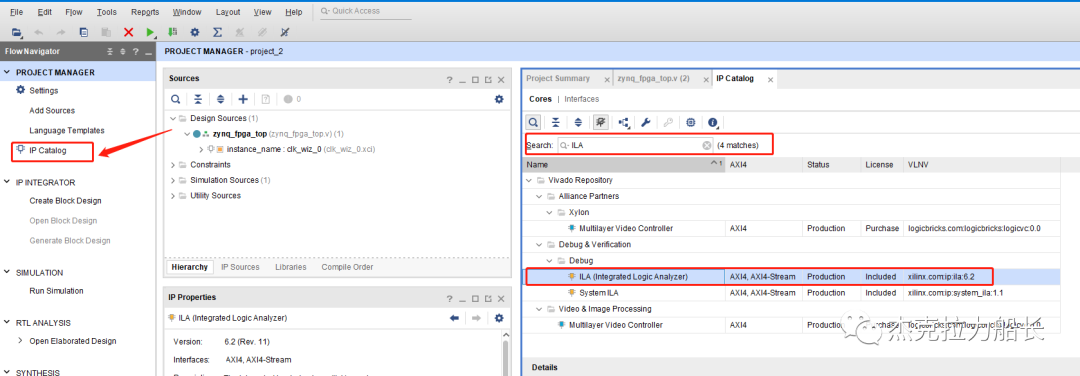

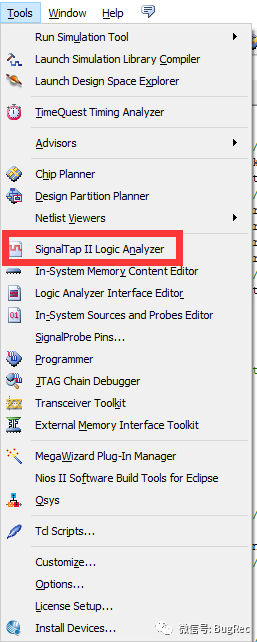

两大主流厂商的软件集成逻辑分析仪供使用,Altera的Quartus自带SignalTap、Xilinx的Vivado自带ILA逻辑调试工具。

2023-10-01 17:08:00 1456

1456

ILA Cross Triggering功能使得ILA核心之间、以及ILA核心与处理器(例如,AMD Zynq 7000 SoC)之间可以进行Cross Trigger。这个功能在你需要在不同时钟域的两个ILA核心之间触发,或者在处理器和ILA核心之间执行硬件/软件跨触发时非常有用。

2023-11-30 10:17:59 506

506

在硬件调试时,经常需要用 ILA 采集一些 FPGA 内部或者对外的初始化信号,然而在下载完 Bitstream 后立即采集这些变化稍纵即逝的信号,比如在 1uS 内手动触发 ILA 采集信号

2024-02-23 09:45:49 374

374

`基于FPGA的在线系统调试概述本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s/1pJ5bCttFPGA

2015-09-02 18:39:49

This application note covers key methods of debugging FPGAs along with technologies that reduce the number of pins needed for debug.

2019-08-08 12:24:46

当我有一个ILA核心存在时,我的设计通常会失败,我在程序框图中标记了网络上的调试。我注意到当Vivado使用调试向导修改xdc文件时,存在这种约束set_property

2018-10-29 14:12:56

在vivado中生成比特流,下板子同时用ILA抓取[5:0]}state和[2:0]count两个信号,不知道为什么count信号一直是常量,如下图,,但是代码中功能是每进入一次状态9即对count加1,而从ILA看,是可以进入状态9的,如下图,,希望大神指教。

2017-08-16 11:22:05

嗨伙计,我在Vivado面临一个问题。我已经生成了三模式以太网MAC(TEMAC)的示例设计,作为Artix7 FPGA板的给定指令。在此之后,我测试了Tx和Rx用于TEMAC。我可以成功传输数据

2020-07-23 08:23:46

嗨同事,如果你能帮助我解决这个问题,我将很高兴。[Chipscope 16-119]实现调试核心dbg_hub失败.ERROR:[Chipscope 16-111] Vivado Analyzer

2018-12-11 11:16:53

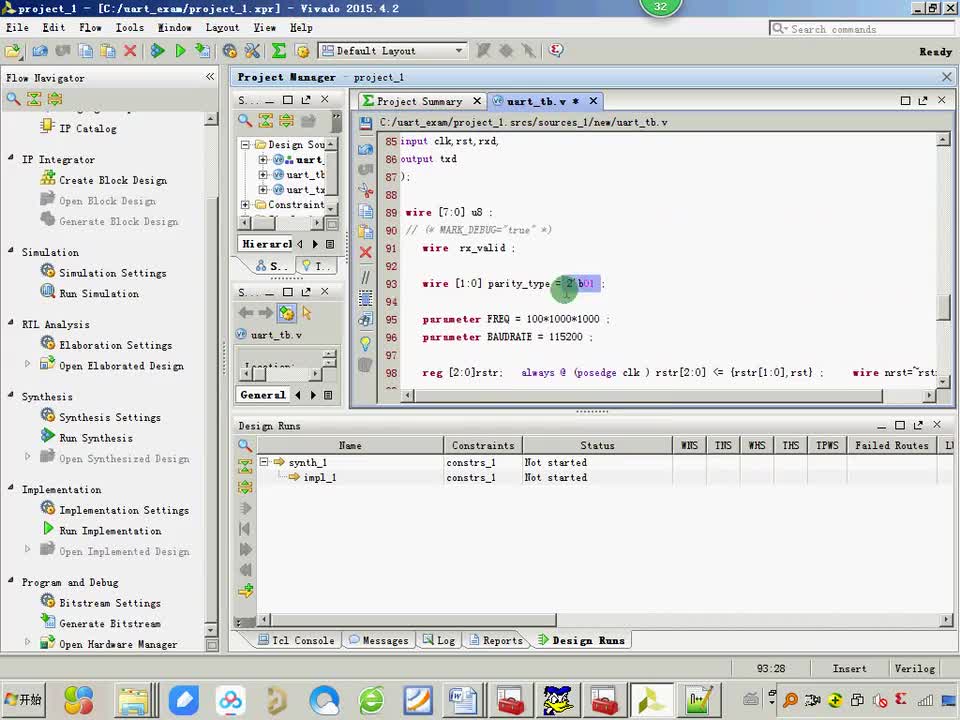

出发信号,然后设置触发值,重新运行后,能够定位到触发值。2,方法2-在代码中添加综合属性,实现在线调试。I 去掉ila_0的实例化。小技巧,可以选择多行,然后右击,选择Toggle Line

2023-04-06 21:48:03

嗨,在网络实施期间,当我将用户ILA端口从3个端口扩展到11个端口时,会生成以下消息:[Vivado_Tcl 4-131] Power Optimization遇到异常:ERROR:[Common

2018-11-08 11:29:12

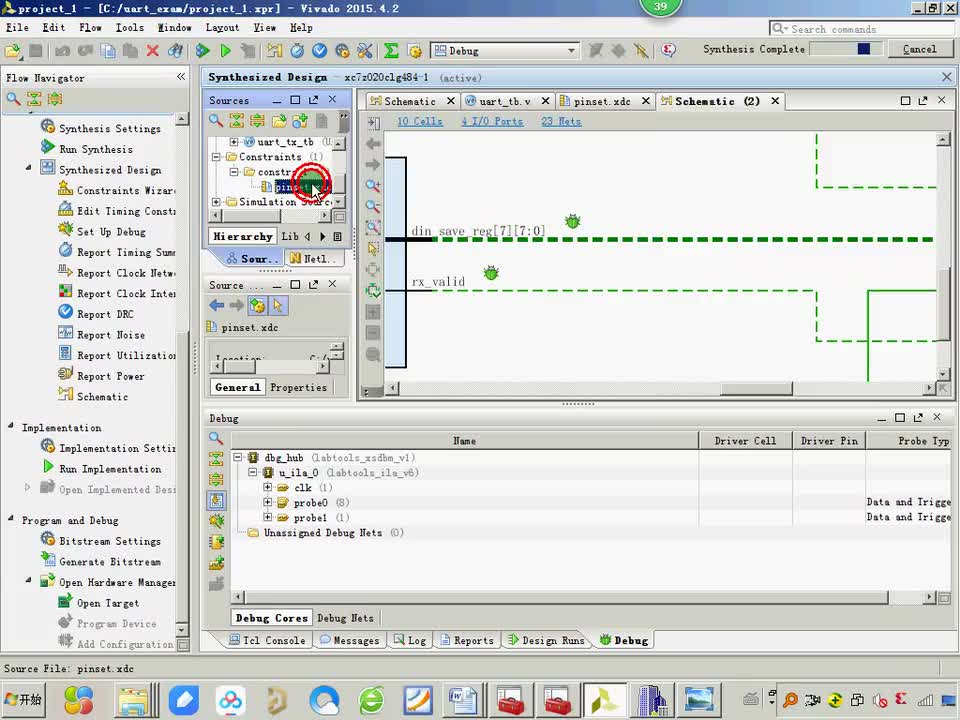

,确认无误后直接点击finish即可,如下图所示:在“Debug”子窗口中的“Debug Cores”选项卡中,可以看到Vivado已经添加了ILA IP核,并且“Unassigned Debug

2023-04-17 16:33:55

在用Vivado实现某个工程时,功能仿真正确,时序满足要求,比特流也能生成,但是在ILA调试和下板子时,无法得到正确的结果信号,请问各位大神可能是什么问题?

2017-12-11 11:10:47

在使用vivadao在线调试功能时,对需要抓的信号MARK DEBUG,调用了ILA测试核,添加了时钟约束,但是总是显示no nets matched的warning,最后烧到片子里界面没有跳转到在线调试界面,无信号,显示没有添加ILA,问题出在哪里呢?求大神解答

2015-06-08 11:19:27

DSP的CCS软件在线调试,不仅能观察数据,还能在线修改参数值,我想问一下vivado在线调试有这个功能吗,我看见debug好像只能在线观察,我想把bit文件下载到板上,我不仅要观察,还想在线改变一些参数值(不需重新编译),vivado有这个功能吗??急求,谢谢大家了!!!

2017-12-20 14:03:27

大家好,我在使用Arty(Artix 7 FPGA)进行调试时遇到了一些麻烦。背景:我使用ILA在Zybo(Zynq)和Nexys 4 DDR(也是Artix 7)上调试我的程序,一切正常。我

2020-08-26 15:20:18

of an implementation issue with Vivado. I am attempting to add debug cores to my design with ILA cores and probes.

2019-01-03 11:00:14

dbg_hub_CV.0文件夹甚至不存在,这可以解释为什么我收到错误。有谁知道我为什么看到这个以及我能做些什么来绕过它?日志错误:错误:[Chipscope 16-212]处理Vivado调试IP时出现故障“c:/F

2018-11-13 14:18:54

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

MDK在线调试TQ2440,Debug后就直接全速运行了,我已经设置了run to main(),求解

2015-03-23 16:44:02

简介STM32支持连接调试器进行在线Debug调试,可以用于一步步的排查程序的错误STM32F1系列的Cortex-M3 支持两种调试主机接口(debug host interface ) :第一个

2022-01-26 07:09:06

所有: 我在VC707主板上使用Vivado 2015.4中的ILA内核时遇到问题。有时它被硬件管理员识别,有时不被识别。当硬件管理器识别出来时,我有时会收到数据已损坏的错误消息。 是否可以告诉

2018-10-31 16:15:41

的JTAG Chain和Debug Core,因此本文提出一种比较方便的调试方法来同时使用这两个core:ILA通过analyzer查看,VIO通过TCL控制。使用步骤:使用CoreGEN生成VIO

2012-03-08 15:29:11

linux上的在线debug如何开展?

2021-12-24 06:10:37

就跑非的,前面几步还是可以正常走,走着走着就会跑飞了。3.工程A和工程B的代码基本功能一样。4.我的怀疑有两点,一个是工程配置的问题,还有一点就是代码不一致,引出的在线debug跑飞的情况。问题解决:1.我新建一个工程C,使用可以在线debug的A工程的代码 ,结果是可以在线单步调试;2

2022-02-22 06:20:14

你好这是我第一次尝试添加ILA来调试loigc。在Vivado我添加了ILA IP核 ila_0 ila_0_INST( .clk(sys_clk),//输入线clk.probe0

2019-10-10 05:57:42

。结果是我可以使用prj A在板上进行调试,但是在使用prj B进行调试时失败了。错误消息在图中。图示意图显示我将clk连接到ILA。图debug_error显示了HW调试中的错误消息。以上来自于谷歌

2019-03-27 09:56:05

最近我一直在使用vc709板来研究PCIe示例,然后我想用ILA IP调试核心.AndI就像视频所说的那样,在我创建比特流并打开之后调用插入调试核心到Design.But很难,Vivado给我一个

2020-07-27 14:28:58

2或4处的调试集线器。要确定用户扫描链设置,请打开已实现的设计并使用:get_property C_USER_SCAN_CHAIN [get_debug_cores dbg_hub]。警告

2019-10-16 09:34:16

嗨,大家好,我目前正在创建一个PCIe接口卡,我正处于项目的调试阶段。我试图监视用户_clkrate的AXI突发。关于ILA核心和PCIe端点(在VC709上)我有一些问题。1.当我尝试将

2019-09-25 09:26:14

hw_server以检测用户扫描链2或4处的调试集线器。要确定用户扫描链设置,请打开已实现的设计并使用:get_property C_USER_SCAN_CHAIN [get_debug_cores

2020-08-17 10:04:52

仿真和生成mcs文件后运行的结果如下(仿真的结果和实际传回的数据结果不同,并且相同的c程序前后两次传回的结果都不同),目前想用ila调试,看错在那一步了,但ila一直不出波形,三种加debug的方法

2023-08-16 06:37:13

你好,我在合成后插入了调试核心。并生成了位文件。在对FPGA进行编程之后,我能够看到ILA内核和信号。但是无法触发,也无法看到波形。我在Ubuntu 14上使用Vivado 2014.4。有人遇到过这个问题?如果我得到一个带有调试核心的小示例项目,那将会很棒。谢谢哈

2020-07-30 09:49:48

[Chipscope 16-119]实现调试核心u_ila_0 failed.ERROR:无法为u_ila_0生成核心。中止IP生成操作。错误:[Chipscope 16-218]尝试从IP缓存

2018-10-26 15:10:15

Configured(TM.java:372)at com.xilinx.sdk.debug.core.XilinxAppLaunchConfigurationDelegate.isFpga

2018-12-25 11:11:02

大家好如果我想在ILA调试模式下看到显示信号的幅度怎么办?你觉得有可能在屏幕上看到吗?例如,我在附加的图片上标记了红色箭头和蓝色箭头。你认为我可以调整信号的幅度吗? (如示波器)或调整ILA显示

2019-04-11 08:37:24

你好,由于我的ILA上没有连接的调试通道,我的构建是failingopt_design。这是错误消息:错误:[Chipscope 16-213]调试端口'u_ila_0 / probe20'有1个未

2018-10-25 15:22:27

因此,在最终解决了由许可证问题引起的最后2-3个问题之后,我又一次遇到了许可证问题。这次是使用ILA块。没有它,我理解我无法进行任何调试。我刚刚收到“未找到Vivado分析器许可证”的错误在我可以

2018-11-29 16:15:10

PlanAhed教程:使用Chipscope -UG677进行调试(v 14.5)以调试此问题。我们发现PlanAhead工具推断出ILA核心的多个实例,因为我们增加了标记为调试的“网络”数量。有时,32位总线

2019-03-08 13:57:18

/1XTQtP5LZAedkCwQtllAEyw提取码:ld9c 1概述基于Vivado的板级调试介绍,可以参考文档《玩转Zynq-基础篇:基于Vivado的在线板级调试概述.pdf》。这里我们以zstar_ex54工程为例,对FPGA的在线逻辑

2019-10-28 11:14:02

1概述基于Vivado的板级调试介绍,可以参考文档《玩转Zynq-基础篇:基于Vivado的在线板级调试概述.pdf》。这里我们以zstar_ex55工程为例,对FPGA的Virtual IO

2019-11-18 15:08:59

更加独特的调试手段。在FPGA器件支持并且剩余逻辑资源足够的情况下,设计者往往习惯于使用开发软件提供的在线逻辑分析仪进行调试,如Vivado的ILA和QuartusII的SignalTapII,它们

2019-05-24 15:16:32

斑梨电子树莓派Pico RP2040官方原装USB串口调试套件Raspberry Pi Debug ProbeRaspberry Pi Debug Probe是一个一体化的USB调试套件,提供所有

2023-02-25 10:48:18

什么是D-ILA投影技术

D-ILA(Direct-Drive Image Light Amplifier,直接驱动图像光源放大器)技术。D-ILA技术在提供高分辨率和高对比度方面显示了技术优势,

2010-02-05 10:42:23 636

636 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

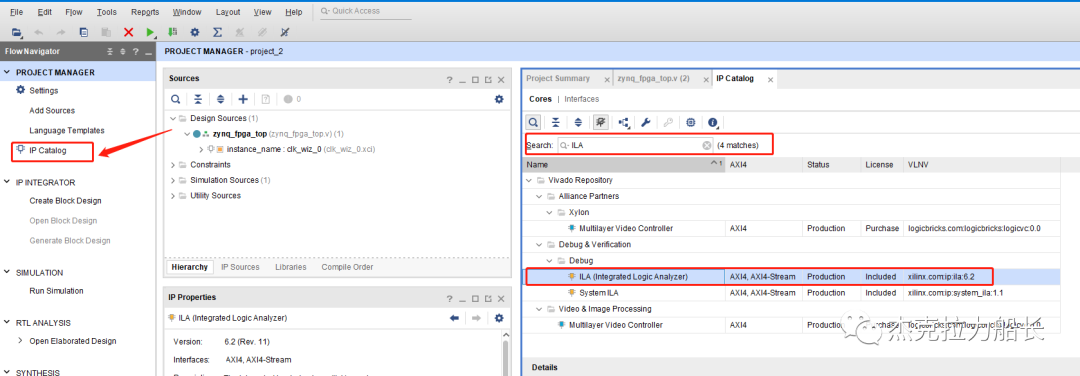

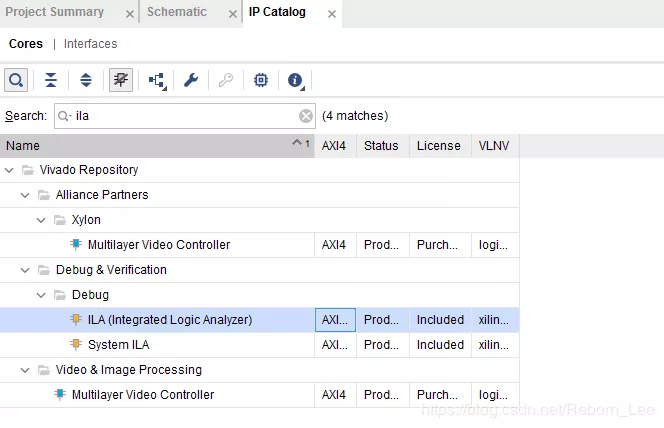

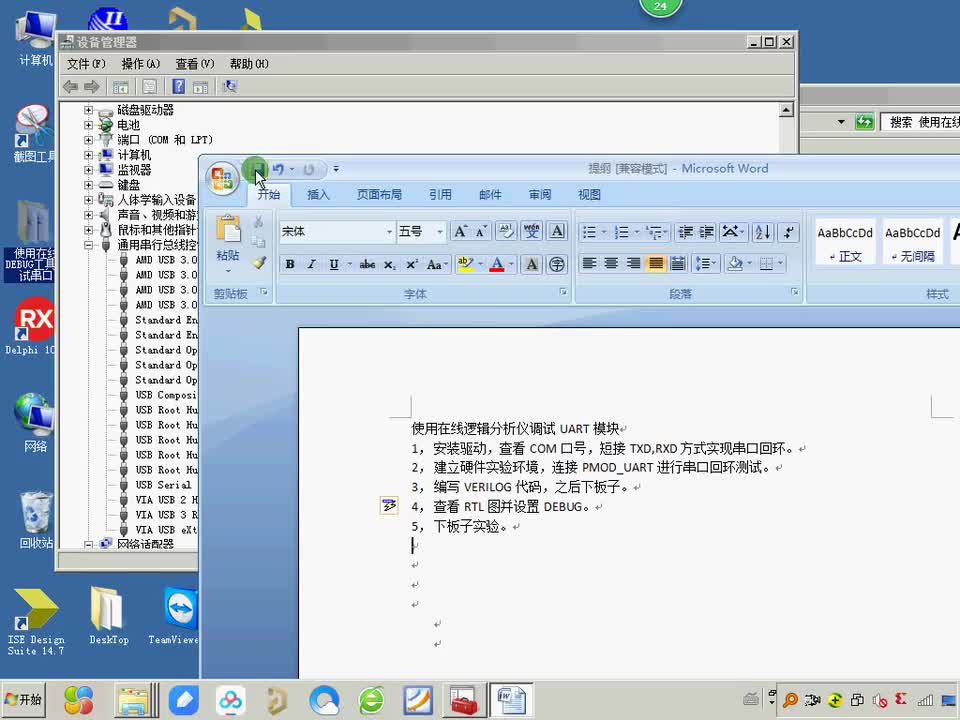

65 在ISE中称为ChipScope而Vivado中就称为in system debug。下面就介绍Vivado中如何使用debug工具。 Debug分为3个阶段: 1. 探测信号:在设计中标志想要查看的信号 2. 布局布线:给包含了debug IP的设计布局布线 3. 分析:上板看信号。

2017-11-17 14:05:02 56687

56687

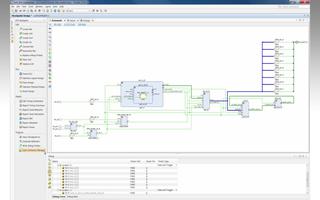

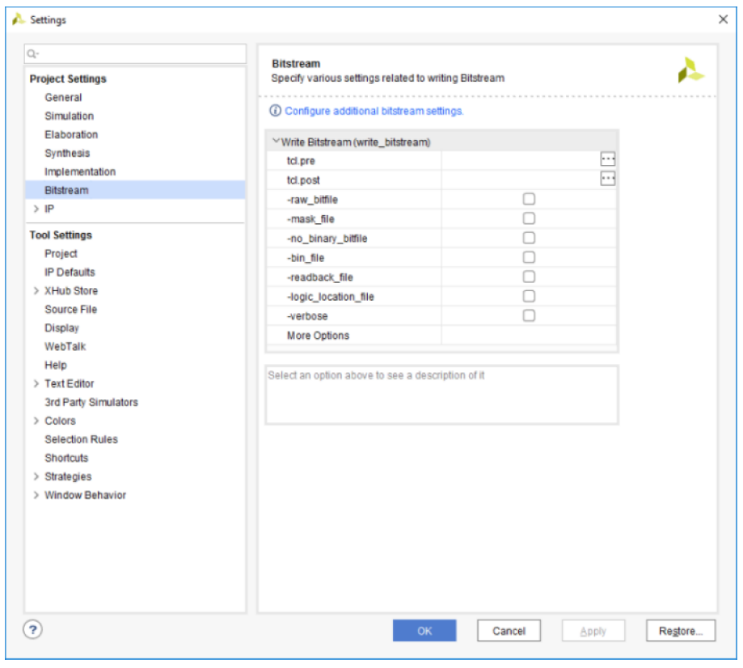

PL部分调试,作为PL DMA的控制APB总线,将其设置为Mark Debug,如下图所示。综合完成,不进行implemention,在综合菜单下面找到“Set Up Debug”,进行ILA配置。

2017-11-28 15:46:26 6787

6787 本文档内容介绍了基于chipscope使用教程以及FPGA在线调试的方法,供参考

2018-03-02 14:09:49 9

9 FPGA设计中的信号连接到ILA核的时钟和探针输入如图1。这些信号附加到探针输入,以设计速度采样,并使用片上块RAM(BRAM)存储。核参数指定探针的数量、跟踪样本深度和每个探针输入的宽度。使用与FPGA的JTAG接口连接的自动实例化调试核心集线器与ILA核进行通信。

2018-08-04 10:29:00 1931

1931

Vivado不仅是xlinx公司的FPGA设计工具,用它还可以学习Verilog描述,你造吗?

2018-09-20 09:29:22 9427

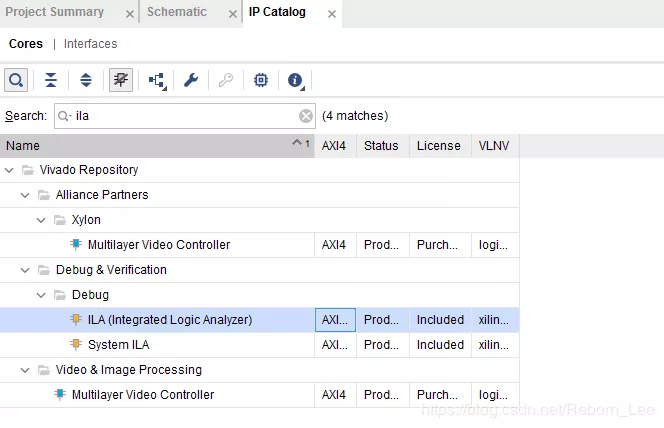

9427 其实这儿便很简单了,可以直接在画布上添加一个ILA核,再把想要的信号线连进来就行了呀,都不需要在代码里定义这个ILA核。不过这样做就说明你还没能灵活的使用Xilinx的在线调试工具了,因为还有更简单的办法哈哈。

2018-11-14 10:47:56 6509

6509

了解使用Vivado 2016.3中引入的系统内IBERT进行调试的好处,以及将其添加到设计中所需的步骤。

2018-11-20 06:43:00 5435

5435 了解使用Vivado 2016.1中引入的增量编译流程进行调试的好处,以及在使用增量编译实现时添加/删除/修改ILA内核所需的步骤。

2018-11-30 06:19:00 2759

2759

了解Vivado中的Logic Debug功能,如何将逻辑调试IP添加到设计中,以及如何使用Vivado Logic Analyzer与逻辑调试IP进行交互。

2018-11-30 06:22:00 3107

3107 了解使用Vivado 2016.1中引入的ECO流程进行调试的好处,以及在ECO布局中替换ILA调试探针所需的步骤。

2018-11-29 06:01:00 3316

3316

了解如何使用Vivado在设备启动时及其周围进行调试。

你也会学习

使用Vivado 2014.1中引入的Trigger at Startup功能来配置和预先安装a

调试核心并触发设备启动时或周围的事件......

2018-11-22 07:05:00 4084

4084 Vivado在使用A7芯片时,使用内部逻辑分析仪时,在非AXI总线下最多只能绑定64组信号(例化一个或者多个ILA模块,信号组数相加不能超过64),如果超过64组会出现错误。

2018-11-23 09:38:55 1400

1400 STM32F1系列的DEBUG调试功能需要配置吗?

2020-03-01 13:57:43 2980

2980 说说STM32调试DEBUG相关知识

2020-03-06 15:23:22 3565

3565 FPGA的调试是个很蛋疼的事,即便Vivado已经比ISE好用了很多,但调试起来依旧蛋疼。即便是同一个程序,FPGA每次重新综合、实现后结果都多多少少会有所不同。而且加入到ila中的数据会占用RAM资源,影响布局布线的结果。

2020-03-08 17:35:00 9947

9947 Tcl介绍 Vivado是Xilinx最新的FPGA设计工具,支持7系列以后的FPGA及Zynq 7000的开发。与之前的ISE设计套件相比,Vivado可以说是全新设计的。无论从界面、设置、算法

2020-11-17 17:32:26 2112

2112 Vivado中提供了多种Debug的操作方式,下面就来总结一下: 1. 代码中例化ILA IP核 第一种,直接例化ILA IP核: 需要探测多少个信号,信号的位宽是多少,直接选择即可: 下面界面可以

2020-11-11 17:07:13 10177

10177

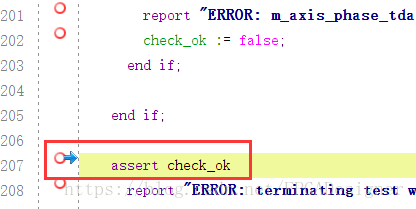

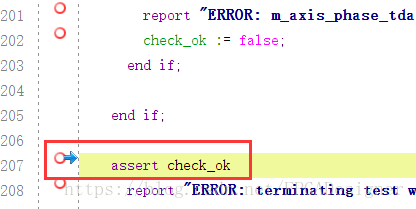

源代码级别调试 Vivado Simulator提供了在仿真过程中debug设计的特性,通过为源代码添加一些可控制的执行条件来检查出问题的地方。总的来说有三种调试方法: 1.使用Step逐行调试

2020-12-29 15:57:04 14316

14316

在线调试也称作板级调试,它是将工程下载到FPGA芯片上后分析代码运行的情况。

2020-11-01 10:00:49 3948

3948

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

2022-02-08 11:35:19 22057

22057

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

2021-01-22 07:52:04 19

19 不一致,从而出现Bug。一种debug的方式就是用FPGA工具提供的ILA模块(xilixn在ISE中叫:chipscope),来实时抓取FPGA内部数字信号的波形,分析逻辑错误的原因,帮助debug。 ILA

2021-08-09 14:12:05 15208

15208

配置VScode编译、调试STM32(二)Cortex-Debug插件

2021-12-01 12:21:04 16

16 【流水灯样例】基于 FPGA Vivado 的数字钟设计前言模拟前言Vivado 设计流程指导手册——2013.4密码:5txi模拟

2021-12-04 13:21:08 26

26 就跑非的,前面几步还是可以正常走,走着走着就会跑飞了。3.工程A和工程B的代码基本功能一样。4.我的怀疑有两点,一个是工程配置的问题,还有一点就是代码不一致,引出的在线debug跑飞的情况。问题解决:1.我新建一个工程C,使用可以在线debug的A工程的代码 ,结果是可以在线单步调试;2

2021-12-27 19:31:35 6

6 STM32等单片机,使用J-Link或ST-Link等调试器,可以进行在线调试,由于C代码是顺序执行的,我们可以插入断点,让程序停在我们需要的位置,或者是实时查看一些变量的数值,大大提高了我们Debug的速度,提高产品的开发效率。

2022-06-15 09:34:00 1679

1679 主题 1:VIVADO 开发流程和资源评估 学习目标: 1、掌握 VIVADO 开发流程 2、掌握 VIVADO 的在线调试流程 3、掌握资源评估的方法 学习内容: 1、开发流程:新建

2022-06-21 06:50:44 267

267 今天介绍的是vivado的三种常用IP核:时钟倍频(Clocking Wizard),实时仿真(ILA),ROM调用(Block Memory)。

2023-02-02 10:14:01 2529

2529 Xilinx LabTools工具是Xilinx FPGA单独的编程和调试工具,是从ISE或Vivado中独立出来的实验室工具,只能用来下载FPGA程序和进行ILA调试,支持所有的FPGA系列,无需

2023-03-28 10:46:56 4755

4755 Xilinx被AMD收购的事情把我震出来了,看了看上上一篇文章讲了下仿真的文件操作,这篇隔了很久远,不知道该从何讲起,就说说FPGA的在线调试的一些简单的操作方法总结。

2023-06-19 15:52:21 1225

1225

之前的文章介绍了FPGA在线调试的方法,包括选定抓取信号,防止信号被优化的方法等等。

2023-06-20 10:38:48 3333

3333

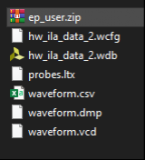

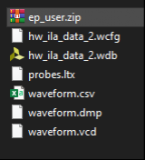

现在,您不仅可以使用 Python 脚本执行调试分析,更重要的是,借由 Vivado ILA 所生成的 ILA 文件可以进一步简化此操作。通过将 *.ila 扩展名重命名为 *.zip 然后将生成的文件解压,即可将其转换为 CSV 文件。

2023-06-26 09:20:46 634

634

电子发烧友网站提供《Vivado Design Suite用户指南:编程和调试.pdf》资料免费下载

2023-09-13 14:47:21 0

0 电子发烧友网站提供《Vivado设计套件用户指南:编程和调试.pdf》资料免费下载

2023-09-13 11:37:38 0

0 《Vivado Design Suite 用户指南:编程和调试》 文档涵盖了以下设计进程: 硬件、IP 和平台开发 : 为硬件平台创建 PL IP 块、创建 PL 内核、功能仿真以及评估 AMD

2023-10-25 16:15:02 354

354

电子发烧友App

电子发烧友App

评论