感谢你对Vivado HLS也就是XILINX’s 高层次综合解决方案有兴趣,这个解决方案综合c,c++和系统c代码成Verilog和VHDL RTL结构。

2012-04-25 08:59:37 2583

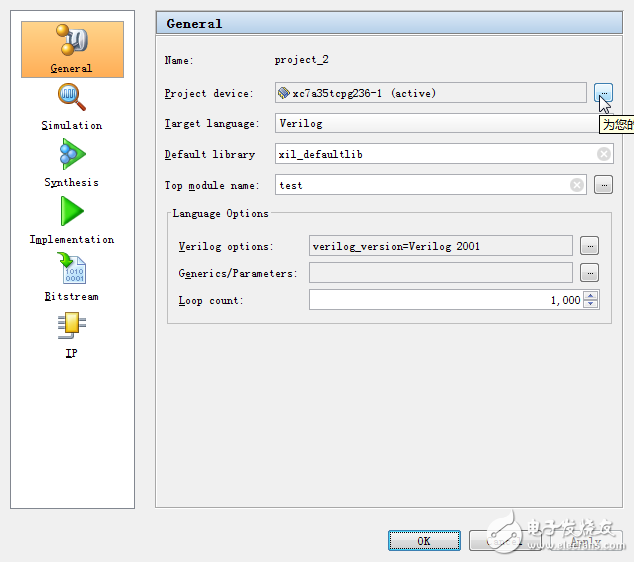

2583 先给大家简单快速地介绍一下 Vivado 集成设计环境,即 IDE。当打开 Vivado 工程后,会有一个工程概要,向您介绍工程的设置、警告和错误信息以及工程的一般状态。

2012-04-25 09:00:43 6408

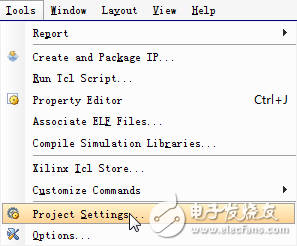

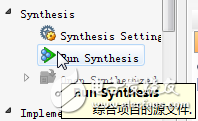

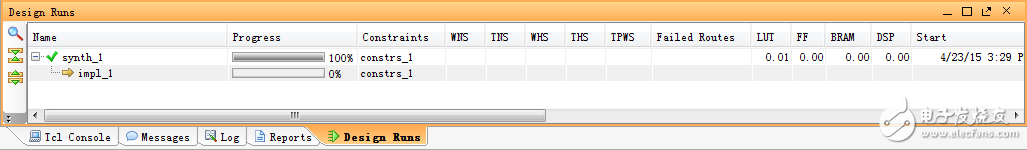

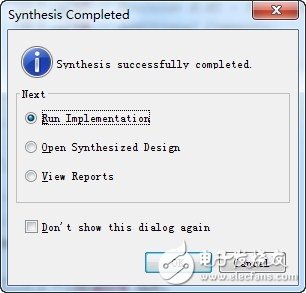

6408 在 Flow Navigator 中点击设置, 然后选择Synthesis,或者 selectFlow Settings Synthesis Settings。 如图1所示: 1、综合约束 在设置

2020-11-23 14:16:36 4238

4238

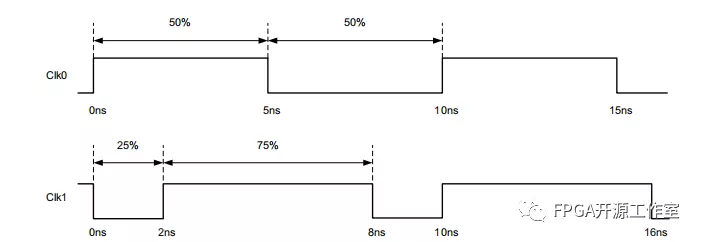

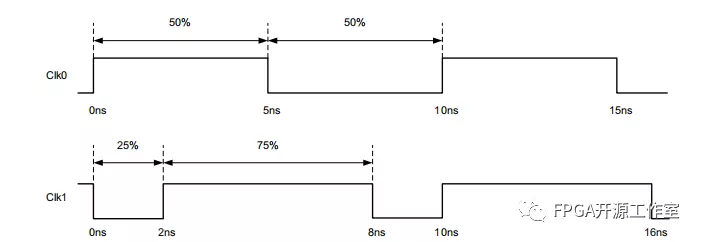

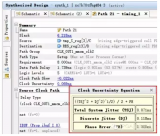

1. 时钟介绍 在数字设计中,时钟代表从寄存器(register)到寄存器可靠传输数据的时间基准。Xilinx Vivado集成设计环境(IDE)时序引擎使用ClocK特征计算时序路径要求,并通过

2020-11-29 10:51:45 5359

5359

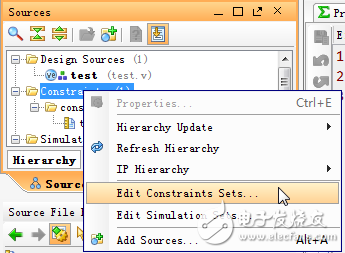

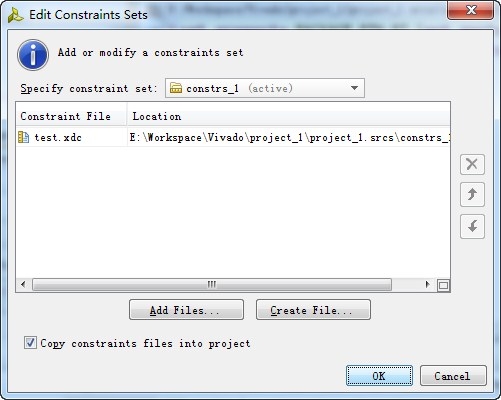

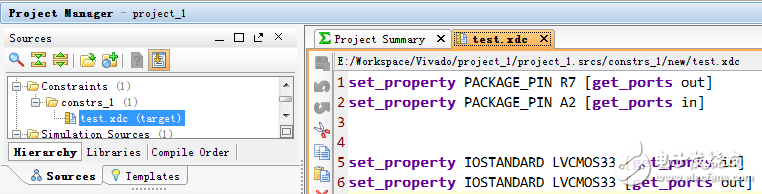

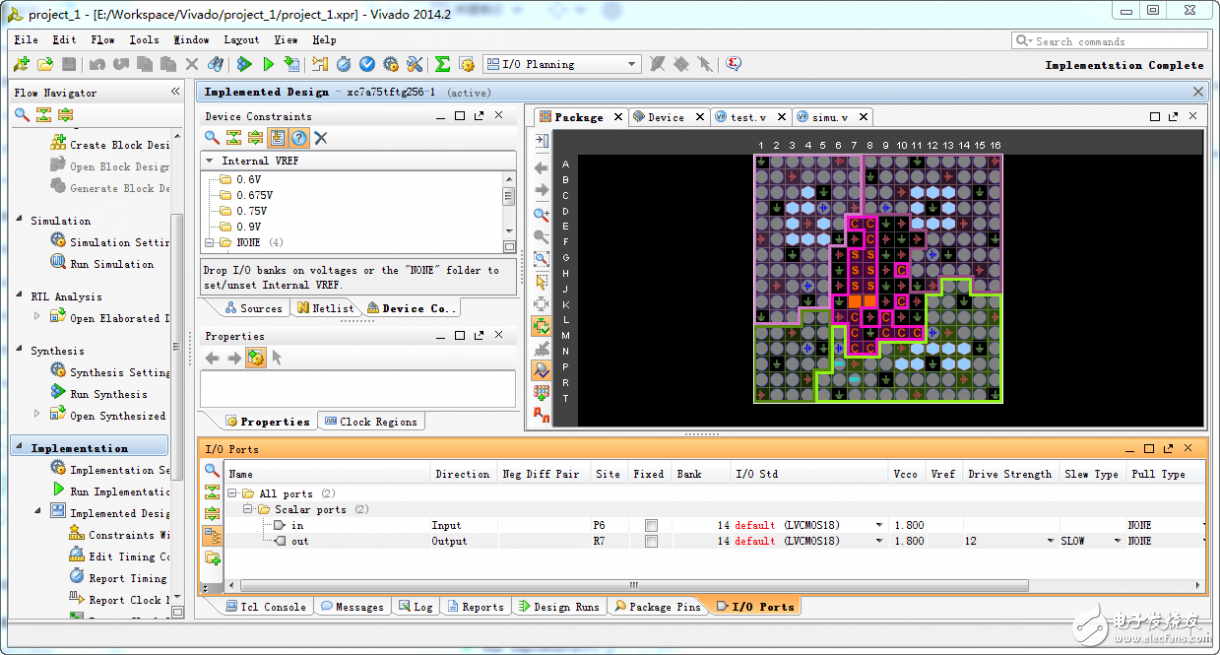

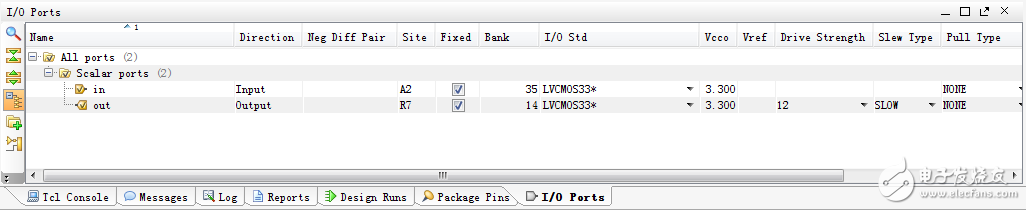

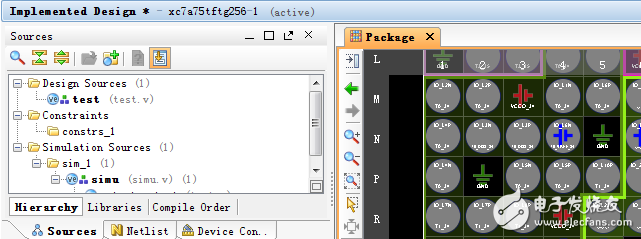

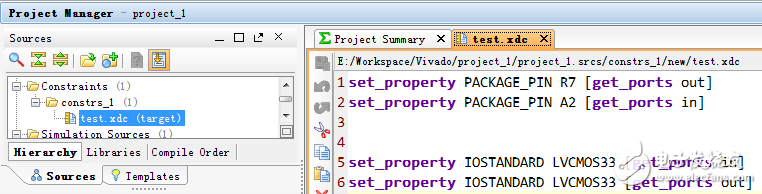

引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2022-07-25 10:13:44 4067

4067 “全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错

2023-07-24 11:07:04 655

655

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1956

1956

Vivado概述 / 251.3.1 Vivado下的FPGA设计流程 / 251.3.2 Vivado的两种工作模式 / 261.3.3 Vivado的5个特征 / 30参考文献 / 31第2章

2020-10-21 18:24:48

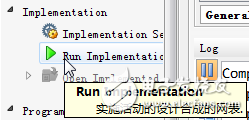

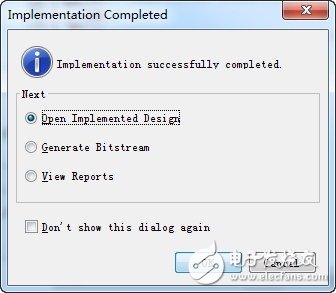

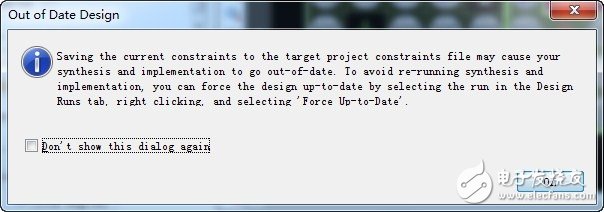

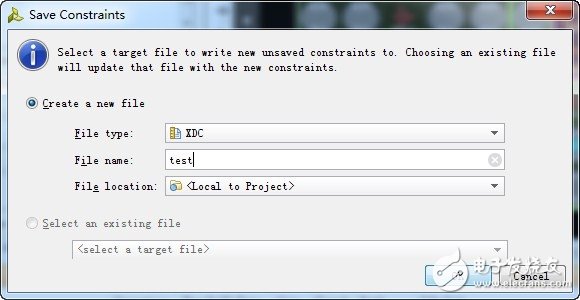

和Vivado的综合性能,管脚位置与电平约束完全一致。PS:若时钟和管脚约束直接敲命令,两者除了语法,没有明显区别。6、综合实现——点评:Vivado默认策略情况下从综合到生成bit共计23分50秒。而

2021-01-08 17:07:20

1.1 Vivado出现内部异常导致内部异常的原因有很多,但是可行的解决方法有非常直接的,经测试后可行的就是关闭Vivado窗口,再次重新打开。2.Vivado综合,仿真,实现过程中 出现的问题在

2021-07-31 09:09:20

电路全局复位来定义初始化内容。触发器控制信号的输入应总是高电平有效。如果设置为低电平有效,会插入一个反相器,对电路性能会产生不利影响。Vivado综合工具根据HDL代码会选择4种寄存器原语:FDCE:带有时钟

2020-09-29 10:08:57

Xilinx官网:www.xilinx.com; 2)选中Support菜单下的Downloads&Licensing;3)选择对应系统;2.2Vivado安装(2015.4为例)1)运行

2019-07-18 15:40:33

Xilinx官网:www.xilinx.com; 2)选中Support菜单下的Downloads&Licensing;3)选择对应系统;2.2Vivado安装(2015.4为例)1)运行

2023-09-06 17:55:44

/ brix用户所在国家:美国用户语言:en用户区域设置:en_USRDI Base根目录:/ opt / Xilinx / VivadoRDI数据目录:/opt/Xilinx/Vivado/2016.2

2020-05-20 15:24:42

Vivado综合可以理解多种多样的RAM编写方式,将其映射到分布式RAM或块RAM中。两种实现方法在向RAM写入数据时都是采取同步方式,区别在于从RAM读取数据时,分布式RAM采用异步方式,块RAM

2020-09-29 09:40:40

。计数器为26位,led输出为4位,那么我们将位宽设置好,点击OK生成IP核。在这里,我们简要介绍一下Vivado的OOC(Out-of-Context)综合的概念。对于顶层设计,Vivado使用自顶向下

2023-04-17 16:33:55

/O管脚分析,可以参考表1-1管脚定义说明。2.Xilinx7系列FPGA管脚Pinout文件下载我们在进行原理图库设计时,如何获得FPGA每个管脚定义呢?在UG475官方文档第二章7 Series

2021-05-28 09:23:25

/O管脚分析,可以参考表1-1管脚定义说明。2.Xilinx7系列FPGA管脚Pinout文件下载我们在进行原理图库设计时,如何获得FPGA每个管脚定义呢?在UG475官方文档第二章7 Series

2021-07-08 08:00:00

开发设计流程。话不多说,上货。Xilinx FPGA Vivado 开发流程在做任何设计之前,我们都少不了一个工作,那就是新建工程,我们设计的一些操作,必须在工程下完成,那么接下来就向大家介绍一下新建工程的步骤

2023-04-13 15:18:52

不多说,上货。Xilinx FPGA 开发流程及详细说明本篇目录1. 设计前准备2. 建立工程3. 输入设计4. 综合分析5. RTL仿真6. 锁定管脚7. 布局布线8. 生成配置文件并下载9.

2023-03-30 19:04:10

都可配置成输入、输出。每个bank的首尾管脚只能作为单端I/O,其余48个I/O则可配置成24对差分I/O。在差分信号的实现过程中,管脚分配应选择相应电平标准的bank中除首尾以外的其他48个IO

2020-12-23 17:17:47

本帖最后由 lee_st 于 2017-10-31 08:43 编辑

Xilinx_FPGA下载烧写教程(超详细)

2017-10-21 21:00:16

Xilinx_FPGA下载烧写教程(超详细)

2017-09-30 08:57:48

Xilinx_FPGA下载烧写教程(超详细)Step by step 学习下载配置 Xilinx 之 FPGA配合 Mars-EDA 的 Spartan2 核心板,用图文方式向大家详细讲述如何下载配置 Xilinx的 FPGA。

2017-10-31 12:16:03

Xilinx工具:vivado在该图中,TX_CLK_i连接到pll_x1模块的输入时钟。然后,pll_x1的输出时钟连接到ODDR。接下来,ODDR的输出引脚将连接到I / O引脚

2020-05-04 08:04:41

,选择Create Port。2. 弹出窗口中,设置端口a为4位输入信号,并点击OK。3. 将a与A、B都连接起来。4. 同样的方法,添加一个8位输出端口p,与P连接。5. 再添加一个clk时钟输入

2018-05-15 12:05:13

vivado详细使用教程

2016-05-04 11:12:17

哪位大神能够分享一下关于xilinx vivado 2013.4 的教程啊,小弟感激不敬!!!

2014-03-26 21:38:02

xilinx EDF已经综合过的网表文件怎样添加到Vivado工程中?买了一个第三方的IP,给出了端口列表和核心模块发射机的.edf已经综合过的网表文件,该网表文件里面富含了大量的信息,我想知道edf文件怎样添加到Vivado工程中去?要不然的话,总是提示核心模块实例化失败!

2016-09-07 11:34:10

我用xilinx spartan-6fpga 它硬核的管脚是固定的还是可配置的我在xilinx提供的文档里找不到关于硬核管脚的分配求指导

2012-08-11 09:28:44

使用xilinx spartan6,在工程中使用原语生成DDR控制器mig文件,DDR数据管脚定义发生改变,需要重新分配管脚,求告知,这个管脚分配要怎么弄

2016-07-19 09:54:37

引言:本文我们介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题,指导硬件设计人员进行原理图及PCB设计。本文介绍以下内容:GTX/GTH收发器管脚概述GTX/GTH收发器时钟

2021-11-11 07:42:37

就是把HDL语言/原理图转换为综合网表的过程。2. 什么是综合网表?综合网表就是综合的结果啦。综合网表的业界标准是EDIF格式。文件后缀通常为.edn, .edf, .edif。EDIF网表是可以用

2018-08-08 10:31:27

使用OTG接口烧写方式也可以成为fastboot 烧写方式,下面介绍OTG方式烧写时 所使用的硬件和软件平台,然后再给大家介绍烧写过程的相关步骤,使用win10系统。硬件平台使用串口线连接开发板串口

2022-01-10 06:36:59

分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,quartus2中引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-04-03 07:00:00

更新! 支持BF70x系列芯片;支持新的仿真器,ICE-1000,和ICE-2000;一直在用BF60x做项目,但是CCES这个IDE没有烧写工具,需要在命令提示行下输入一对命令来实现烧写的功能

2018-10-24 09:23:52

是管脚的分配也必须在设计代码出来之前完成。所以,管脚的分配更多的将是依赖人,而非工具,这个时候就更需要考虑各方面的因素。 综合起来主要考虑以下的几个方面: 1 、 FPGA 所承载逻辑的信号流向。 IC

2012-08-11 10:27:54

FPGA管脚分配需要考虑的因素 FPGA 管脚分配需要考虑的因素 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好

2012-08-11 11:34:24

的 BANK 中。 2、 掌握 FPGA 内部 BANK 的分配的情况。现在 FPGA 内部都分成几个区域,每个区域中可用的 I/O 管脚数量各不相同。在 IC 验证中都是采用了ALTERA 与XILINX系列

2017-03-25 18:46:25

=FLASE绕过PAR的检查,这样就只是将本该接入专用时钟管脚(或者叫做全局时钟管脚)的信号,接到了普通IO口上,但并没有做好如何用普通IO口来引入全局时钟,Xilinx官方论坛上更是有老外直接指出这只

2019-07-09 08:00:00

FPGA验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑

2024-01-10 22:40:14

以及管脚分配后就可以进行综合和实现了。在过程管理区双击Synthesize-XST。如图所示可以得到资源使用的图标 综合可能有3种结果:如果综合后完全正确,则在Synthesize-XST前面有一个

2012-02-24 10:44:57

求助大神!!!FPGA对于DDR3读写,FPGA是virtex6系列配置MIG IP 核时,需要管脚分配1.原理图上dm是直接接地,管脚分配那里该怎么办2.系统时钟之类的管脚分配,是需要在原理图上找FPGA与DDR3之间的连线吗?还是?

2018-03-16 18:45:10

) ,打开Pin Planner,分配管脚外,还有以下2种方法。方法一:Import Assignments 步骤1:使用记事本或类似软件新建一个txt文件(或csv文件),按如下格式编写管脚分配内容

2018-07-03 12:56:11

,这没有意义。在Xilinx的Aurora示例设计中,Xdc文件不限制GTX的引脚位置,但在综合和实现之后,反射时钟在右引脚中分配没有问题。所以我很困惑为什么我的设计无法正常工作。我想知道之前

2019-03-01 09:18:11

1、关于stm32程序烧写问题:使用STM32 ST-LINK Utility进行烧写时,注意需要外部供电(还未测试)ST-LINK烧写的SWD模式 是ST-LINK烧写的一种方式,只需要4根接线

2021-12-10 07:06:13

文件烧写到外部配置存储器中。 选择好烧写的二进制文件,其他设置可以保持默认。二进制文件路径为:project_name_path \project_name.runs\impl_1

2016-12-27 20:22:29

在之前文章中对于NanoPi2的介绍都是在Windows环境下,但Windows环境中进行Linux开发存在一些局限性,从本篇开始介绍在Ubuntu环境中的开发过程。首先是Ubuntu环境下烧写系统

2016-06-05 14:54:55

本帖最后由 stone927 于 2015-11-4 22:43 编辑

【WRTnode2R试用体验】+烧写固件篇上一篇帖子介绍了编译自己的openwrt系统,今天将要演示如何将编译出的固件烧

2015-11-04 22:40:40

您好,我想下载Xilinx Vivado 2017.1但是,每次我收到以下错误:“由于您的帐户导出合规性验证失败,我们无法满足您的要求。”谁能帮我?提前致谢以上来自于谷歌翻译以下为原文Hello

2018-12-27 10:41:52

请问一下Xilinx公司发布的vivado具体的作用是什么,刚刚接触到,以前一直用quartus ii,没有使用过ise,后来今天听说了vivado,不知道是做什么用的,希望大家都能参与讨论中,谢谢。

2015-04-15 16:51:00

在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用 FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是

2015-01-06 17:38:22

嗨, 我们正在尝试将自定义IP连接到vivado的IP集成商中的可用IP。但我们在综合设计时发现了一些问题。请查看附带的截图以获取详细视图。谢谢。

2020-04-09 06:28:36

嗨,大家好,我正在使用Vivado 2014.对于设计,是使用BUFG或IBUF / OBUF原语到端口引脚还是工具将在分配PIN时自动获取缓冲区?我没有为时钟引脚A2YCLK0分配BUFG。在我

2019-04-03 13:28:08

。下面小编来详细介绍一下不同仿真模式的区别。 数字电路设计中一般包括3个大的阶段:源代码输入、综合和实现,而电路仿真的切入点也基本与这些阶段相吻合,根据适用的设计阶段的不同仿真可以分为RTL行为级仿真

2018-01-24 11:06:12

当我试图在Ubuntu的Synplify中调用xilinx for P& R时,它说XILINX变量尚未设置。我把它分配到vivado中的bin文件夹,但似乎是错误的。看起来Synplify

2018-12-19 11:04:40

请问各位大神如何使用PIC kit2烧写EEPROM程序,烧写软件的那两个复选框该如何处理?希望给出详细的步骤或说明,万分感谢~

2015-05-22 11:50:42

如何通过设置boot引脚来实现ISP串口烧写?

2021-12-06 07:16:07

前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 09:38:32

无法使用基于ISE的策略运行综合和实施,或导入ngc网表。请设置XILINX环境以获得完整功能。source run_ippack.tcl -notrace确实在我打开vivado并添加我的IP并完成我

2020-04-03 08:48:23

嗨,我想创建一个设计,我需要2Mhz clk,我想用16Mhz输入时钟的vivado套装中的“时钟向导”IP核生成它。根据Xilinx手册(下面的链接),这可以通过CLKOUT4_CASCADE选项

2020-07-27 06:32:48

1. 批文件中需要设置jlink.exe的路径,你也可以使用环境变量来设置,以便可以找到jlink.exe程序。2. loadfile命令后面要烧写的文件必须存在,或者通过设置环境变量指定我们使用的工程

2020-10-19 13:48:07

今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

上一篇《Tcl 在 Vivado 中的应用》介绍了 Tcl 的基本语法以及如何利 用 Tcl

2023-06-28 19:34:58

你好,请问有没有用SD卡烧写的详细步骤,我用的是LCDK6748板子。我看这个网页讲的不是很详细:http://processors.wiki.ti.com/index.php/OMAP-L138_Preparing_SD_Card_for_Boot#CCS,CCS调用SDMMCWriter_DSP.pjt

2020-05-21 13:34:21

嗨,你能告诉我在闪存存储器MT29F1G08ABADAWP-IT:D的vivado工具中设置的设置,来自制造商Micron与Xilinx Zynq Soc XC7Z020-2CLG400I一起

2019-03-27 10:14:33

1、跨时钟域信号的约束写法 问题一:没有对设计进行全面的约束导致综合结果异常,比如没有设置异步时钟分组,综合器对异步时钟路径进行静态时序分析导致误报时序违例。 约束文件包括三类,建议用户应该将

2022-11-15 14:47:59

亲爱的大家,我现在正在使用Vivado 2013.3。我试图将PL结构时钟从1 MHZ更改为500KHZ。 (1 MHZ下没问题)但是,Vivado在运行综合时崩溃了。对我来说减少PL结构时钟非常重要,因为我打算在一个时钟周期内收集更多的XADC数据。我该怎么办?谢谢!

2020-03-25 08:40:07

本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 FPGA学习资料教程之Xilinx-FPGA-引脚功能详细介绍

2016-09-01 15:27:27 0

0 设计过FPGA的原理图,看FPGA的手册,说管脚的分配问题,如时钟管脚要用GC类管脚,而且单端时钟输入时要用P类型的管脚,不能用N类型管脚等等。

2017-02-11 03:48:34 10684

10684

Vivado时钟的两大特性--时钟延迟和时钟的不确定性。

2017-11-17 11:38:01 5381

5381

使用Xilinx Vivado HLS(Vivado 高层次综合)工具实现浮点复数QRD矩阵分解并提升开发效率。使用VivadoHLS可以快速、高效地基于FPGA实现各种矩阵分解算法,降低开发者

2017-11-17 17:47:43 3293

3293

在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配

2017-11-22 07:09:36 8891

8891

本文介绍一下xilinx的开发软件 vivado 的仿真模式, vivado的仿真暂分为五种仿真模式。 分别为: 1. run behavioral simulation-----行为级仿真,行为

2018-05-29 13:46:52 7674

7674 介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。所以首先要设计合理,才可能满足约束,约束反过来检查

2018-06-25 09:14:00 6374

6374 本文档的主要内容详细介绍的是MicroBlaze(Vivado版)设置说明详细资料免费下载开始IP综合设计(步骤)

1、在工作流导向面板中的IP Integrator中,点击Create

2018-09-05 08:00:00 0

0 本文档的主要内容详细介绍的是STM32时钟系统时钟树和时钟配置函数介绍及系统时钟设置步骤资料。

2018-10-11 08:00:00 22

22 本文通过一个简单的例子,介绍Vivado 下的仿真过程。主要参考了miz702的教程,同时也参考了Xilinx的ug937, xapp199.。

2018-11-10 10:53:51 37132

37132 了解如何使用Vivado设计套件的电路板感知功能快速配置和实施针对Xilinx评估板的设计。

2018-11-26 06:03:00 3062

3062 在Vivado Design Suite中,Vivado综合能够合成多种类型的属性。在大多数情况下,这些属性具有相同的语法和相同的行为。

2019-05-02 10:13:00 3750

3750 从 Vivado 2019.1 版本开始,Vivado 综合引擎就已经可以支持增量流程了。这使用户能够在设计变化较小时减少总的综合运行时间。

2019-07-21 11:02:08 1367

1367 1 I/O延迟约束介绍 要在设计中精确建模外部时序,必须为输入和输出端口提供时序信息。Xilinx Vivado集成设计环境(IDE)仅在FPGA边界内识别时序,因此必须使用以下命令指定超出这些边界

2020-11-29 10:01:16 4315

4315 本章介绍了 Xilinx公司的ISE52中的综合工具XST的综合属性、HDL代码参数设置、专用参数选项设置,使用XST综合设计、实行设计的步骤与方法。ISE5.2集成的下载配置工具 IMPACT的结构、操作步骤与方法。 Altera公司的Quartus3.0编译器和编程器的使用步骤与方法。

2021-03-11 11:35:05 26

26 Xilinx_Vivado_zynq7000入门笔记说明。

2021-04-08 11:48:02 70

70 Vivado 的XDC设置输出延时 Vivado 的XDC设置输出延时,用于输出伴随时钟和数据的,数据是由系统时钟125M驱动,伴随时钟是由125M经过Pll相位移动-90度。 设置输出时钟

2021-06-09 17:28:01 3888

3888

LOCK_PINS 是 Xilinx Vivado 做物理约束的属性之一。用来将LUT的逻辑输入(I0,,I1,I2...)绑定到其物理输入pin上(A6,A5,A4...)。

2023-01-11 10:52:24 768

768 今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

2023-05-05 09:44:46 674

674

本文主要介绍Vivado布线参数设置,基本设置方式和vivado综合参数设置基本一致,将详细说明如何设置布线参数以优化FPGA设计的性能,以及如何设置Vivado压缩BIT文件。

2023-05-16 16:40:45 2957

2957

如果你正在使用Vivado开发套件进行设计,你会发现综合设置中提供了许多综合选项。这些选项对综合结果有着潜在的影响,而且能够提升设计效率。为了更好地利用这些资源,需要仔细研究每一个选项的功能。本文将要介绍一下Vivado的综合参数设置。

2023-05-16 16:45:50 1857

1857

电子发烧友网站提供《为EBAZ4205创建Xilinx Vivado板文件.zip》资料免费下载

2023-06-16 11:41:02 1

1 Vivado综合默认是timing driven模式,除了IO管脚等物理约束,建议添加必要的时序约束,有利于综合逻辑的优化,同时综合后的design里面可以评估时序。

2023-07-03 09:03:19 414

414 本文详细介绍了vivado软件和modelsim软件的安装,以及vivado中配置modelsim仿真设置,每一步都加文字说明和图片。

2023-08-07 15:48:00 1478

1478

之一。对于S3C2440来说,正确设置系统时钟是实现其高效稳定运行的前提条件之一。本文将详细介绍如何设置S3C2440的系统时钟。 一、 S3C2440的时钟系统架构 在了解如何设置S3C2440的系统时钟之前,我们需要先了解一下S3C2440的时钟系统架构。 我们可以看到S3C2440的时钟系统主

2023-09-02 15:12:42 488

488

正在加载...

电子发烧友App

电子发烧友App

评论