1. OFFSET约束的写法

Offset 约束定义了外部时钟pad和与之相关的输入、输出pad之间的相对关系。这是一个基础的时序约束。Offset定义的是外部之间的关系,不能用在内部信号上。

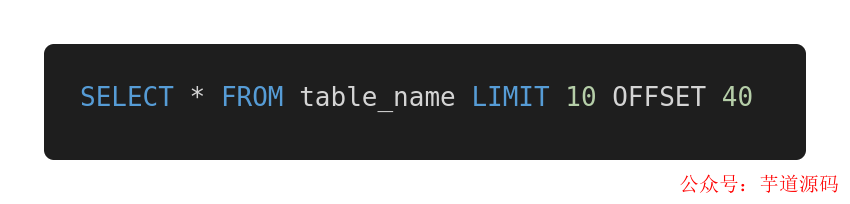

OFFSET约束写起来还是比较简单的,如

OFFSET = {IN|OUT} offset_time [units] {BEFORE|AFTER} clk_name [TIMEGRP group_name];

offset_time: 捕获时钟沿和数据起始时间之差,默认单位为ns,可以定义为ns、ps等

BEFORE|AFTER:和本意类似

clk_name: 输入clock pad net 的层次化全称

offset_time 写多少取决于数据之间所需要的相对关系,另外,弄懂XST是如何分析时序关系也是十分重要的。

2. OFFSET IN 分析

下面的式子是UG612中指出的时序要求需要满足的关系,看着可能不是太明白,但是结合例子分析就容易理解了。下面的式子给出的要求是Toffset_IN_BEFORE - (TData + TSetup - TClock) > 0 ,实际上就对应着slack 大于0 。 具体表述如下(分别为建立时间和保持时间要求)

TData + TSetup - TClock <= Toffset_IN_BEFORE

where

TSetup = Intrinsic Flip Flop setup time

TClock = Total Clock path delay to the Flip Flop

TData = Total Data path delay from the Flip Flop

Toffset_IN_BEFORE = Overall Setup Requirement

TClock - TData + Thold <= Toffset_IN_BEFORE_VALID

where

Thold = Intrinsic Flip Flop hold time

TClock = Total Clock path delay to the Flip Flop

TData = Total Data path delay from the Flip Flop

Toffset_IN_BEFORE_VALID = Overall Hold Requirement

文档中还提到了Hold time的需求,建立时间和保持时间在上文有介绍。UG612这里是个大坑,给出了这个式子之后就再也没有讨论过hold time了。之前的WP327(WP327部分内容错误,UG612有修正)倒是提到了这一点

“The OFFSET IN requirement value is used as a setup time requirement of the FPGA during the setup time analysis. The VALID keyword is used in conjunction with the requirement to create a hold-time requirement during a hold-time analysis. The VALID keyword specifies the duration of the incoming data valid window, and the timing analysis tools perform a hold-time analysis. By default, the VALID value is equal to the OFFSET time requirement, which specifies a zero hold-time requirement. See Figure 6."

这一段介绍了hold time 的处理方法。如果指定了数据的VALID 时间,那么hold time 的requirement 是确定的,这样能够进行具体的分析;如果没有确定,那么默认认为hold-time 的requirement 是0 。

3.OFFSET IN 举例

Simple Example

Slack: -0.191ns (requirement - (data path - clock path - clock arrival + uncertainty))

Source: reset (PAD)

Destination: my_oddrA_ODDR_inst/FF0 (FF)

Destination Clock: clock0_ddr_bufg rising at 0.000ns

Requirement: 3.000ns

Data Path Delay: 2.784ns (Levels of Logic = 1)

Clock Path Delay: -0.168ns (Levels of Logic = 3)

Clock Uncertainty: 0.239ns

上面的例子首先告诉我们,OFFSET_IN约束是3ns,也就是说对于输入数据在采样时钟沿前3ns有效。那么在触发器上能否正确采样取决于:触发器采样时钟延迟了-0.168,故多提前了-0.168ns;data path delay是2.784,故数据延迟2.784;源、目的端时钟关系为0,不变;不确定性带来坏的影响,有

slack = 3 + (-0.168) -2.784 - 0.239 +0;

Phase-Shifted Example

Slack: 2.309ns (requirement - (data path - clock path - clock arrival + uncertainty))

Source: reset (PAD)

Destination: my_oddrA_ODDR_inst/FF0 (FF)

Destination Clock: clock90_bufg rising at 2.500ns

Requirement: 3.000ns

Data Path Delay: 2.784ns (Levels of Logic = 1)

Clock Path Delay: -0.168ns (Levels of Logic = 3)

Clock Uncertainty: 0.239ns

分析过程类似,不过我们注意到在定义的时候,相对值是clock,但是触发器采样的时钟是clk90(Destination)。这也就意味着我们多了一个clock arrival time,这个值是2.5ns。其余和上面的例子是一样的。

那么回到之前的式子Toffset_IN_BEFORE - (TData + TSetup - TClock) > 0 ;分析报告中的requirement 实际上就是Toffset_IN_BEFORE,data path包括了TData 和 TSetup,TClock实际上就是clock arrival 和clock path delay。这个式子是没有考虑到clock uncertainty 的。

在结束这一节之前,还要提及一个很奇怪的,不知道为何要存在的概念。之前没有特别说明,对于OFFSET IN约束来说,写法大抵是

OFFSET = IN 3ns BEFORE clock;

采用before是很自然的,因为我们一直在分析建立时间,建立时间就是恰恰是采样沿之前。OFFSET IN还可以这样写,即(不明白为什么要有这个样子的写法)

OFFSET = IN 2 ns AFTER clock_pad

此时对应的需要满足的条件是

TData + TSetup - TClock <= TPeriod - Toffset_IN_AFTER

where

TSetup = Intrinsic Flip Flop setup time

TClock = Total Clock path delay to the Flip Flop

TData = Total Data path delay from the Flip Flop

TPeriod = Single Cycle PERIOD Requirement

Toffset_IN_AFTER = Overall Setup Requirement

4. OFFSET OUT 分析

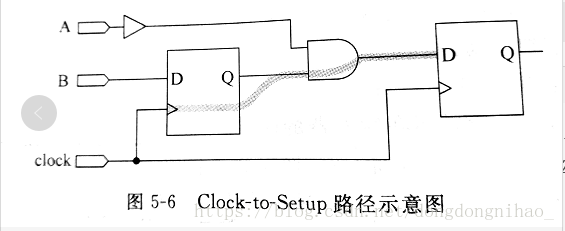

OFFSET OUT 约束是FPGA到下游的器件的时钟、数据之间的相对关系,具体可以用下图来表示。具体约束要求,下游器件接收到的数据会在时钟沿之后多久之内到达。那么,根据这一幅图可以得出Clock to Out = clock_delay + clock_to_out + data_delay + clock_arrival。这是因为FPGA内部的触发器的时钟延迟了clock path,同时由于触发器的触发时间,FPGA触发器输出就延时了clock_delay+clock_to_out时间,同时数据还有延迟。另,图中给出的是一种情况,这种情况下clock_arrival = 0,最后的结果还需要加上clock_arrival.

根据这一相对关系,可以得出FPGA时序需要满足的关系

TQ + TData2Out + TClock <= Toffset_OUT_AFTER

where

TQ = Intrinsic Flip Flop Clock to Out

TClock = Total Clock path delay to the Flip Flop

TData2Out = Total Data path delay from the Flip Flop

Toffset_OUT_AFTER = Overall Clock to Out Requirement

具体的分析和OFFSET IN的类似,这里不再重复,同样给出几个例子。

例子分析

Simple Example

Slack: -0.865ns (requirement - (clock arrival + clock path + data path + uncertainty))

Source: OutD_7 (FF)

Destination: OutD<7> (PAD)

Source Clock: clock3_std_bufg rising at 0.000ns

Requirement: 3.000ns

Data Path Delay: 3.405ns (Levels of Logic = 1)

Clock Path Delay: 0.280ns (Levels of Logic = 3)

Clock Uncertainty: 0.180ns

电子发烧友App

电子发烧友App

评论