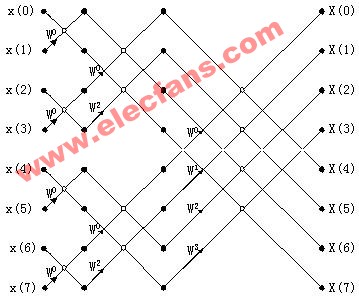

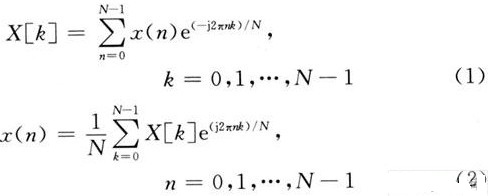

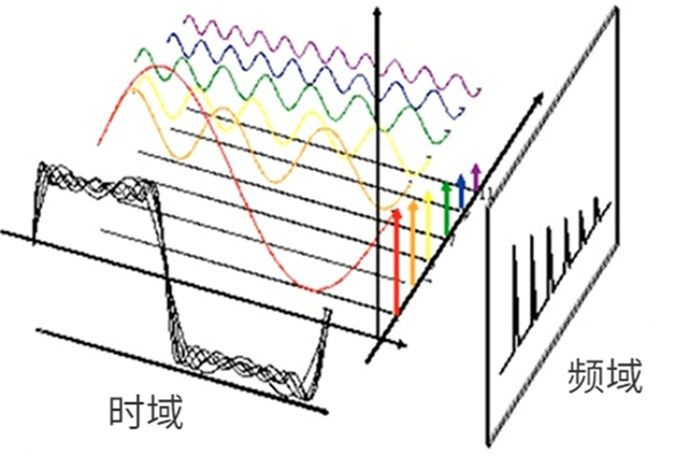

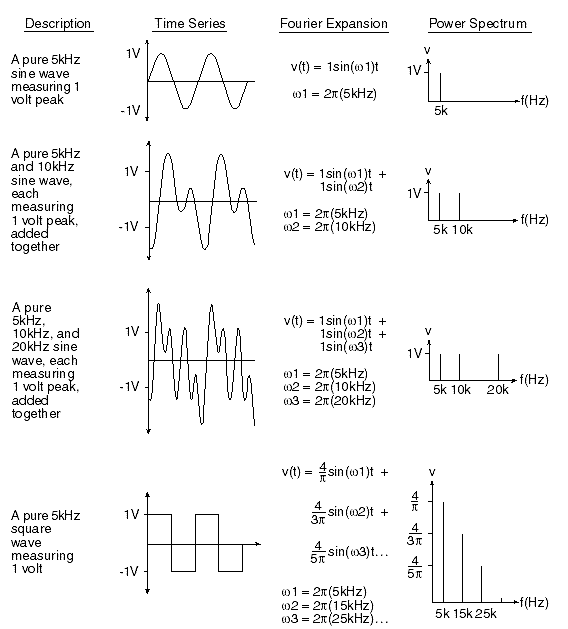

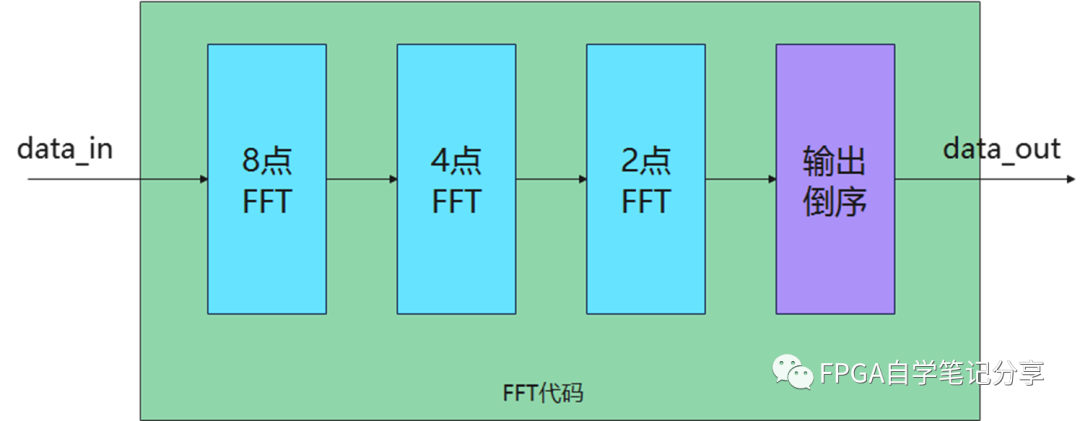

fft输入输出解析。

输入:fft要求输入一个复数,但一般可以只输入实数。

输出:输出一个复数,其模为信号强度。相位为波形相位。

设:

采样频率FS

转换长度N

则:

分辨率为FS/N。

‘量程’为-FS/2~FS/2

提高采样频率则可提高量程,却会(在转换长度不变的情况下)降低分辨率。此时需要通过增加转换长度的方式增加分辨率,但却会增加处理时间。

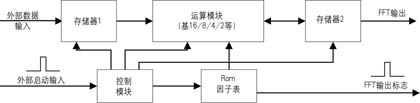

相关ip核:

FFT V7.1:适用于Spartan3E系列,输入输出为wire或reg型。

FFT V8.0:使用AXI_STREAM总线协议。

FFT V9.0:使用AXI_STREAM总线协议,适用zyqn。

fftV7.1 ip核仿真实例:

开发环境:xilinx ISE+modelsim

选择设备,添加ip核,编写仿真文件

仿真文件如下

module test;

// Inputs

reg clk;

reg start;

reg fwd_inv;

reg fwd_inv_we;

reg scale_sch_we;

reg [15:0] xn_re;

reg [15:0] xn_im;

reg [11:0] scale_sch;

// Outputs

wire rfd,irfd;

wire busy,ibusy;

wire edone,iedone;

wire done,idone;

wire dv,idv;

wire [9:0] xn_index;

wire [9:0] xk_index;

wire [9:0] ixn_index;

wire [9:0] ixk_index;

wire [15:0] xk_im_t;

wire [15:0] xk_re_t;

wire [15:0] ixk_im_t;

wire [15:0] ixk_re_t;

wire [32:0] out;

wire signed [15:0] xk_re;

wire signed [15:0] xk_im;

wire signed [15:0] ixk_re;

wire signed [15:0] ixk_im;

wire [16:0] getifft;

// Instantiate the Unit Under Test (UUT)

fft uut (

.clk(clk),

.start(start),

.fwd_inv(fwd_inv),

.fwd_inv_we(fwd_inv_we),

.scale_sch_we(scale_sch_we),

.rfd(rfd),

.busy(busy),

.edone(edone),

.done(done),

.dv(dv),

.xn_re(xn_re),

.xn_im(xn_im),

.scale_sch(scale_sch),

.xn_index(xn_index),

.xk_index(xk_index),

.xk_re(xk_re),

.xk_im(xk_im)

);

complent inst1(ixk_re,ixk_re_t);

complent inst2(ixk_im,ixk_im_t);

assign out = ixk_re_t[14:0]*ixk_re_t[14:0]+ ixk_im_t[14:0]*ixk_im_t[14:0];

sqrt your_instance_name (

.x_in(out), // input [15 : 0] x_in

.x_out(getifft), // output [8 : 0] x_out

.clk(clk) // input clk

);

/*

fft iuut (

.clk(clk),

.start(dv),

.fwd_inv(~fwd_inv),

.fwd_inv_we(fwd_inv_we),

.scale_sch_we(0),

.rfd(irfd),

.busy(ibusy),

.edone(iedone),

.done(idone),

.dv(idv),

.xn_re(xk_re),

.xn_im(xk_im),

.scale_sch(0),

.xn_index(ixn_index),

.xk_index(ixk_index),

.xk_re(ixk_re),

.xk_im(ixk_im)

);

*/

ifft iuut (

.clk(clk),

.start(dv),

.fwd_inv(~fwd_inv),

.fwd_inv_we(fwd_inv_we),

.rfd(irfd),

.busy(ibusy),

.edone(iedone),

.done(idone),

.dv(idv),

.xn_re(xk_re),

.xn_im(xk_im),

.xn_index(ixn_index),

.xk_index(ixk_index),

.xk_re(ixk_re),

.xk_im(ixk_im)

);

initial begin

// Initialize Inputs

clk = 0;

start = 1;

fwd_inv = 1;

fwd_inv_we = 1;

scale_sch_we = 1;

xn_re = 0;

xn_im = 0;

scale_sch = 12'b101010101011;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

end

always #50

begin

xn_re[14]=(~xn_re[14]);

end

always #1

clk=~clk;

endmodule

module complent(

input [15:0] complent,

output [15:0] truecode

);

wire [14:0]temp1;

wire [15:0]temp2;

assign temp1=complent[15]==0?complent[14:0]:~(complent[14:0]);

assign temp2={complent[15],temp1};

assign truecode= temp2 + 1;

endmodule

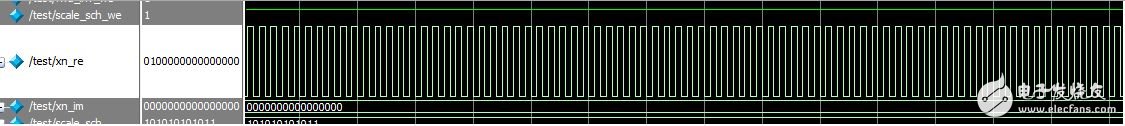

使用modelsim结果如下

输入波形

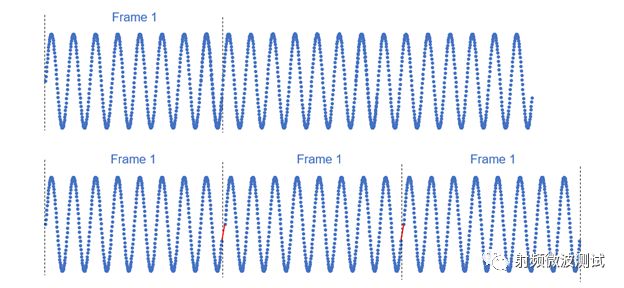

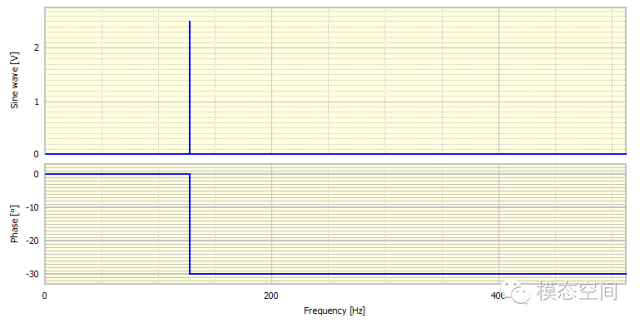

fft输出波形,包括实部和虚部

ifft输出波形(实部和虚部),和经变换后的输出波形

电子发烧友App

电子发烧友App

评论