2月12日,自适应和智能计算的全球领导企业赛灵思公司(Xilinx)宣布已将完整的HDMI 2.1 IP子系统引入其知识产权核(IP核)产品组合中,使得各种搭载赛灵思器件的专业音视频设备能够发送

2019-02-13 10:49:01 3095

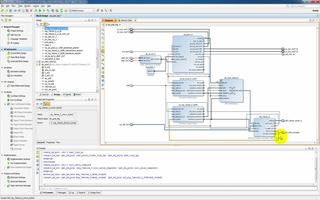

3095 大家好,欢迎Vivado的一个快速演示,它是xilinx新的设计套件,应用到7系列和以上的系列器件。

2012-04-25 08:55:55 2192

2192 双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 403

403

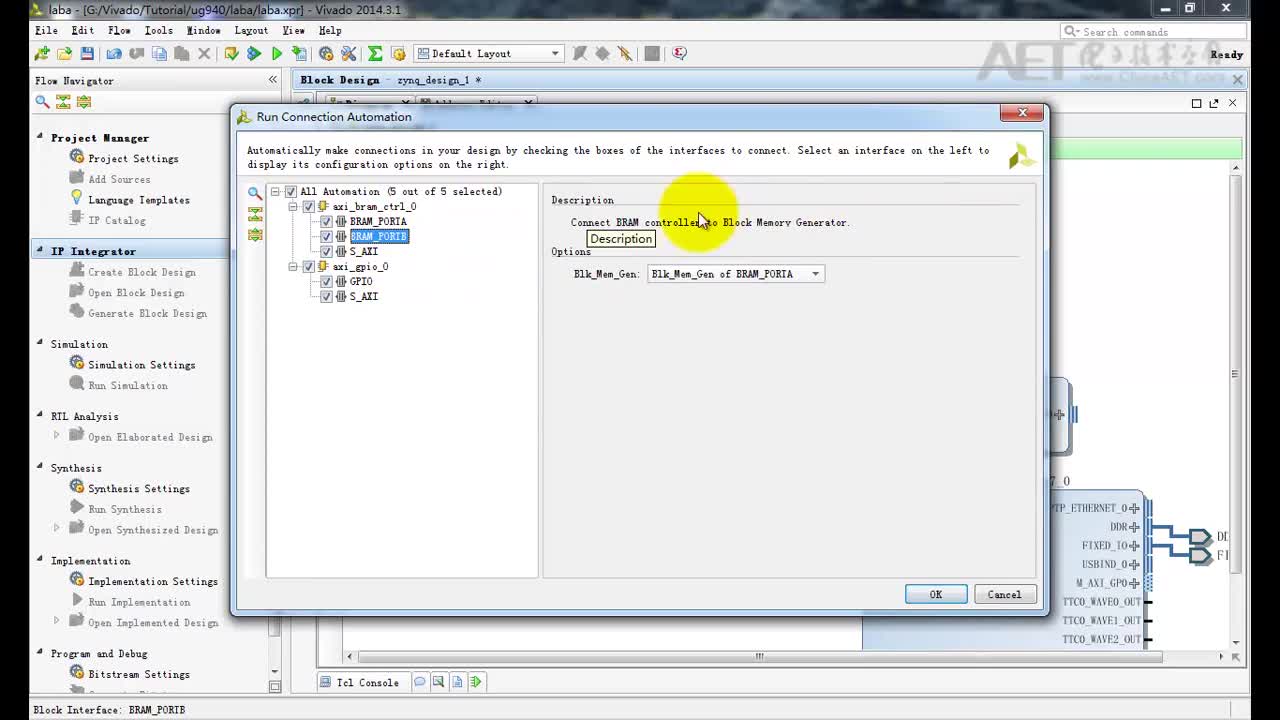

嗨,我正在使用Vivado 13.2在Zynq 7000上实现嵌入式设计。这是我的设计流程1)创建了一个新项目my_ip,其中包含1个ngc文件和2个从Xilinx Fifo Generator生成

2020-04-15 10:22:15

我尝试使用Vivado 2016.2实现与2015.3相同的设计(https://github.com/Elphel/x393),2016年使用更多资源并且无法计时。我尝试了干净启动(新项目,只是

2018-10-29 14:15:05

在模拟模型方面,Vivado提供的IP似乎有一些根本性的变化。在将工作设计从ISE 14.4转换为Vivado 2013.2之后,然后按照建议的方式升级大部分Xilinx IP,例如基本乘法器,除法

2019-02-26 10:42:23

Xilinx设计工具ISE设计套件系统版+ Vivado系统版14.3是否可以为此版本的软件进行静默安装?任何意见,将不胜感激干杯以上来自于谷歌翻译以下为原文Xilinx Design Tools

2018-12-28 10:53:04

Vivado中xilinx_courdic IP核(求exp指数函数)使用

2021-03-03 07:35:03

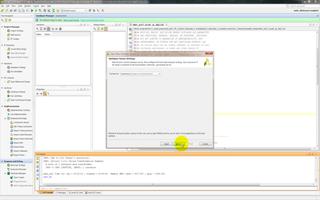

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

你好,我们在2016年3月购买了Xilinx-Vivado / Ise的完整版本。我的同事将我添加为“管理员”,因此我也可以创建许可证。但它没有显示在我的xilinx帐户中,因此我无法生成许可证。我

2018-12-21 11:00:57

的新一代开发环境,致力于解决系统级集成和实现的生产力瓶颈。 Vivado Design Suite 在总体生产力、易用性和系统级集成能力方面领先一代。加速实现设计实现时间缩短 4 倍设计密度提升 20%高达

2014-12-23 13:11:08

Xilinx在Artix设备上是否有6G-SDI的IP?我发现一些旧的信息提到它为Vivado但它似乎不在IP目录中。谢谢

2020-07-24 06:32:48

菜鸟求指教,最近在用vivado 2015.3 做个小项目,遇到问题:代码综合后会报错:'get_property' expects at least one object.错误地址在IP的 clocks.xdc文件中。

2016-08-31 10:42:56

,int b);最后经过编译可以生成VHDL等硬件描述文件与IP核文件.我想调用自己写的IP核(add函数)我在vivado 中添加了自定义IP核与PS(处理系统)我知道网上说用AXI Steam? 来连接

2016-01-28 18:40:28

,int b);最后经过编译可以生成VHDL等硬件描述文件与IP核文件.我想调用自己写的IP核(add函数)我在vivado 中添加了自定义IP核与PS(处理系统)我知道网上说用AXI Steam? 来连接

2016-01-28 18:39:13

本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

2021-03-02 07:22:13

哪位大神能够分享一下关于xilinx vivado 2013.4 的教程啊,小弟感激不敬!!!

2014-03-26 21:38:02

:www.xilinx.com/products/intellectual-property/temac-evaluation.html在该页面的大约一半处,在其中显示完整系统硬件评估的位置,我点击“处理器IP评估

2020-04-21 08:40:43

请问怎样将混合信号电压基准提升至更高的电平?

2021-04-13 06:06:23

您好,我想下载Xilinx Vivado 2017.1但是,每次我收到以下错误:“由于您的帐户导出合规性验证失败,我们无法满足您的要求。”谁能帮我?提前致谢以上来自于谷歌翻译以下为原文Hello

2018-12-27 10:41:52

早安Xilinx Communitry,我有一个关于VIVADO IP中心设计流程的问题。设计针对Xilinx fpga的数字逻辑不仅仅有一种方法。您可以使用HLS和HDL进行设计。您可以使用纯

2019-03-29 09:14:55

你好,我正在尝试使用Xilinx IP内核进行简单的hdmi passthrough。我正在将TMDS直接馈送到FPGA。我不确定tdms线和时钟应该去哪里。这是我到目前为止所得到的。使用以

2020-08-11 10:33:03

请问一下Xilinx公司发布的vivado具体的作用是什么,刚刚接触到,以前一直用quartus ii,没有使用过ise,后来今天听说了vivado,不知道是做什么用的,希望大家都能参与讨论中,谢谢。

2015-04-15 16:51:00

,但现在有了Vivado,我没有看到这样的应用程序我希望Xilinx不要像许多其他应用程序那样放弃这个应用程序以上来自于谷歌翻译以下为原文Hello everyone Can I Install

2018-12-27 10:57:02

的Windows 10更新。现在甚至没有完全控制将允许我在我的用户上使用Vivado。但是它仍然适用于我的管理员。当我查找位于C:\ Xilinx \ Vivado \ 2015.3 \ bin

2019-01-02 14:41:39

HI, 我正在尝试使用浮点IP在Zedboard上生成一个系统(SoC)(使用VIVADO 2016.4)。由于这个IP具有分层接口,我使用AXI DMA将此ip添加到AXI系统总线。但现在我的问题是如何使用Xilinx SDK检查此IP? (表示如何向IP发送输入以及如何检查输出)。谢谢

2020-05-26 14:04:10

我试图在Vivado 2015.3中运行Zynq基础TRD 2015.2。我无法看到程序框图的详细信息(如附件中所示)。它显示为IP。有没有办法查看内容?

2020-04-28 08:47:59

前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 09:38:32

您好,我正在为Vivado 2015.3课程做一个项目。该项目是边界扫描测试。我编写了所有VHDL代码并尝试实现。但是,实施还没有发生。我一直得到错误:[Synth 8-4169]使用条款中的错误

2019-04-15 12:38:48

你好我正在尝试在vivado HLS中创建一个IP,然后在vivado中使用它每次我运行Export RTL我收到了这个警告警告:[Common 17-204]您的XILINX环境变量未定义。您将

2020-04-03 08:48:23

嗨,我试图下载Vivado 2015.3完整安装程序所有操作系统版本,但我收到以下错误。错误由于技术问题,我们无法满足您的要求。请稍后再试。请不要单击后退按钮。如果您反复收到此错误,请稍后再试,并发

2019-04-16 15:17:58

和Digi-Key说话,他们似乎一无所知。我也打电话给AVNet,他们说他们很乐意帮忙,但他们需要产品/部件号。我还试着打电话给Xilinx,他告诉我和经销商谈谈。是否可以续订我们的Vivado系统

2018-12-24 13:49:08

组件,这样我就不必浪费时间了?过度查看可能导致调试时间大幅下降的事情的可能性很大。我正在使用Xilinx Vivado。我目前的设计是在2015.3(部分已经在2015年4),我想迁移到2016.2

2018-12-19 11:07:18

使用active_hdl 12.0 仿真xilinx IP。按照文档,在vivado中编译好了用于active_hdl 12.0的IP库,并在active_hdl软件中完成添加。同时将vivado

2022-09-25 22:46:59

dear all:求教 Vivado 问题!vivado 2015.3generate bitstream 后报错:[DRC 23-20] Rule violation (REQP-38

2016-09-23 11:36:04

我已获得Xilinx HDMI IP内核的评估许可证,并已将其加载到许可证管理器中。我的IP经理似乎缺少实际的IP本身。我已经检查了计算机上的Xilinx文件夹,但找不到任何文件。我找到了名为

2019-01-02 15:02:41

ISE指出)。由于Xilinx已将设计师推向PlanAhead和Vivado,因此设计方向似乎朝着更高层次的方向发展,从设计师那里去除了设计控制的某些方面。图形架构,C到VHDL HLS,以及

2019-07-29 07:54:51

我正在尝试在VC707上构建和测试AXI以太网子系统。但是write_bitstream错误输出时出现以下错误:[Common 17-69]命令失败:此设计包含一个或多个不允许生成比特流的单元

2020-08-21 11:07:27

嗨,我面临与Vivado 2015.3类似的问题。我在linux中有我的设计,想要调试一些东西。所以我做了以下配置。1.我在windows机器上下载并安装了vivado_lab_2015.3。2.

2020-04-26 12:34:20

大家好,我正在尝试使用Vivado IP集成块设计开发设计。我使用了Xilinx Repository中的几个IP块以及我自己的一些简单块。我只使用了块设计,并没有自己做任何放置。我也没有添加约束

2018-10-30 11:10:33

IP多媒体子系统-媒体网关功能有哪些?

IP多媒体子系统-媒体网关功能(IMS-MGF)

IMS-MGF终结来自电路交换网的

2010-04-07 16:24:10 727

727 赛灵思公司 (Xilinx, Inc. (NASDAQ:XLNX) )今天公开发布以 IP及系统为中心的新一代颠覆性设计环境 Vivado 设计套件

2012-04-25 08:51:15 1229

1229 Xilinx发布Vivado Design Suite 2013.3版本,新增最新UltraFast设计方法及新一代即插即用IP和部分重配置功能,丰富设计流程,实现前所未有的IP易用性, 进一步提高设计生产力

2013-12-24 17:51:23 1193

1193 testbench来验证设计。 Integrate带有Xilinx IP Block的 HLS IP 这里展示了在IP Integrator中,如何将两个HLS IP blocks跟Xilinx IP FFT结合在一起 ,并且在Vivado中验证设计。

2017-02-07 17:59:29 4179

4179

本文基于xilinx 的IP核设计,源于音频下采样这一需求。 创建vivado工程 1. 首先打开vivado,创建一个新的project(勾选create project subdirectory

2017-02-08 02:25:09 3716

3716

Xilinx采用先进的 EDA 技术和方法,提供了全新的工具套件Vivado,面向未来“All-Programmable”器件。Vivado开发套件提供全新构建的SoC 增强型、以IP和系统为中心

2017-02-08 04:10:11 457

457 及 Xilinx 技术专家共聚一堂。 在这为期一天的活动中,您可以学习各种有关 Vivado 的高级功能、使用技巧及设计窍门,以提升您的 FPGA/SoC 设计生产力: 主题演讲将涵盖行业趋势和 Xilinx

2017-02-08 06:04:03 204

204 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言

2017-02-08 13:08:11 1235

1235

HLx 版本均包括带有 C/C++ 库的 Vivado 高层次综合 (HLS)、Vivado IP 集成器 (IPI)、LogicCORE™ IP 子系统以及完整的 Vivado 实现工具套件,使主流用户能够方便地采用生产力最高、最

2017-02-08 19:35:06 386

386 赛灵思(Xilinx)近期宣布推出高阶设计工具2015.3版DSP系统产生器(System Generator),可让系统工程师运用Xilinx All Programmable组件设计高效能DSP系统。

2019-10-06 18:00:00 283

283 无缝集成在其设计中的工作。该 IP 集成工具支持针对所有 Xilinx 器件提供,其中包括最新 UltraScale 器件系列,可充分满足 Vivado 设计套件工具 2014.4 以及更高版本的要求。 了解更多 »

2017-02-09 08:12:36 319

319

有关FPGA——VIVADO15.4开发中IP 的建立

2017-02-28 21:04:35 15

15 Xilinx的Vivado采用原理图的设计方式,比较直观适合大型项目,我们自己的code都需要封装成user IP。这里主要介绍怎么把多个关联管脚合并成类似bus的大端口。

2017-09-15 16:54:34 42

42 在给别人用自己的工程时可以封装IP,Vivado用封装IP的工具,可以得到像xilinx的ip一样的可以配置参数的IP核,但是用其他工程调用后发现还是能看到源文件,如何将工程源文件加密,暂时没有找到方法,如果知道还请赐教。

2018-06-26 11:33:00 7425

7425 面向未来十年All Programmable,一个以IP及系统为中心的工具套件,把可编程系统的集成度和实现速度提升至原来的4倍。赛灵思公司(Xilinx)2012年4月25日美国发布会现场及答记者问

2018-06-05 13:45:00 3756

3756 大家好,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。 首先咱们来了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 36234

36234 本篇记录了本人解决xilinx下载器驱动安装问题(装驱动提示错误如下图)。主要过程就是更新到win10,再重装驱动即可,最后测试在Vivado2015.3中可以成功下载调试。 电脑环境 操作系统

2018-08-07 13:47:42 5154

5154 赛灵思公司(Xilinx)今天宣布推出可编程行业唯一 SoC 增强型设计套件Vivado设计套件 的2014.3版本、SDK 和最新 UltraFast 嵌入式设计方法指南,为 Zynq-7000

2018-09-06 16:07:00 1466

1466 关键词:Vivado , 设计套件 赛灵思公司(Xilinx)今天宣布, 其业界首款可编程SoC级增强型Vivado设计套件的最新版本在生产力方面进行了两大改进。Vivado设计套件2013.1版本

2018-09-25 09:18:01 275

275 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-20 06:55:00 2340

2340 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-20 06:56:00 2512

2512 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-29 06:32:00 3340

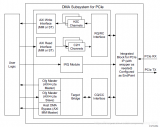

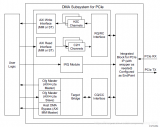

3340 了解如何使用Xilinx的Vivado IP Integrator(IPI)快速轻松地组合将PCI Express连接到外部DDR存储器的完整子系统。

该视频将展示如何配置和连接所有Xilinx IP,包括AXI ......

2018-11-28 06:38:00 4916

4916

了解如何创建和使用Xilinx的UltraScale PCI Express解决方案。

使用Vivado IP目录GUI创建和使用PCI Express IP内核。

打开示例设计并在Vivado软件中实现它。

2018-11-28 06:36:00 3424

3424

本视频介绍了设置和测试Xilinx PCIe DMA子系统性能的过程。

2018-11-27 06:16:00 6069

6069 了解如何使用Vivado设计套件的电路板感知功能快速配置和实施针对Xilinx评估板的设计。

2018-11-26 06:03:00 3062

3062 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-30 19:24:00 4251

4251 在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

2018-12-22 14:26:38 4468

4468 赛灵思的新型LogiCOREIP子系统属于高度可配置并根据市场量身定制的构建模块,其集成了多达80个不同的IP 核、软件驱动程序、设计实例和测试平台。

2019-07-31 09:05:58 1570

1570 DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 开发工具:Vivado

2020-11-26 15:02:11 7386

7386

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP

2020-12-29 15:59:39 9496

9496 本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2022-07-25 17:45:48 3057

3057

本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2021-01-31 08:12:02 8

8 Vivado2017.2 中BRAM版本为 Block Memory Generator Specific Features 8.3。BRAM IP核包括有5种类型:Single-port RAM 单端口RAM,Simple Dual-port RAM 简单双端口RAM(A写数据B读数据)

2021-03-10 06:15:56 19

19 前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有

2021-03-22 10:31:16 3409

3409 Xilinx_Vivado_zynq7000入门笔记说明。

2021-04-08 11:48:02 70

70 基于VIVADO的PCIE IP的使用 项目简述 上一篇内容我们已经对PCIE协议进行了粗略的讲解。那么不明白具体的PCIE协议,我们就不能在FPGA中使用PCIE来进行高速数据传输了吗?答案是否

2021-08-09 16:22:10 10199

10199

以Xilinx Vivado设计套件中提供的FFT IP为例,简要说明如何进行FFT IP配置和设计。

2022-07-22 10:21:27 1755

1755 在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 1240

1240

电子发烧友网站提供《为EBAZ4205创建Xilinx Vivado板文件.zip》资料免费下载

2023-06-16 11:41:02 1

1 在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-20 14:23:57 622

622

Xilinx平台的Vivado HLS 和 Vitis HLS 使用的 export_ip 命令会无法导出 IP

2023-07-07 14:14:57 338

338

DDS(Direct Digital Frequency Synthesizer) 直接数字频率合成器,本文主要介绍如何调用Xilinx的DDS IP核生成某一频率的Sin和Cos信号。

2023-07-24 11:23:29 1728

1728

Vivado IP核提供了强大的FIFO生成器,可以通过图形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1628

1628

FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

2023-08-29 16:41:49 2605

2605

Vivado是Xilinx公司2012年推出的新一代集成开发环境,它强调系统级的设计思想及以IP为核心的设计理念,突出IP核在数字系统设计中的作用。

2023-09-17 15:37:31 1060

1060

针对系统级封装,如何通过协同设计提升ESD保护能力? 协同设计是一种集成电路设计方法,通过在设计过程中将各功能模块和子系统之间的协同关系考虑在内,可以提升电子系统的整体性能和功效。在针对系统级封装

2023-11-07 10:26:04 217

217 Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317

电子发烧友App

电子发烧友App

评论