Altera推出业界唯一投产的低功耗28 nm Cyclone® V GT FPGA,帮助开发人员降低了PCIe Gen2应用的系统总成本,并全面通过了PCI Express® (PCIe®) 2.0规范的兼容性测试。

2013-03-19 12:37:39 2139

2139 6678的pcie和fpga的pcie TX和RX需要交叉接么?DSP的TX接到FPGA的rx,DSP的RX接到FPGA的TX?

2018-06-21 15:49:12

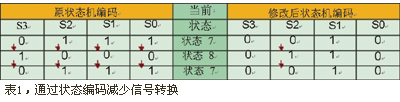

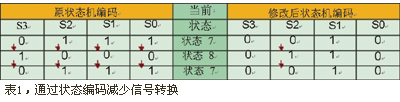

系列子系列介绍表 (1) Artix-7 FPGA系列——业界最低功耗和最低成本 通过表1我们不难得出以下结论: 与上一代 FPGA相比,其功耗降低了50%,成本削减了35%,性能提高30%,占用

2012-09-21 13:46:16

FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能够做到如此低的功耗是因为什么?

2021-04-30 06:08:49

FPGA已经被广泛用于实现大规模的数字电路和系统,随着CMOS工艺发展到深亚微米,芯片的静态功耗已成为关键挑战之一。文章首先对FPGA的结构和静态功耗在FPGA中的分布进行了介绍。接下来提出了晶体管

2020-04-28 08:00:00

是90nm的1.2 V器件,与先前产品相比可降低静态和动态功耗,且FPGA制造商采用不同的设计技术进一步降低了功耗,平衡了成本和性能。这些90nm器件都改变了门和扩散长度,优化了所需晶体管的开关速率

2015-02-09 14:58:01

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-11-05 07:54:43

对于各种不同的数据中心工作负载,FPGA 可以显著提高性能,最大程度减少附加功耗并降低总体拥有成本 (TCO)。

2019-08-13 08:03:44

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-08-29 07:52:29

电源引脚布局减小了22%,功耗降低了35%。图1 2.有效应对噪声敏感输入 因为FPGA中许多模块对供电电源噪声非常敏感,而噪声会导致产生抖动,随之带来很高的误码率(BER),降低了电路性能,而

2018-10-23 16:33:09

目前许多终端市场对可编程逻辑器件设计的低功耗要求越来越苛刻。工程师们在设计如路由器、交换机、基站及存储服务器等通信产品时,需要密度更大、性能更好的FPGA,但满足功耗要求已成为非常紧迫的任务。而在

2019-07-15 08:16:56

。除此之外,设计中采用一些低功耗技巧,也可以降低静态功耗。IGLOO具有功耗友好的器件架构,能提供静态、睡眠、Flash*Freeze功耗模式,允许采用动态电压和频率调节技术来降低系统整体实际功耗。提供可选择

2019-07-05 07:19:19

PCIe设备的低功耗状态要求系统驱动程序显式地将设备置于低功耗状态,从而PCIe链路则可以依次变为低功耗链路状态。PCIe规范允许PCIe链路在没有系统驱动的情况下进入低功耗状态。这个特性就是所谓

2021-12-28 06:18:35

PCIe设备的低功耗状态要求系统驱动程序显式地将设备置于低功耗状态,从而PCIe链路则可以依次变为低功耗链路状态。PCIe规范允许PCIe链路在没有系统驱动的情况下进入低功耗状态。这个特性就是所谓

2022-01-03 08:00:09

设计技巧为什么能够节省功耗?降低FPGA功耗的设计技巧有哪些?

2021-04-30 06:04:19

降低FPGA功耗的设计技术 Design Techniques to Reduce Power Consumption Each generation of FPGAs gets

2009-12-18 16:49:59

”,这个系统大到宇宙空间,小到微观空间个体。在电子领域更可以直接指不同的工作系统,不同的单个器件。简化模型如图1。桥接的目的是什么?是为了两个系统之间产生物理或者电气连接,为了传输特定的媒介。在电子领域

2022-02-20 07:00:00

LT4320IN8-1理想二极管桥控制器的典型应用电路。 LT4320-1是理想的二极管桥控制器,可驱动四个N沟道MOSFET,支持典型的DC至600Hz的电压整流。通过最大化可用电压并降低功耗,理想的二极管桥简化了电源设计并降低了电源成本,特别是在低压应用中

2019-03-29 07:58:55

通过最大化可用的电压和降低功耗(请参阅下面的温度计比较),理想二极管桥简化了电源设计和降低供电成本,尤其是在低电压应用。一个理想二极管桥也消除了热设计问题,昂贵的散热片,并大大降低了印刷电路板面积。

2019-10-23 09:10:25

Virtex 7 PCIe硬IP是否意味着FPGA内部的ASIC?或者像Tandem方法一样,在第一阶段,CPLD将PCIe初始配置加载到FPGA? (http://www.em.avnet.com

2020-05-29 12:52:09

层板设计,专业的PCB Layout保证信号完整性的同时,经过严格的质量控制,满足工业环境应用。SOM-TLK7核心板引出FPGA丰富的资源信号引脚,二次开发极其容易,客户只需要专注上层应用,大大降低了

2020-09-24 14:39:36

项目名称:FPGA PCIe信号拆分应用领域:计算机参赛计划:利用FPGA的并行资源,实现在不使用plx硬核芯片的情况下对PCIe信号的拆分。具体有效带宽视开发板资源而定。使用FPGA相较于使用硬核

2021-05-12 18:05:46

1688Mb/s的DDR3存储器。可以被配置为三态用于降低功耗和高速IO操作。除了供电引脚和一些专用的配置引脚,每个BANK里的IO有相同的IO能力。7系列的FPGA,其IO可以分为宽电压IO标准和高性能两种

2016-11-01 15:52:18

。上次介绍了该开发板所采用的PCIE传输框架RIFF,今天进一步分析其ARM端的测试例程pcie2screen并介绍一下FPGA端程序的修改。一、测试例程pcie2screen例程pcie

2023-02-13 17:57:47

了DMA 读写功能的模块,而且 RIFFA 模块提供了TX 和 RX 读写接口,因此用可以直接操作 RIFFA 的读写接口,从而来控制 PCIE 模块的读写,有了 RIFFA 模块大大降低了 FPGA

2023-01-30 14:14:25

无论从微观到宏观、从延长电池寿命到减少全球变暖的温室效应等等,各种不同因素都在迅速推动系统设计人员关注节能问题。一项有关设计优先考虑事项的最新调查指出,大部分工程师已把功耗排在首位,或者是将其紧跟在性能、密度和成本之后。在功耗方面,FPGA带来了独特的挑战。为什么要设计优化FPGA功耗?

2019-08-08 07:39:45

客户关注的问题。降低FPGA功耗是降低封装和散热成本、提高器件可靠性以及打开移动电子设备等新兴市场之门的关键。

2019-09-20 06:33:32

基于V7的高性能PCIe信号处理板是什么?基于V7的高性能PCIe信号处理板有哪些主要功能?基于V7的高性能PCIe信号处理板有哪些应用?

2021-06-25 06:21:15

进行原型开发,把设计移植到低风险、低成本HardCopy V ASIC,性能将大大提高,功耗能够降低50%。Stratix V FPGA具有以下优点: (1)高功效收发器突破了带宽 a.集成

2012-09-21 13:49:05

案例中,这样的平台需要进行一定的调整以满足汽车制造商的需求。而使用FPGA可以快速实现低成本桥接解决方案,使得现有平台能够完美应用于汽车领域。

2019-07-23 07:57:39

总谐波失真 (THD) 低于一定百分比,而且还需要每个谐波都不超过 IEC 61000-3-2 合规性标准中规定的特定限值。在这篇共分两部分的博客中,我将介绍用于降低 PFC 谐波和改善 THD

2018-09-12 09:47:28

最新器件 Virtex-4 FPGA 提供了 90 nm 工艺技术的高性能,却避免了预想中静态功耗的显著增大。使用赛灵思功耗估算工具并遵循低功耗设计考虑事项,满足您的功耗目标将比以往任何时候都更加容易。

2012-01-11 11:59:44

有着严格的浪涌电流和稳态工作电流限值要求,因此由总线供电的器件应用经常忽视FPGA,而是更愿意采用性能和灵活性都不及 FPGA 的微控制器解决方案。随着赛灵思低功耗系列器件中最新成员Artix-7

2016-07-27 17:14:50

事件被捕获使用硬件UART克服软件实现的性能限制LCMXO2-640HC-4TG100C可编程逻辑器件FPGA芯片通过硬件性能加速提升系统性能基于逻辑的信号过滤降低了处理器负荷以最小的处理器开销实现

2019-09-20 15:13:30

处理器的设计正在从提高频率向降低功耗的方向转变,为满足更高性能的要求并使功耗不超过许多应用所能承受的范围,微处理器的一个明显变化是从频率越来越高向多内核架构转变。

2019-11-08 06:21:20

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-08-15 08:28:42

如何降低可重构系统的整体功耗?有什么方法能使可重构系统的性能和功耗需求之间达到平衡?

2021-04-08 07:09:23

现在需要一反向耐压值为600V,电流为3A的整流桥作为开关电源的整流器,但是,这个高压整流桥的压降大,这样引起的功耗就大,由于对开关电源的效率有要求,请问有什么办法可以降低整流桥的功耗吗?或者,有低压降的高压整流桥推荐吗?

2014-05-13 19:53:40

/latest_fpgas_show_big_gains_in_floating_point_performance/我对SP Add的Virtex 7 - 690T的计算如下:1-将频率降低15% - 对于

2020-08-13 09:56:00

嗨,我能够在我们的定制板上连接到virtex 7 fpga。我的块级设计具有用于pcie的轴桥作为终点和axi bram。但我无法使用pcie链接从外部处理器访问bram。任何人都可以帮忙解决这个问题吗?大多数情况下,我猜这与地址翻译有关,我无法弄清楚。谢谢

2020-04-22 09:31:47

嗨,我正在使用AXI-PCIe桥接IP与我的逻辑进行通信。我的poroject要求有128K内存。我不知道如何配置AXI BAR地址来扩展内存。我阅读了IP文档,但没有任何意义。目前我能够从具有32K PCIe BAR空间的PC读写。

2020-06-19 10:14:32

针对互连功能以及高性能和低功耗进行了优化。ECP5 FPGA系列提供业界最小尺寸封装(10x10 mm),并具备高达85K查找表(LUT),功能密度相比竞品高出近2倍,同时成本和功耗也大幅降低

2020-10-21 11:53:02

从工艺选择到设计直至投产,设计人员关注的重点是以尽可能低的功耗获得最佳性能。Altera在功耗和性能上的不断创新,那其28nm高端FPGA如何实现功耗和性能的平衡?具体有何优势?

2019-09-17 08:18:19

如何利用FPGA实现低成本汽车多总线桥接?

2021-04-29 06:51:23

复杂器件专业技术相结合,将为系统供应商提供低功耗的芯片方案,供他们在此基础上持续提高带宽容量,并完成更智能的处理。此外,TPACK提供的芯片解决方案可以导入到最新的FPGA中,进一步降低功耗。最终实现

2019-07-31 07:13:26

对于各种不同的数据中心工作负载,FPGA 可以显著提高性能,最大程度减少附加功耗并降低总体拥有成本 (TCO)。

2019-10-10 07:46:05

如何才能实现降低FPGA设计的功耗?

2021-04-29 06:47:38

相关的影响和设计问题,并介绍一些可行的解决方案和应用方法。桥接新旧视频接口人们对创新的低成本视频桥接解决方案的需求正与日俱增。 例如,构建监控系统、无人机或 DSLR 摄像头的设计人员想要利用上热门移动

2017-04-06 13:48:17

我的项目是为安全关键应用开发基于VMEbus的LCD模块。我只会使用VMEbus的连接器P1到背板。要使用的模块是:人机界面(LCD模块)数据输入(例如,通过键)数据输出(LED)地址选择逻辑 16

2019-05-23 08:52:42

嗨,我正在使用超大规模的FPGA板。我可以通过DMA子系统IP和DDR控制器IP将数据从PC传输到DDR。我打算在FPGA中进行一些处理,然后更新数据,以便PC可以读取。如何通过PCIe指示PC处理

2020-05-08 09:40:04

,允许采用动态电压和频率调节技术来降低系统整体实际功耗。提供可选择的1.2V和1.5V的I/O和核电压,以方便用户平衡设计的性能和功耗之间的关系。IGLOO的时钟结构可以没有副作用的对全局信号和局部信号进行门控制。另外IGLOO的RAM模块具有LP和F*F端口来控制RAM本身的静态功耗。

2020-05-13 08:00:00

我有一个问题,我必须在使用JTAG将位文件下载到FPGA后重新启动计算机。否则,我无法使用PCIE读取寄存器或与PCIE接口有关的任何内容。我该怎么做才能改善我的情况?谢谢。

2020-06-02 15:56:26

。电池通过PIC用来sh的PMOSfet直接连接到GSM模块。关闭GSM模块并降低功耗。我与LDO有一些问题,只提供PIC和一些上拉,当GSM模块注册或发送GPRS分组时,我每4mS获得大约500S

2019-09-19 14:05:22

究竟怎样才算低功耗?小于5mA?小于1ms?小于100uA?怎样通过软件控制的方式来优化并降低单片机的功耗?低功耗的范围大概在哪?

2021-07-08 06:25:55

脉宽调制器 (DPWM)、低功耗微控制器等。它们是如无桥接 PFC 等复杂高性能电源设计的较好选择。数字控制无桥接 PFC在其他一些无桥接 PFC 拓扑结构中[1] [2],图 1 是一个已经为业界所广泛

2018-09-26 10:52:03

的功耗取决于FPGA芯片及硬件设计本身,很难有较大的改善。可以优化是第3部分功耗:设计动态功耗,而且这部分功耗占总功耗的90%左右,因此所以降低设计动态功耗是降低整个系统功耗的关键因素。上面也提到过功耗

2014-08-21 15:31:23

的视频放大器只需要2V/V增益(图9),从而降低了对最后一级视频放大器的要求,并降低功耗。同时也降低了两个放大器的总功耗,实现最佳性能。

2020-12-17 09:52:10

嗨,我将从一个新项目开始。它涉及使用FPGA和GP / GPU加速PCIe板,这些板将被添加到常规计算机或服务器中。 GPU将是NVIDIA特斯拉。 FPGA板......还有待选择。我确实看到了

2019-01-24 10:55:48

如何利用FPGA设计技术降低功耗?

2021-04-13 06:16:21

本帖最后由 一只耳朵怪 于 2018-6-25 11:01 编辑

你好!我目前正在实现6657DSP 评估板与xilinx kintex7 FPGA之间的PCIE连接,其中DSP作为Root

2018-06-25 05:14:40

成本 通过表1我们不难得出以下结论: 与上一代 FPGA相比,其功耗降低了50%,成本削减了35%,性能提高30%,占用面积缩减了50%,赛灵思FPGA芯片在升级中,功耗和性能平衡得非常好。 (2

2012-09-06 16:24:35

PCI Express是一种高性能互连协议,被广泛应用于网络适配、图形加速器、网络存储、大数据传输以及嵌入式系统等领域。文中介绍了PCIe的体系结构,以及利用Altera Cyclone IV GX

2019-05-21 09:12:26

ARM处理器),释放宝贵的可编程逻辑资源,用于实现其他逻辑功能,从而提高了性能,降低了功耗和成本。作为一个例子,PCI Express(PCIe)协议堆栈需要大约150K LE作为软核实现,在硬核模块中则

2015-02-09 15:02:06

描述 Kintex®-7 FPGA 为您的设计在 28nm 节点实现最佳成本/性能/功耗平衡,同时提供高 DSP 率、高性价比封装,并支持 PCIe® Gen3 和 10 Gigabit

2023-11-10 14:22:14

新一代 FPGA的速度变得越来越快,密度变得越来越高,逻辑资源也越来越多。那么如何才能确保功耗不随这些一起增加呢?很多设计抉择可以影响系统的功耗,这些抉择包括从显见的

2009-06-20 10:37:12 2321

2321

本白皮书介绍了有关赛灵思 28 nm 7 系列 FPGA 功耗的几个方面,其中包括台积电 28nm高介电层金属闸 (HKMG) 高性能低功耗(28nm HPL 或 28 HPL)工艺的选择。 本白皮书还介绍了 28 HPL 工艺提供

2012-03-07 14:43:44 41

41 白皮书 :采用低成本FPGA实现高效的低功耗PCIe接口 了解一个基于DDR3存储器控制器的真实PCI Express (PCIe) Gen1x4参考设计演示高效的Cyclone V FPGA怎样降低系统总成本,同时实现性能和功耗

2013-02-26 10:04:25 72

72 商汤科技算法平台团队和北京大学高能效实验室联合提出一种基于 FPGA 的快速Winograd算法,可以大幅降低算法复杂度,改善 FPGA 上的 CNN 性能。

2018-02-07 11:52:06 8687

8687

赛灵思7系列FPGA产品通过采用新的工艺和新的架构方式,成功将产品的功耗显著降低。7系列FPGA产品的实测功耗与上一代产品相比,降低了约一半。采用台积电全新28HPL工艺,赛灵思7系列28nm FPGA产品同时实现了高性能和低功耗。

2018-06-05 13:45:00 4086

4086 查看UltraScale FPGA中集成的PCIe Gen3模块的性能演示。

第一个演示显示了PCIe链路上的最大数据吞吐量;

demo#2利用现成的DMA引擎和软件驱动程序来代表典型的用例。

2018-11-28 06:22:00 3464

3464 与传统FPGA架构相比,UltraScale架构引入了许多创新,可提高性能并降低功耗。

在本视频中,我们将重点介绍路由,逻辑和实现软件的增强功能......

2018-11-22 06:45:00 3056

3056 reconfigure.io的Rob Taylor在法兰克福的XDF 2018云轨道中展示了一个用例。

Rob讨论了FPGA在FPGA中的可访问性,降低了评估和利用FPGA的成本。

2018-11-22 06:08:00 3402

3402 高线性度下变频混频器使 3G 和 4G 无线基站的性能提高并降低了功耗

2021-03-21 10:18:10 3

3 本文介绍一个FPGA 开源项目:PCIE I/O控制卡。上一篇文章《FPGA优质开源项目– PCIE通信》开源了基于FPGA的PCIE通信Vivado工程,用于实现上位机通过PCIE接口访问FPGA的DDR3以及RAM内存数据。PCIE I/O控制卡工程是在上一个工程的基础上进行了部分模块和参数的修改。

2023-09-01 16:18:36 1296

1296

V不仅对之前Arora家族进行了补充,还在降低功耗的同时显著提升了性能。与Arora家族GW2A系列相比,Arora V器件的性能提高了30%,功耗降低了60%。Arora V编程配置为设计人员提供

2023-11-02 09:45:04 638

638 性能提升,功耗降低!,这样的MOSFET是你的最爱么?

2023-12-04 15:09:36 114

114

电子发烧友App

电子发烧友App

评论