两大主流厂商的软件集成逻辑分析仪供使用,Altera的Quartus自带SignalTap、Xilinx的Vivado自带ILA逻辑调试工具。

2023-10-01 17:08:00 1456

1456

ILA Cross Triggering功能使得ILA核心之间、以及ILA核心与处理器(例如,AMD Zynq 7000 SoC)之间可以进行Cross Trigger。这个功能在你需要在不同时钟域的两个ILA核心之间触发,或者在处理器和ILA核心之间执行硬件/软件跨触发时非常有用。

2023-11-30 10:17:59 506

506

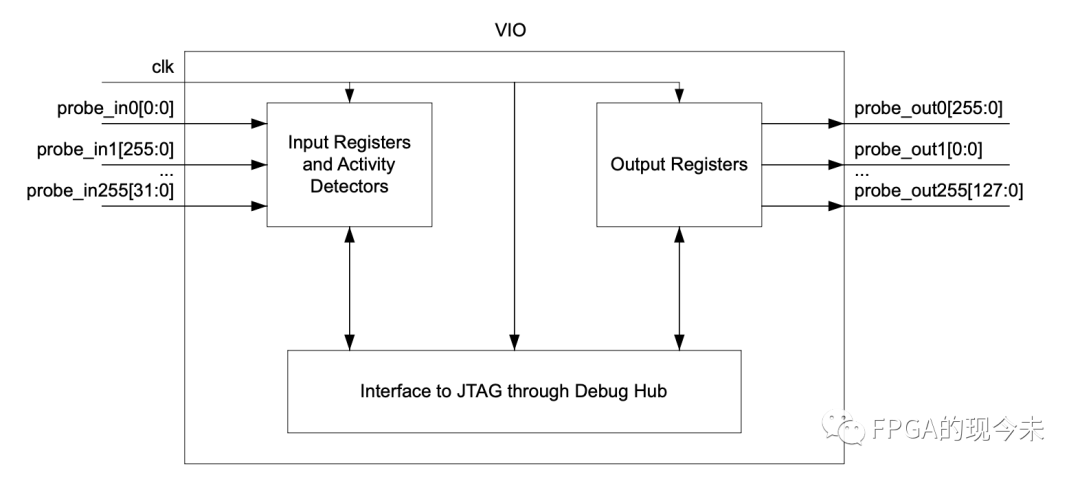

在以往的项目中,要控制FPGA内部某个信号的值,往往是通过配置寄存器来实现的。其实Xilinx还提供了一个叫VIO的core,可以动态改变FPGA内部某个信号的值,但是一直没有用过,一来对于以前的项目来说,没有应用场景,通过寄存器就可以配置了;二来感觉这个东西不是很“实用”。

2023-12-11 18:26:52 697

697

我确实遇到了一个我想解决的问题。这更像是Vivado的实现问题。我正在尝试使用ILA内核和探针将调试内核添加到我的设计中。执行设计后,我收到以下错误:[Chipscope 16-119]实现调试核心

2019-01-03 11:00:14

HI,Chipscope中的ILA,VIO和ATC2有什么区别?问候Naveen G K.谢谢娜文G K.

2020-03-31 10:09:34

嗨,我有spartan 3a评估套件,我试图将Chipscope ILA添加到我的设计中但是我在实现的设计部分中收到了错误。错误:NgdBuild:1317- 使用核心芯片eye_ila_v1需要

2018-12-12 10:47:57

你好, 我正在使用Aurora 8B / 10B v5.3 IP内核,Virtex 5 FPGA用于使用SFP电缆的GB收发器。我使用核心生成器创建了IP核,获得了示例设计(所有文件)。我模拟了示例

2020-04-07 14:52:25

本人菜鸟一枚,请问FPGA中(使用verilog)ChipScope显示输入时钟信号(clk50M),报错误,如果通过pll获取其他频率比如clk40M,为什么ChipScope显示的时钟频率一直为

2017-05-09 20:31:19

的情况时,总会遇到一些以前未曾接触过的新内容,这些新内容会让我们感到陌生和恐惧,不知道该如何下手。

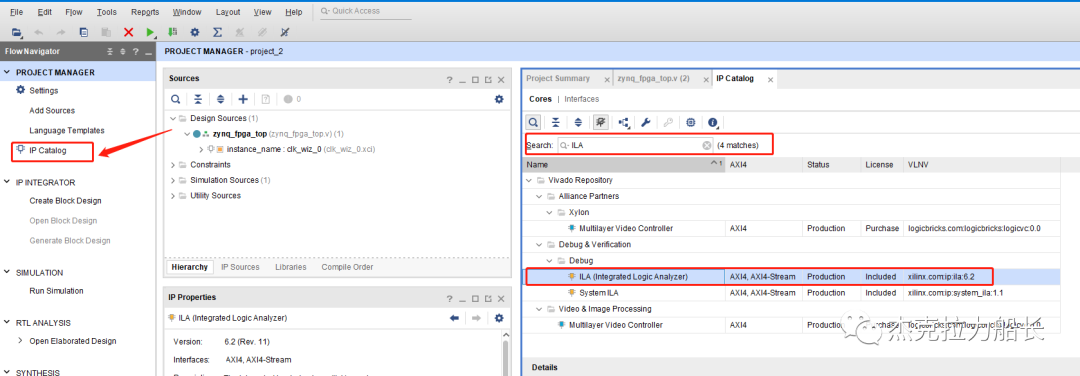

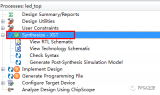

那么今天以xilinx vivado 为例分享学习FPGA 新IP核的正确打开方式。

一、常规

2023-11-17 11:09:22

提供的软核,通过Xilinx开发环境和jtag下载线可以在PC上获知FPGA内部逻辑信号的状态,也能输出信号给FPGA内部逻辑。TCL是一种通用的EDA工具脚本语言。Xilinx开发环境提供了一个很

2012-03-08 15:29:11

网上能找到的资料都是用altera的FPGA做的,有人用过xilinx FPGA搭建8051核吗?请与我联系

2017-06-03 14:59:23

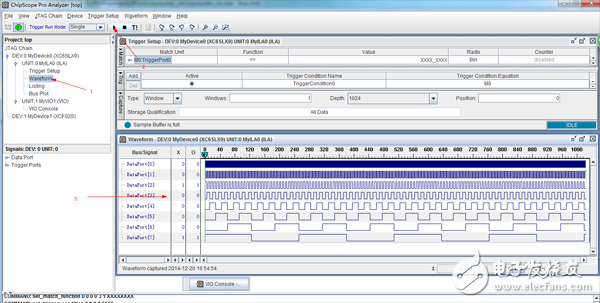

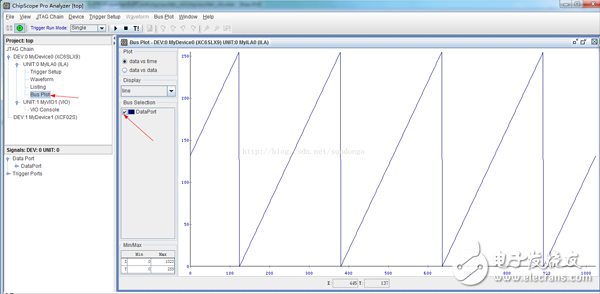

`Xilinx FPGA入门连载27:基于Chipscope的超声波测距调试之功能简介特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

2015-11-23 11:24:49

`Xilinx FPGA入门连载28:基于Chipscope的超声波测距调试之Chipscope配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s

2015-11-25 13:45:30

`Xilinx FPGA入门连载29:基于Chipscope的超声波测距调试之板级调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

2015-11-29 19:01:50

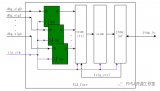

`Xilinx FPGA入门连载40:SRAM读写测试之设计概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能简介如图所示,本

2015-12-18 12:57:01

`Xilinx FPGA入门连载40:SRAM读写测试之Chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

2015-12-25 15:04:32

Xilinx FPGA入门连载43:FPGA片内ROM实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述该工程

2016-01-06 12:22:53

`Xilinx FPGA入门连载46:FPGA片内ROM实例之chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm

2016-01-18 12:30:14

实例内部系统功能框图如图所示。我们通过IP核例化一个RAM,定时遍历写入其所有地址的数据,然后再遍历读出所有地址的数据。通过ISE集成的在线逻辑分析仪chipscope,我们可以观察FPGA片内RAM

2016-01-20 12:28:28

Xilinx FPGA入门连载50:FPGA片内RAM实例之chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

2016-01-27 13:10:35

实例内部系统功能框图如图所示。我们通过IP核例化一个FIFO,定时写入数据,然后再读出所有数据。通过ISE集成的在线逻辑分析仪chipscope,我们可以观察FPGA片内FIFO的读写时序。 2 模块

2016-02-26 10:26:05

`Xilinx FPGA入门连载54:FPGA 片内FIFO实例之chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s

2016-03-04 13:13:12

`Xilinx FPGA入门连载55:FPGA 片内异步FIFO实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

`Xilinx FPGA入门连载58:FPGA 片内异步FIFO实例之chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s

2016-03-16 12:13:05

`Xilinx FPGA入门连载59:FPGA 片内ROM FIFO RAM联合实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s

2016-03-16 12:43:36

`Xilinx FPGA入门连载61:FPGA 片内ROM FIFO RAM联合实例之chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com

2016-03-21 12:19:39

入门指南 -- 数码管驱动实例Lesson29 特权Xilinx FPGA SF-SP6入门指南 -- 基于Chipscope的超声波测距之功能简介Lesson30 特权Xilinx FPGA

2015-07-22 11:49:20

'ila_pro_0'.XST失败。错误:Xst:错误:sim:877 - 在执行IP'ILA期间发现错误(ChipScope Pro - 请参阅CoreGen日志/*/par1/results

2020-05-04 12:09:30

`Xilinx系列FPGA芯片IP核详解(完整高清书签版)`

2017-06-06 13:15:16

将设计上传到FPGA中。但是当我尝试使用chipScope Pro进行分析时,它会返回一条警告,表示没有连接Xilinx平台的USB电缆。我使用的是Windows 10。请告诉我们可以做些什么。问候

2019-04-18 12:38:46

。:ERROR:sim- 无法生成'icon_pro'。生成期间发现错误。:ERROR:sim:877- 执行IP'ICON时发现错误(ChipScope Pro -See CoreGen Log F

2018-12-12 10:41:37

问题描述:我要通过spi获取ADC ROM中的内容。在综合后进行仿真,其结果和想要的结果一致,如图1所示。然后加入chipscope进行数据的抓取,但出现如下图的结果。其中FPGA的输入

2018-06-04 10:34:29

请问大家,在一个ICON下做了两个ila,使用的是不同的时钟域。请问该如何设置同时触发呢?非常感谢!

2013-11-25 08:57:07

有没有大神可以提供xilinx FPGA的FFT IP核的调用的verilog 的参考程序,最近在学习FFT的IP核的使用,但是仿真结果有问题,所以想找些参考设计,谢谢

2016-12-25 17:05:38

xilinx的Chipscope的使用方法

2018-01-12 15:28:25

大家好,我在使用Arty(Artix 7 FPGA)进行调试时遇到了一些麻烦。背景:我使用ILA在Zybo(Zynq)和Nexys 4 DDR(也是Artix 7)上调试我的程序,一切正常。我

2020-08-26 15:20:18

Xilinx FPGAs ChipScope™ Pro System Analyzer

2023-03-30 12:03:54

Xilinx FPGAs ChipScope™ Pro System Analyzer

2023-03-30 12:03:54

嗨, 我试图使用Chipscope Pro来调试我的FPGA(Spartan 6:SP605)实现。我想在顶层模块放置一个ILA和一个VIO核心,在子级别模块放置一个ILA和一个VIO

2020-03-18 10:21:46

“srio_v5_6.xise”。我合成了项目并实现了它,但是在实现项目时发生了错误如下:错误:NgdBuild:604- 无法解析类型为'srio_icon'的逻辑块

2018-10-08 11:10:47

在使用vivadao在线调试功能时,对需要抓的信号MARK DEBUG,调用了ILA测试核,添加了时钟约束,但是总是显示no nets matched的warning,最后烧到片子里界面没有跳转到在线调试界面,无信号,显示没有添加ILA,问题出在哪里呢?求大神解答

2015-06-08 11:19:27

使用Fclk_clk0,ARM PLL,与我所有的PL逻辑绑定现在,我把AXI_monitor& XPS中的ICON(3个控制端口),并实例化一个附加的ILA&包装器中的VIO(连接到ICON)我生成一个位文件,使用分析配置,但似乎时钟没有运行。

2019-09-05 06:03:46

` 本帖最后由 eehome 于 2013-1-5 10:07 编辑

Xilinx FPGA开发实用教程第1章 FPGA开发简介1.1 可编程逻辑器件基础1.1.1 可编程逻辑器件概述1.1.2

2012-04-24 09:23:33

请问大家,在一个ICON下做了两个ila,使用的是不同的时钟域。请问该如何同时触发呢?非常感谢!

2013-11-25 08:49:34

你好这是我第一次尝试添加ILA来调试loigc。在Vivado我添加了ILA IP核 ila_0 ila_0_INST( .clk(sys_clk),//输入线clk.probe0

2019-10-10 05:57:42

thoughts? I appreciate this. ERROR:NgdBuild:1317 - Using core chipscope_ila_v1 requires a ChipScopePro

2018-11-28 15:12:01

'chipscope_vio'.ERROR:NgdBuild:604 - 无法解析类型为'chipscope_icon'的逻辑块'icon_1'。引脚名称拼写错误可能导致此问题,缺少edif或ngc文件,块名称

2019-08-02 08:10:22

/pcie3_7x_0_example.runs/impl_1/debug_nets.ltx不匹配。设备设计有0个ILA核心和0 VIO核心。 probe文件有1个ILA内核和0个VIO内核。分辨率:确保设备探测文件是最新的,然后重新编程设备。我不知道为什么会发生,请给我一些想法!谢谢FIRO

2020-07-27 14:28:58

project, launched ChipScope 64 bit Core Inserter and added ILA & ICON cores. After that I added to my

2018-12-11 11:15:26

嗨,可以在Chipscope中看到FPGA外部引脚......?问候Naveen G K.谢谢娜文G K.

2020-03-31 09:55:44

在Xilinx FPGA上使用Cortex M1 软核——Keil中使用J-Link调试Cortex-M1嵌入式工程本文的软件代码部分参考自ARM提供的例程。

2021-12-15 08:36:50

我是7系列FPGA的新手。最近开始使用Xilinx VC707板。在此之前,我曾经在Virtex 5上工作。我有一个ISE项目,使用Xilinx ISE和Chipscope使用Vitex 5板进行

2020-07-28 10:18:04

“CHIPSCOPE_INST.u_ddr_ila_basic”。引脚名称拼写错误可能导致此问题,缺少edif或ngc文件,块名称与edif或ngc文件名之间的大小写不匹配,或者类型名称的拼写错误。目标'virtex7'不支持符号'ddr_ila_basic'。谢谢。

2020-07-15 10:50:11

ChipScope Analyzer中尝试使用opena插件时,我收到了这些消息。命令:open_target xilinx_tcf url = tcp:信息:启动ChipScope主机

2019-11-08 15:21:30

亲爱的论坛,我们面临着Xilinx Kinetix-7 FPGA非常奇怪的行为。所以问题如下:我们合成了RTL并将其加载到FPGA中。当我们打开bord时,FPGA工作正常!几分钟后(约5-7分钟

2019-11-07 09:38:56

[Chipscope 16-119]实现调试核心u_ila_0 failed.ERROR:无法为u_ila_0生成核心。中止IP生成操作。错误:[Chipscope 16-218]尝试从IP缓存

2018-10-26 15:10:15

本帖最后由 神奇艾尔斯 于 2019-10-28 10:50 编辑

如题,我想写一个计数器,我设置一个值开始加,加到1000停止;count在always块里,是reg型,好像无法连到vio上

2019-10-28 09:57:38

嗨,由于未连接的Chipscope信号,我在PlanAhead 14.7中收到以下错误:错误:[Chipscope 16-30]调试端口'cs_ila_0 / DATA'上有5个未连接的通道。这可

2018-10-19 14:36:55

% of the luts.Vivado has no problem without Chipscope. When I add an ILA with 38 probes and 4k sample

2018-10-30 11:16:13

` 1概述本实例(zstar_ex55)在zstar_ex54的基础上,增加VirtualIO(VIO)实现在线板级调试的功能,意图让大家学会VIO这种基于FPGA的简单实用的在线板级调试手段。2

2019-11-21 10:04:31

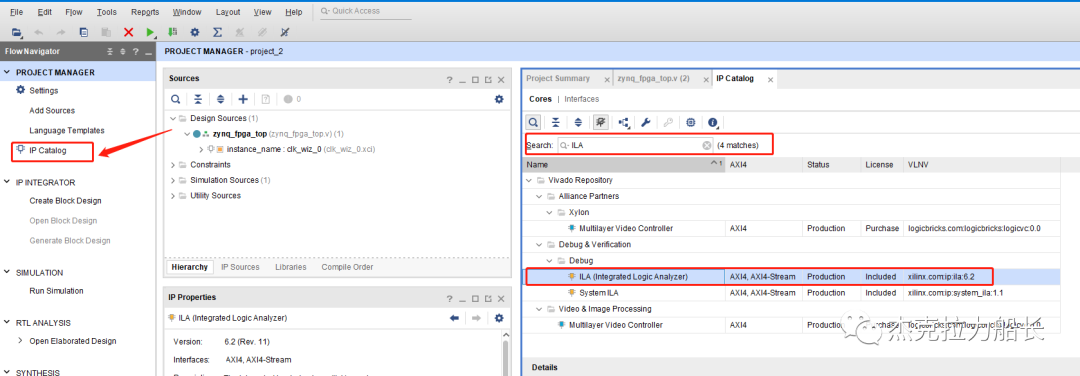

的Vivado上可以查看最终采集的波形。并且ILA不需要被测试信号有实际的物理探测点,只要这个信号是在FPGA内部,就可以被实时的观测到。ILA功能模块可以通过配置IP核方式例化到RTL代码中,也可以在

2019-05-24 15:16:32

新手请教:virtex5中有4条boundary scan chain(USER1,USER2,USER3,USER4),创建chipscope ICON时只能使用一条chain。那么做了4条为什么只能用一条,4条chain有什么区别? 若是我的理解有问题,请大牛指点,非常感谢!

2014-02-13 09:21:58

FPGA调试工具chipscope,学习与使用FPGA必用的工具。。

2009-03-23 09:45:00 86

86 实用FPGA的调试工具—ChipScope Pro

ChipScope Pro应用于FPGA调试阶段,它具有传统逻辑分析仪的功能,可以观察FPGA内部的任何信号,触发条件,数据宽度和深度等的设

2010-02-09 15:10:46 95

95 什么是D-ILA投影技术

D-ILA(Direct-Drive Image Light Amplifier,直接驱动图像光源放大器)技术。D-ILA技术在提供高分辨率和高对比度方面显示了技术优势,

2010-02-05 10:42:23 636

636 本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、Verilog HDL开发基础与进阶、Xilinx FPGA电路原理与系统设计

2012-07-31 16:20:42 11268

11268

chipscope是一款在线逻辑分析仪,可实时有效的检查FPGA内部设计电路各需求中间节点的信号波形。

2015-11-23 11:36:24 2

2 Xilinx FPGA系列入门教程(一)——如何搭建Xilinx FPGA开发环境

2016-01-18 15:30:32 45

45 Xilinx chipscope使用方法,针对刚刚开始接触FPGA的同学,零基础学习。

2016-03-21 16:57:04 1

1 Xilinx FPGA工程例子源码:ChipScope使用示例

2016-06-07 14:13:43 7

7 华清远见FPGA代码-ChipScope功能演示

2016-10-27 18:07:54 4

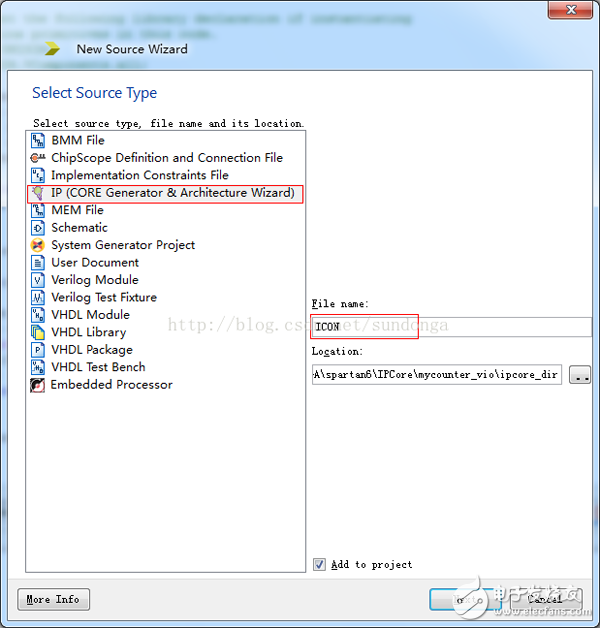

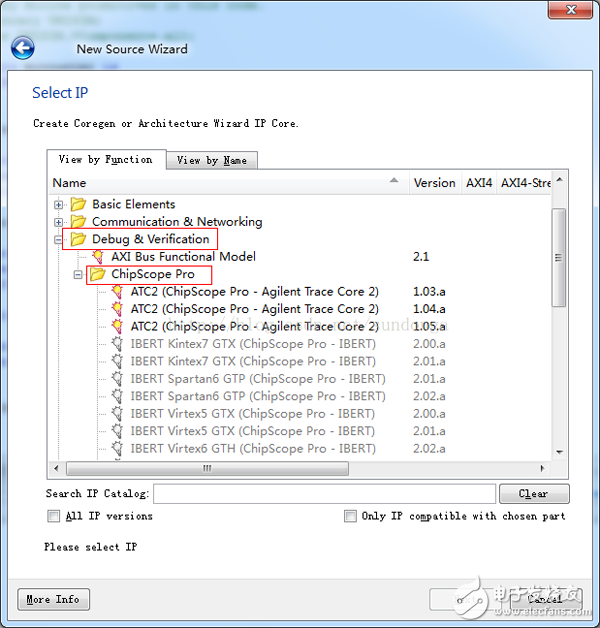

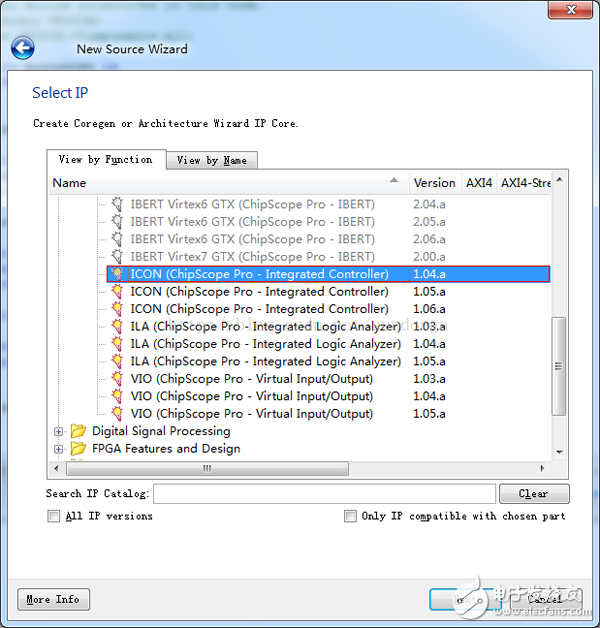

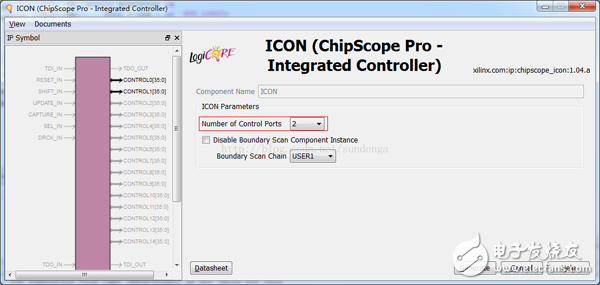

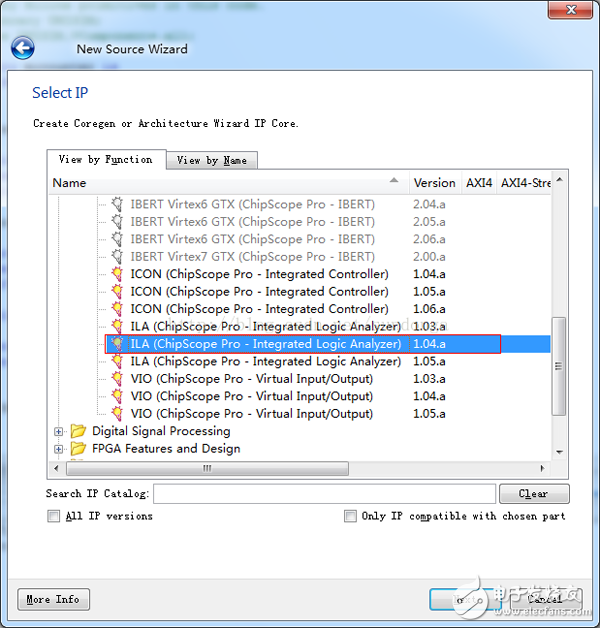

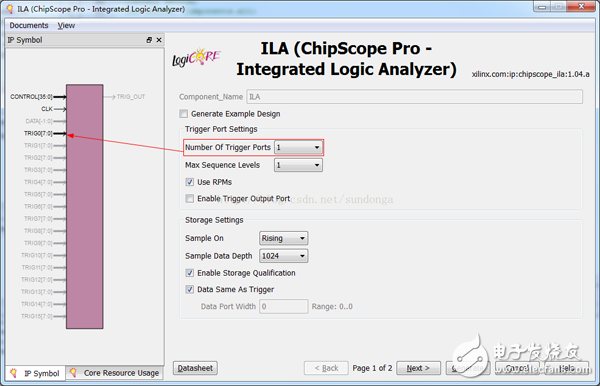

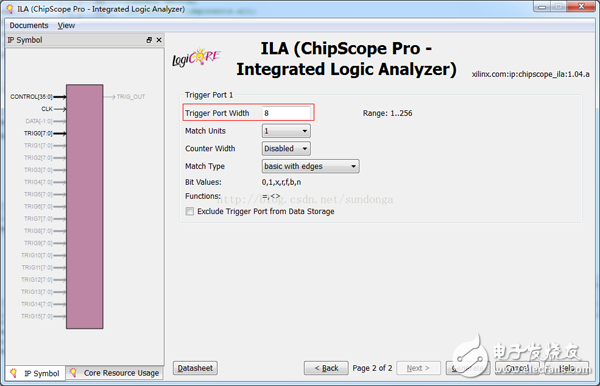

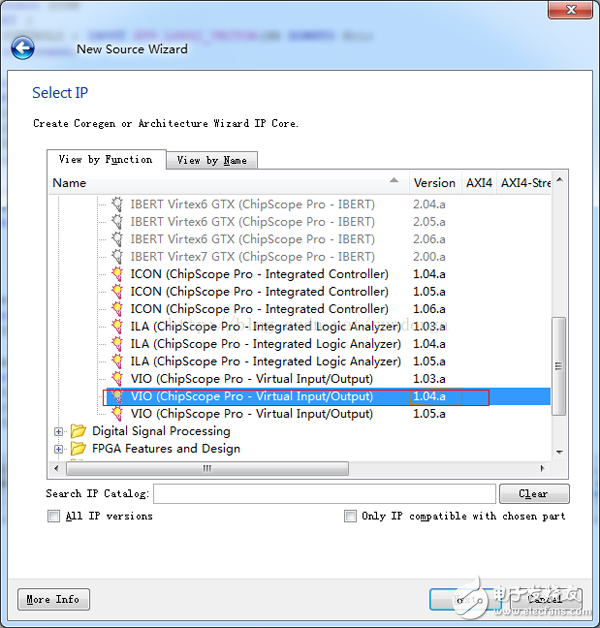

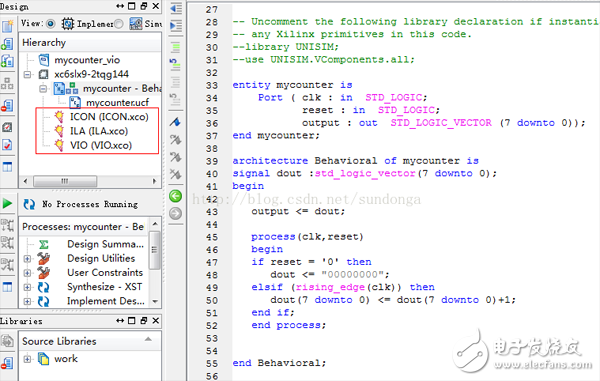

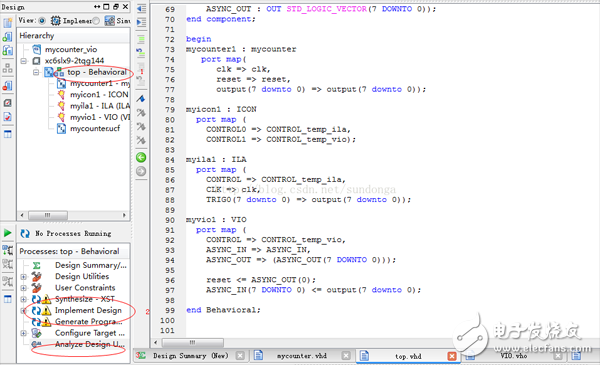

4 Xilinx针对不同类型的调试IP核,提供了不同的核生成器。本节重点介绍Xilinx Core Generator Tool(Xilinx IP核生成器)所支持的ChipScope Pro调试IP核ICON、ILA、VIO和ATC2及其属性

2017-02-11 07:14:11 761

761

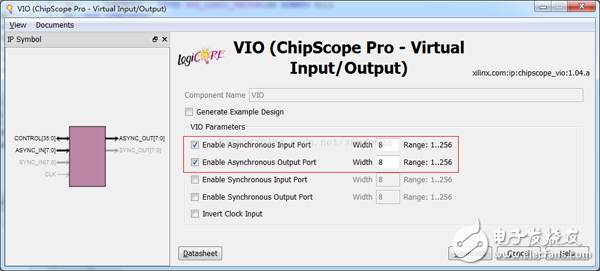

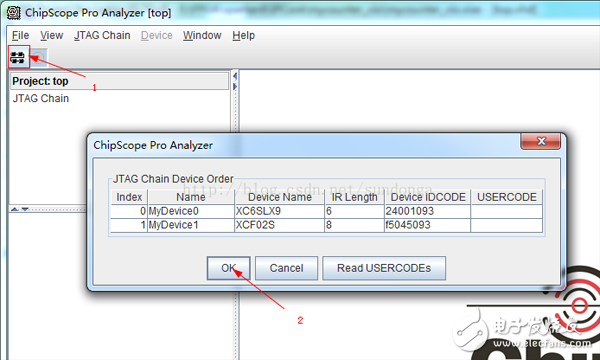

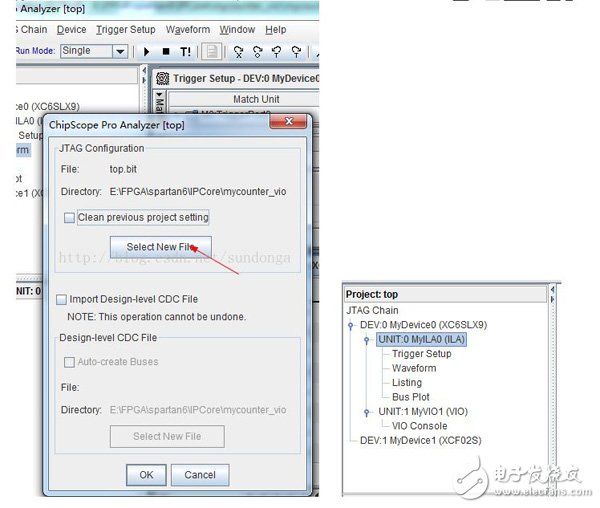

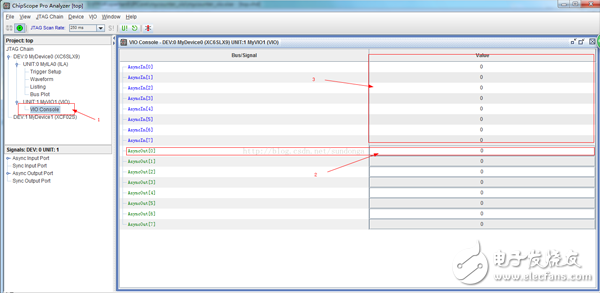

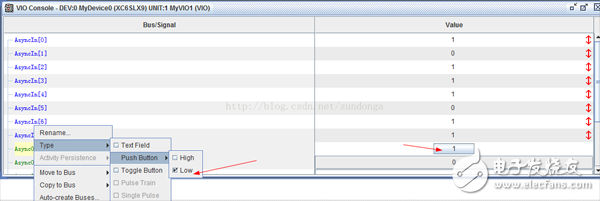

下面通过一个简单8位计数器的例子,了解如何在工程中添加ChipScope Pro内核生成器的各个IP核,对FPGA内部节点和逻辑进行观测。在该实例中,我们将调用一个ICON、一个ILA和一个VIO。

2017-02-11 07:19:40 766

766

ChipScope Pro 分析工具(Analyzer tool)直接与ICON、ILA、IBA、VIO及IBERT核相连,用户可以实时地创建或修改触发条件。

2017-02-11 07:25:00 1486

1486

Xilinx FPGA的Maxim参考设计

2017-10-31 09:59:24 23

23 本文档内容介绍了基于chipscope使用教程以及FPGA在线调试的方法,供参考

2018-03-02 14:09:49 9

9 其实这儿便很简单了,可以直接在画布上添加一个ILA核,再把想要的信号线连进来就行了呀,都不需要在代码里定义这个ILA核。不过这样做就说明你还没能灵活的使用Xilinx的在线调试工具了,因为还有更简单的办法哈哈。

2018-11-14 10:47:56 6509

6509

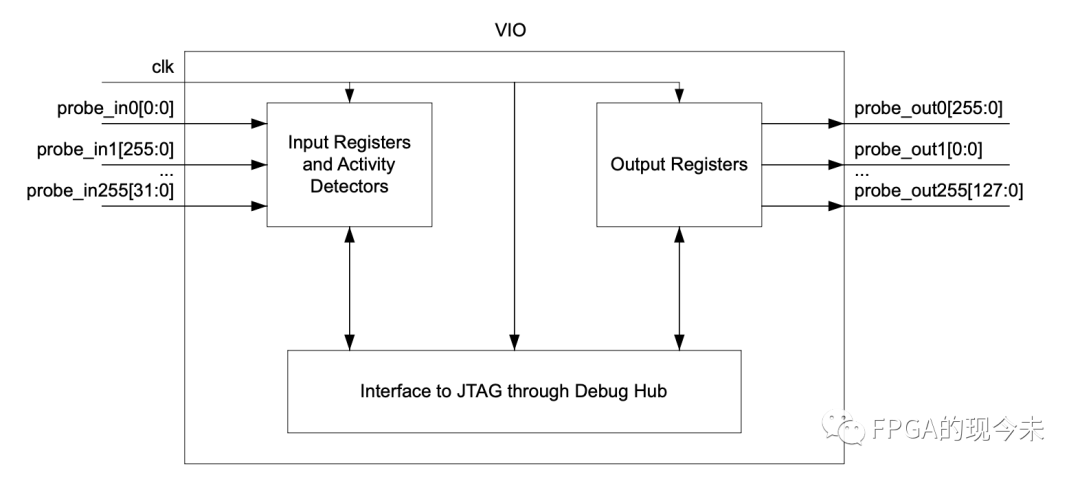

debug,尤其是通信芯片的debug,可以有很多的方法。一个数据帧从进入到输出,可以在通路上的关键节点处设置监测如各种计数器等,可通过VIO(xilinx)定时上报实时状态。可以把VIO的各个

2019-07-19 10:19:15 6570

6570

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

2022-02-08 11:35:19 22057

22057

不一致,从而出现Bug。一种debug的方式就是用FPGA工具提供的ILA模块(xilixn在ISE中叫:chipscope),来实时抓取FPGA内部数字信号的波形,分析逻辑错误的原因,帮助debug。 ILA

2021-08-09 14:12:05 15208

15208

虚拟输入输出(Virtual Input Output,VIO)核是一个可定制的IP核,它可用于实时监视和驱动内部FPGA的信号,如图所示。 可以定制VIO的输入和输出端口的数量与宽度,用于

2021-09-23 16:11:23 6841

6841

一般情况下ILA和VIO都是用在chipscope上使用,VIO可以作为在chipscope时模拟IO。

2022-06-12 15:51:54 1682

1682 Xilinx LabTools工具是Xilinx FPGA单独的编程和调试工具,是从ISE或Vivado中独立出来的实验室工具,只能用来下载FPGA程序和进行ILA调试,支持所有的FPGA系列,无需

2023-03-28 10:46:56 4755

4755 ChipScope是Xilinx提供的一个校验FPGA设计的工具。它的本质是一个虚拟的逻辑分析仪,能调用FPGA内部的逻辑资源对代码中的各个变量进行抓取分析。

2023-05-08 16:55:20 3792

3792

Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

0

正在加载...

电子发烧友App

电子发烧友App

评论