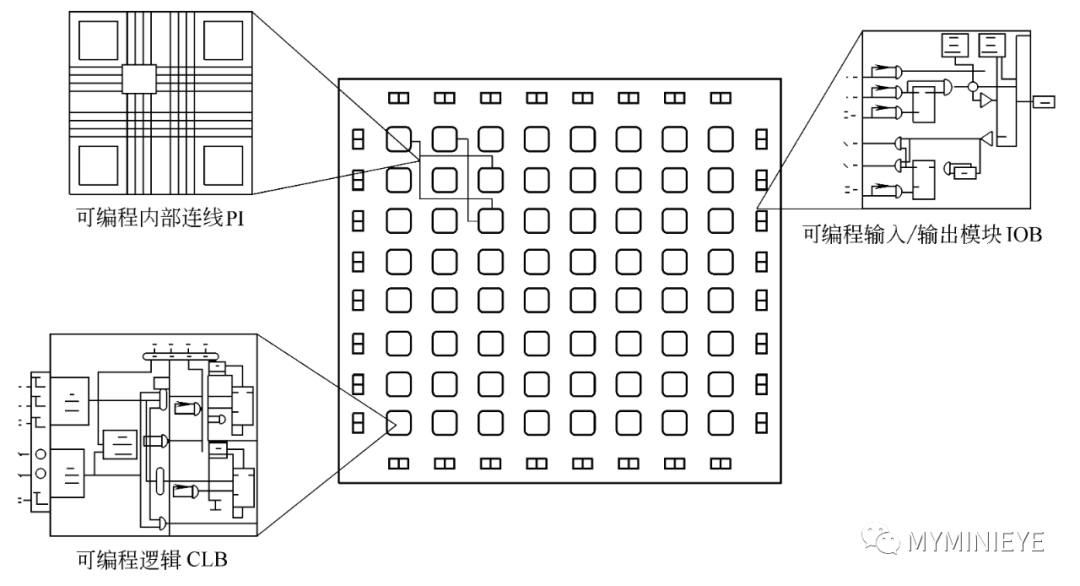

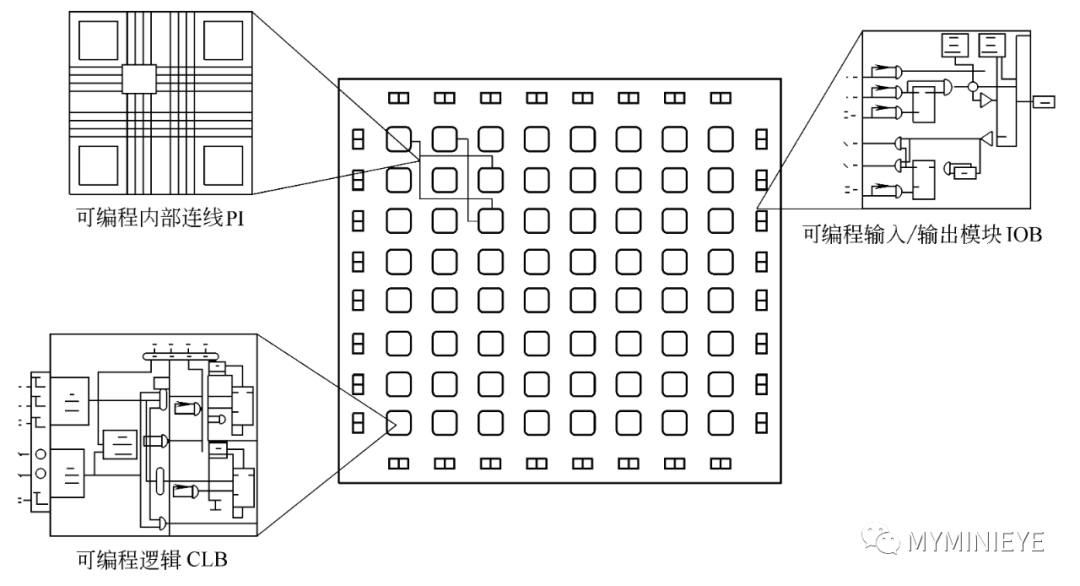

,SliceM还可以配置为分布式RAM和分布式ROM。 下面以Xilinx的ZYNQ的7000系列为例介绍其功能与结构 ZYNQ7000系列采用了Xilinx全新的第四代ASMBL架构

2020-11-02 17:18:05 5016

5016

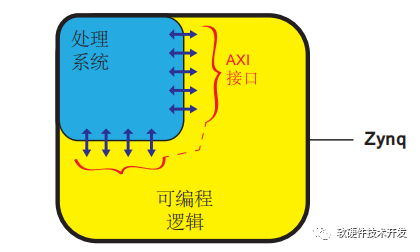

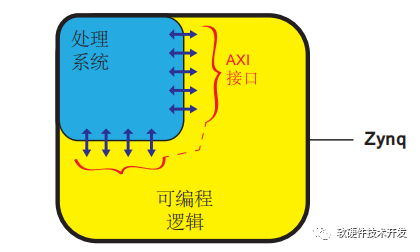

Zynq器件将arm和FPGA结合,利用了两者各自的优势,arm可以实现灵活的控制,而FPGA部分可以实现算法加速,这大大扩展了zynq的应用。比如深度学习加速,图像处理等等。PL侧表示FPGA

2020-11-30 11:56:01 3490

3490

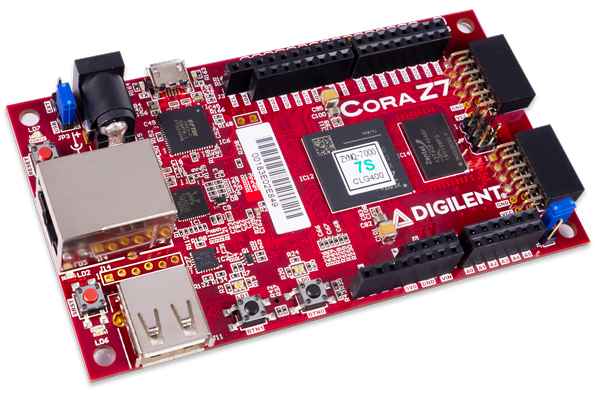

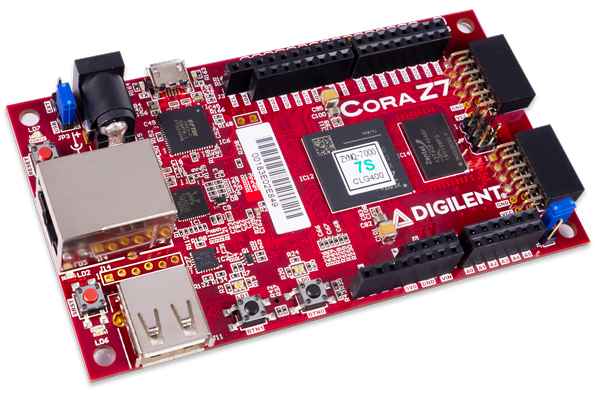

的开发。 1. 实例图片 下面是ZYNQ系列与PYNQ系列中两款具有代表性的开发板: ZYNQ系列——ZYNQ7000 PYNQ系列

2020-12-25 14:15:48 5212

5212 一、ZYNQ基本结构 ZYNQ7000系列分为 Artix-7 Kintex-7 Virtex-7,各个型号区别参考下面的博文 https://www.jianshu.com

2021-05-12 10:25:31 13960

13960

ZYNQ-7000的USB转JTAG驱动无法使用 使用操作系统是win7 64位 有人遇到过这个问题吗?

2013-07-10 22:06:48

Xilinx7系列内部自带一个双通道12位分辨率的高速(1MSPS 1M sample per second)采样速率的模拟混合信号处理模块,双通道的ADC支持单极和差分工作模式,最多支持17路外部

2019-09-10 10:27:36

ZYNQ7000搭建嵌入式Linux操作系统-增加PL端外设一、VIVADO工程建立二、VIVADO工程设置虚拟机下生成内核和uboot.elfSDK生成设备树和BOOT.bin一、VIVADO工程

2021-12-17 06:42:06

上,也可以通过 EMIO 连接到 PL 端的引脚。Zynq-7000 系列芯片一般有 54 个 MIO,个别芯片如 7z007s 只有 32 个。GPIO 是英文“general purpose I

2022-02-08 07:27:16

真随机数发生器在安全解决方案中起着重要作用。真正的随机数发生器通常由平台支持,例如Exynos 5,OMAP 3,4 SoC系列和飞思卡尔i.MX53。我已经阅读了zynq-7000的TRM,但没有找到随机数生成器。 zynq真的不支持RNG吗?

2020-07-17 14:27:09

与内置于 TE0720 系列 Trenz Electronic SoM(采用 Zynq Z-7014S 和 Zynq Z-7020 器件)中的 FPGA 容量相比,集成到 TE0723-03M

2018-08-31 14:43:05

Zynq-7000是什么?Zynq-7000能干什么?有何作用?

2021-06-30 06:22:55

你好, 我试图通过使用XADC读取模拟信号。我有Zynq-7000板。我找不到引脚分配文件。要将模拟信号输入到从vaux0到vaux15的16个通道,我应该如何与XADC接头建立输入连接? 非常感谢。 :)

2020-05-07 08:15:58

我正在使用Zynq-7000,选择欲望频率,我知道我应该使用-g ConfigRate,但这些设置数字是什么意思?例如,默认数字是3,这意味着频率是300KHz?谢谢

2020-08-05 13:14:33

`Zynq7000 SoC开发套件:开创全新的产品设计领域 Zynq-7000 SoC简介(来自Xilinx网站)Zynq™-7000系列器件将处理器的软件可编程能力与 FPGA 的硬件可编程能力

2013-01-28 14:36:33

坛友们,谁用过Zynq7000的处理,交流一些问题!

2017-08-14 20:53:12

最近从LINUX中拆出来一个CAN驱动,结果是不断总线错误(stuff error和Form error)下面说具体情况: 使用的是zynq7000,CAN1。与其对测的板子是335xs。已经确认

2016-05-26 21:33:28

® 7010 SoC/FPGAs (out of the Zynq® 7000 series family of products). This design showcases TPS65218

2015-03-10 15:15:21

UG865是关于ZYNQ7000封装和引脚排列。在表1-5中,方向cloumn上有'N / A'标记。以上来自于谷歌翻译以下为原文The UG865 is about ZYNQ7000

2019-04-17 09:44:36

CPUCPU为Xilinx Zynq-7000SOC,兼容XC7Z035/XC7Z045/XC7Z100,平台升级能力强,以下为Xilinx Zynq-7000特性参数:TLZ7xH-EasyEVM

2022-01-03 07:50:21

CPUCPU为Xilinx Zynq-7000SOC,兼容XC7Z035/XC7Z045/XC7Z100,平台升级能力强,以下为Xilinx Zynq-7000特性参数:电源接口和开关采用12V3A

2021-12-30 07:55:37

描述PMP10601 参考设计提供为 Xilinx® Zynq® 7000 系列 (XC7Z015) FPGA供电时所需的所有电源轨。此设计使用多个 LMZ3 系列模块、多个 LDO 和一个 DDR

2018-07-13 03:11:34

® Zynq® 7000 series (XC7Z045)FPGA.This design uses several LMZ3 series modules, LDOs, and a DDR

2018-11-05 16:42:31

Xilinx-ZYNQ7000系列-学习笔记(3):系统复位与启动一、复位ZYNQ-7000 SoC系统中的复位可以由硬件、看门狗定时器、JTAG控制器或软件产生,可用于驱动系统中每个模块的复位信号

2022-01-25 06:49:13

Xilinx-ZYNQ7000系列-学习笔记(3):系统复位与启动一、复位ZYNQ-7000 SoC系统中的复位可以由硬件、看门狗定时器、JTAG控制器或软件产生,可用于驱动系统中每个模块的复位信号

2022-01-25 07:05:36

`描述PMP10600.2 参考设计提供为 Xilinx® Zynq® 7000 系列 (XC7Z015) FPGA 供电时所需的所有电源轨。此设计使用多个 LMZ3 系列模块、多个 LDO 和一个

2015-05-08 16:17:26

`描述PMP10601 参考设计提供为 Xilinx® Zynq® 7000 系列 (XC7Z015) FPGA 供电时所需的所有电源轨。此设计使用多个 LMZ3 系列模块、多个 LDO 和一个

2015-05-08 16:08:58

描述 PMP10601 参考设计提供为 Xilinx® Zynq® 7000 系列 (XC7Z015) FPGA供电时所需的所有电源轨。此设计使用多个 LMZ3 系列模块、多个 LDO 和一个

2022-09-28 06:24:34

描述此 PMP10600.1参考设计提供为 Xilinx® Zynq® 7000 系列 (XC7Z015) FPGA供电时所需的所有电源轨。此设计使用多个 LMZ3 系列模块、多个 LDO 和一个

2022-09-23 07:43:32

各位大神好,最近在学习xilinx公司的ZYNQ7000系列的开发板,学习XADC,有没有用过的大神,求给一些学习指导。真不太会用啊!

2020-03-24 05:35:10

传统的ARM处理器类似。Zynq7000支持从多种设备启动,包括Jtag, NAND, parallel NOR, Serial NOR (Quad-SPI), 以及SD卡。按手册说明除了Jtag之外

2015-07-22 20:42:50

做一遍也不害怕!Zynq7000,是一个可扩展处理平台,简单说就是有个FPGA做外设的A9双核处理器。所以,它的启动流程自然也和FPGA完全不同,而与传统的ARM处理器类似。Zynq7000支持从多种设备

2015-05-27 20:50:06

视频太大了,无法上传,直接分享百度网盘了介绍一下内容【黑金ZYNQ7000系列原创视频教程】20.Linux下的GPIO操作【黑金ZYNQ7000系列原创视频教程】19.Linux下的hello

2016-11-14 21:04:04

最近在研究zynq7000系列的开发板,上面带有两个12位的XADC,有没有用过的大神给些学习的指导,要是能有小例子就更好啦,谢谢大家了

2016-05-04 15:21:51

在zynq7000上使用rtt,来移植SD卡驱动和文件系统,出现问题

2022-03-30 13:45:02

有一块zynq7000的板子,想在上面实现把从一个以太网口接收的数据,从另一个以太网口发出去的功能~~小白不知道该怎么入手。求资料~~求指导

2018-05-14 18:50:54

可实现重要分析与硬件加速,同时还在单个器件上高度集成 CPU、DSP、ASSP 以及混合信号功能。Zynq-7000 系列包括单核 Zynq-7000S 器件和双核 Zynq-7000 器件,是单位功耗

2018-06-07 15:36:43

描述该参考设计是一种可扩展的电源设计,旨在为基于 FPGA 的 Artix-7、Spartan-7 和 Zynq-7000 系列器件供电。此设计接收来自标准直流电源的电力,并通过明确的 Samtec

2019-01-03 13:47:48

嗨,大家好,是否有“白痴指南”如何为第三方设置Zynq 7000系列进行边界扫描?我有一个测试工作,但我得到间歇性的测试结果取决于Zynq在其启动过程中的位置。我的希望是将Zynq置于一个“自由切换

2019-04-17 08:56:32

如何使用Windows在Zynq 7000主板上启动linux?在Linux中我有终端可以请你建议是否有任何Windows终端以上来自于谷歌翻译以下为原文How can I boot linux

2019-04-09 13:12:21

如何使用vivado仿真zynq7000ov5640程序呢?麻烦各位大哥给个思路,如何模拟摄像头的时序和数据呢?

2022-08-29 09:37:46

如何实现Xilinx Zynq-7000嵌入式系统设计?

2021-12-23 08:53:58

想把鸿蒙系统移植到zynq7000和zynqMP平台上,网上没有找到一点资料,对于一直一头雾水,不知道怎么入手。请问大家,有做过移植吗?

2022-10-20 17:02:15

Layout设计逐渐成为主流,本系列文章同时包含有两部分内容且进行融合,欢迎大家持续关注,关注微信公众号“硬件开发不完全攻略”。 本次更新内容主要讲述如何通过Zynq 7000在Vivado下的工程文件评估芯片的各路电源功耗(电流),电源功耗(电流)评估对于电源选型、电源平面设计、电源完整仿真评估等都有很重...

2021-11-11 06:43:44

嗨,我是Zynq7000和嵌入式系统设计的新手。目前,我正在启动一个需要在Xilinx Zynq7000上构建嵌入式系统的项目。除了音频处理之外,我将使用蓝牙适配器与移动设备进行交互作为主要功能。我

2019-03-18 15:04:05

求xilinx_Zynq7000的学习资料,相关的xilinx学习资料也可以,本人有Altera的资料,有需要的请讲

2019-01-29 06:35:20

想让FX3的UART口和Xilinx ZYNQ7000的PS(Processor system)端的内置UART相互通信,两个芯片使用的是同一个电源(同在一块板子上或分别在两块相互连接的板子上),请教一下它们之间的硬件连接需要TTL电平转换(使用2块MAX3232ESE芯片,如下图所示)么?谢谢

2024-02-28 08:32:43

我用zynq7000板子,需要用到ucos系统,但是需要支持zynq的bsp的ucos库文件,需要下载,没有账号,下载不了,谁能帮忙下载,或者借账号用一下

2016-12-07 10:29:28

的可扩展处理平台(EPP), 赛灵思在今年3月发布了基于Zynq -7000新系列的首批器件。 采用28 nm制造工艺, Zynq-7000嵌入式处理平台系列的每款产品均采用带有NEON及双精度浮点引擎

2019-05-16 10:44:42

Zynq-7000系列中的 4 款产品具有完全相同的 ARM 处理系统,但是可编程逻辑资源的可扩展性有所不同, 因而适用于不同的应用。

2011-03-09 09:29:23 1612

1612 今天,赛灵思 Zynq-7000 SoC 和 Zynq UltraScale+ MPSoC 迎来一个新的产品系列及三款最新器件! 新的产品系列被称为Zynq Z-7000S系列,三款新器件分别为

2017-02-08 04:25:13 517

517

详细介绍zynq7000系列板子的资料,适合初学者借鉴学习。

2017-02-28 15:12:57 9

9 本文将介绍如何利用Vivado和petalinux开发Zynq7000系列芯片的SPI外设接口。

2017-03-20 14:00:25 3707

3707

ZYNQ7000与传统FPGA有着巨大的差异,它将自己定位为一款All Programmable Soc(软硬件可编程片上系统),视其为以FPGA作为外设的双核ARM A9处理器更加准切。它的启动

2017-11-17 16:04:37 7989

7989 以2个Cortex A9的ARM核为核心,还包括片上存储器、片外存储器接口(DDR)和一系列的外设接口。Zynq-7000系列将ARM CPU和外设集成在一个芯片内,使得Zynq-7000系列皆具处理器和FPGA双重特性,特别适用于软硬件协同设计。

2017-11-18 05:11:01 18880

18880

Xilinx公司的Zynq-7000系列是基于Xilinx全编程的系统级芯片(SoC)架构,集成了功能丰富的双核或单核ARM Cortex-A9处理系统(PS)和28nm Xilinx可编程逻辑

2018-04-17 02:27:00 3214

3214

赛灵思隆重推出Zynq-7000

2018-06-06 03:45:00 3874

3874

Xilinx Zynq-7000 EPP Showcased at Embedded World

2018-06-04 13:46:00 2881

2881 Xilinx Zynq™-7000

2018-06-04 13:47:00 3392

3392 本讲座是:赛灵思All Programmable SoC- Zynq 7000系列再度发力-处理性能。

2018-06-04 13:47:00 3828

3828

Zynq-7000 Extensible Processing Platform in Action

2018-05-24 16:47:00 3013

3013 观看世界上第一个可扩展处理平台--Zynq-7000 EPP的演示。

2019-01-02 09:31:00 2062

2062 Zynq-7000全可编程SoC提供无与伦比的性能和功能

2019-01-21 07:32:00 3212

3212 通过Zynq-7000 AP SoC了解电源管理技术,并了解Zynq Power Demonstration的这些技术。

2018-11-22 06:54:00 3500

3500 Zynq7000系列基于Xilinx全可编程SoC架构。这些产品在单个设备中集成了功能丰富的双核ARM®Cortex™-A9处理系统(PS)和28 nm Xilinx可编程逻辑(PL)。ARM Cortex-A9 CPU是PS的核心,还包括片上存储器、外部存储器接口和一组丰富的外围连接接口。

2019-02-12 16:07:28 4

4 Zynq7000系列引脚的分类是确定的,而各类引脚的数目则因芯片封装的不同而不同,(为了便于理解,本文所列引脚数目皆以XQ7Z045 FFG900封装为例,文章其他部分不再做出说明)其主要类型如下。

2019-02-14 17:12:37 2404

2404 本文档的主要内容详细介绍的是Zynq-7000全可编程SOC系列产品选择指南免费下载。

2019-02-15 11:52:09 9

9 ®Cortex™-A9处理器与业界领先的每瓦28nm可编程逻辑性能相集成,实现了超过离散处理器和FPGA系统的功率和性能水平。Zynq-7000系列提供了Dualcore(Zynq-7000设备

2019-02-15 11:52:14 20

20 防御级Zynq-7000q系列基于Xilinx SoC架构。这些产品将功能丰富的双核ARM Cortex™-A9处理系统(PS)和28 nm Xilinx可编程逻辑(PL)集成到单个设备中,用于

2019-02-22 16:16:39 10

10 由 ZYNQ7035 + 4 个 DDR3 + eMMC + QSPI FLASH 的最小系统构成。 ZYNQ7035 采用 Xilinx 公司的 Zynq7000 系列的芯片,型号为 XC7Z035-2FFG676。

2019-06-24 08:00:00 111

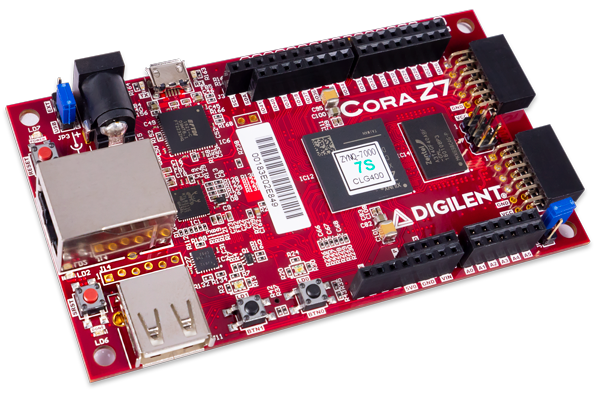

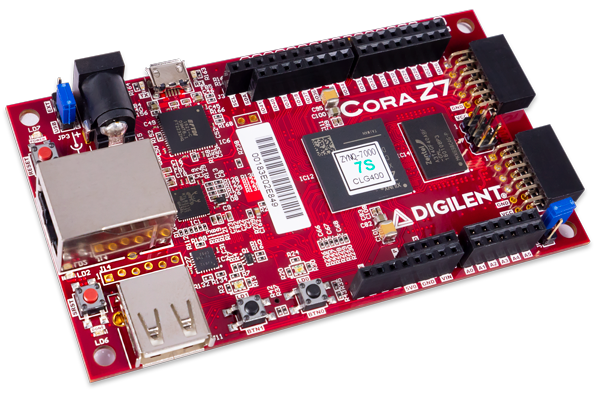

111 Digilent Cora Z7是一款随时可用,低成本且易于嵌入的开发平台,围绕Xilinx功能强大的Zynq-7000全可编程片上系统(APSoC)而设计。 Zynq-7000架构将单核

2019-11-14 15:53:23 2148

2148

Digilent Cora Z7是一款随时可用,低成本且易于嵌入的开发平台,围绕Xilinx功能强大的Zynq-7000全可编程片上系统(APSoC)而设计。 Zynq-7000架构将单核

2019-11-14 15:50:53 1795

1795

Zybo(Zynq™ Board)是一款资源丰富且易用的嵌入式软件及数字电路入门级开发平台,该平台主芯片为Xilinx Zynq-7000系列中的最小型号Z-7010。

2019-11-25 11:42:27 1363

1363

FPGA 开发平台采用核心板加扩展板的模式,方便用户对核心板的二次开发利用。核心板使用 XILINX 的 Zynq7000 SOC 芯片 XC7Z035 的解决方案,它采用 ARM+FPGA SOC 技术

2020-10-22 08:00:00 39

39 zynq-7000 SoC产品选型指南

2020-12-09 16:15:01 12

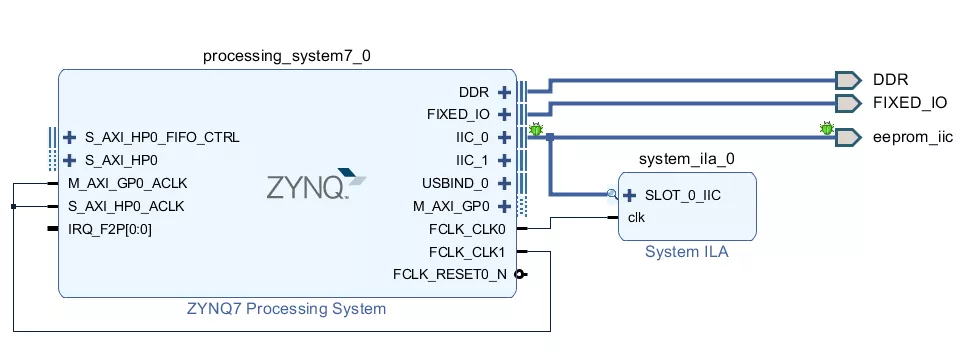

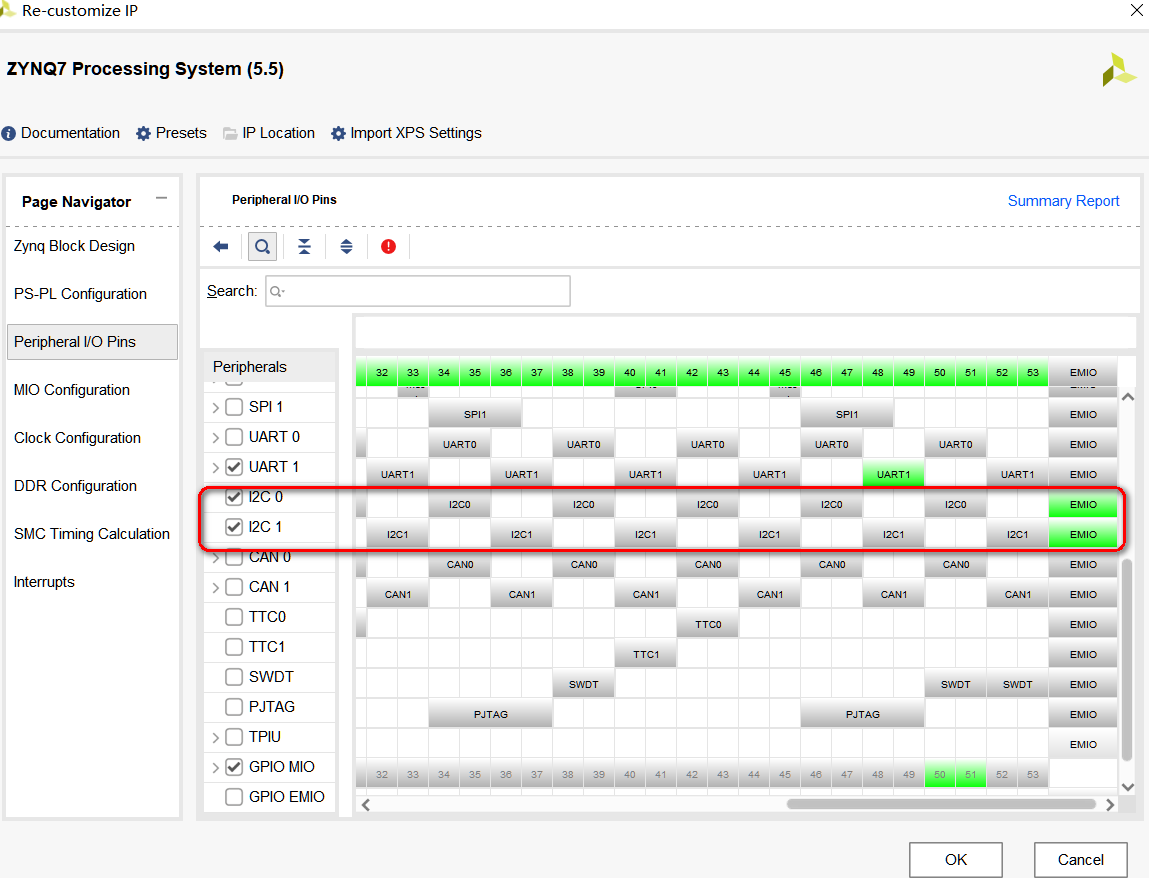

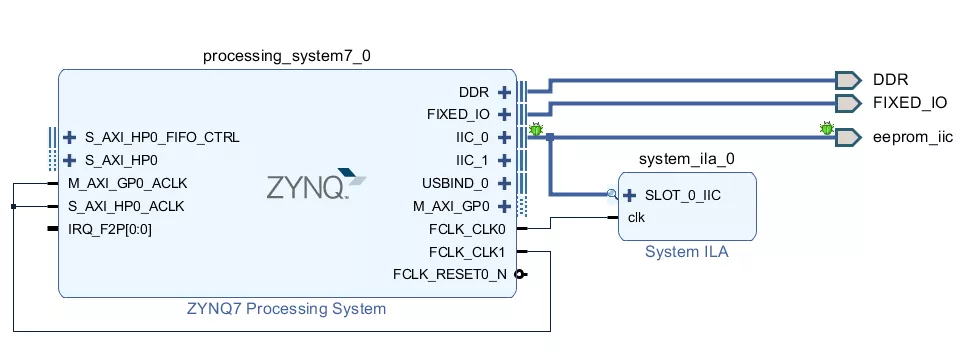

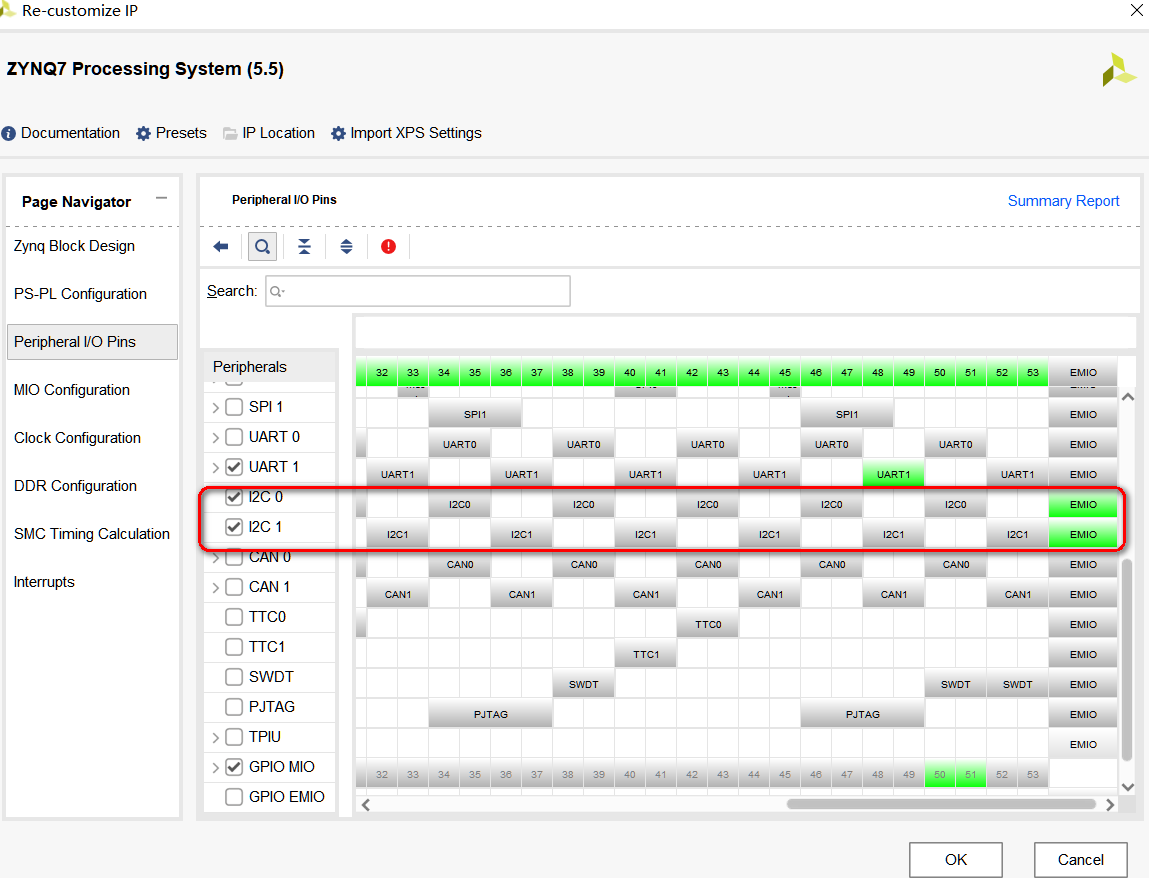

12 ZYNQ7000系列FPGA的PS自带两个IIC接口,接口PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35);SDK

2022-07-25 17:56:52 1404

1404

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2022-07-25 17:41:58 2046

2046

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2021-01-31 06:50:04 12

12 Xilinx_Vivado_zynq7000入门笔记说明。

2021-04-08 11:48:02 70

70 Zynq-7000 SoC数据手册下载

2021-05-21 15:22:41 28

28 上,也可以通过 EMIO 连接到 PL 端的引脚。Zynq-7000 系列芯片一般有 54 个 MIO,个别芯片如 7z007s 只有 32 个。GPIO 是英文“general purpose I/O”的缩写,即通用的输入/输出。是 ZYNQ PS 中的一个外设,用于观测和控制器件引脚的状态。图 1

2021-12-04 18:51:06 16

16 Zynq 7000系列的设计参考书中文版

2021-12-17 17:08:20 0

0 ZYNQ7000 SOC 芯片可以从 FLASH 启动,也可以从 SD 卡里启动, 本节介绍程序 FLASH 启动的方法。Zynq7000 SOC 芯片上电后,最先运行的是ARM端系统(PS

2022-05-07 09:41:35 5019

5019 电子发烧友网站提供《为Xilinx Zynq 7000系列FPGA供电所需电源轨的参考设计.zip》资料免费下载

2022-09-07 09:59:24 3

3 电子发烧友网站提供《Xilinx Zynq 7000系列(XC7Z015)电源解决方案.zip》资料免费下载

2022-09-08 09:20:52 10

10 本文介绍了Xilinx Zynq-7000系列XC7Z035/XC7Z045系列主要特性,资源框图及PS端ETH RJ45接口引脚说明

2022-11-21 09:17:10 3049

3049

Zynq-7000系列芯片的逻辑资源(PL)是不同的,Z-7020以下是基于A7 FPGA的,Z-7030以上是基于K7的,资源数量有所不同。而我们使用的Zedboard是Z-7020的。

2022-12-22 09:44:09 1493

1493 ZYNQ 芯片分为 PL 和 PS, PS 端的 IO 分配相对是固定的,不能任意分配,虽然 PS 端的 ARM 是硬核,但是在 ZYNQ 当中也要将 ARM 硬核添加到工程当中才能使用,FPGA

2023-08-11 09:36:34 4805

4805

对于软硬件技术开发人员,ZYNQ是比较好的入门级FPGA,你可以在FPGA上用verilog编写RTL代码,也可以在ARM中用C语言编写应用程序。而入手一块低成本的开发板则是你开启软硬件技术开发的一条捷径。

2023-09-06 11:00:45 620

620

电子发烧友网站提供《Zynq-7000 SoC:嵌入式设计教程.pdf》资料免费下载

2023-09-13 09:20:03 3

3

正在加载...

电子发烧友App

电子发烧友App

评论