ASIC和FPGA具有不同的价值主张,在作出选择前必须仔细评估。两种种技术对比。这里介绍了ASIC和FPGA 的优势与劣势。

2011-03-31 17:30:09 5382

5382

基于 FPGA 的 ASIC 原型可快速、准确地实现 SoC 系统建模和验证并加速软件和固件的开发。Xilinx 推出Virtex®-7 2000T 器件,使基于 FPGA 的原型得到了进一步发展

2013-03-14 14:33:00 1269

1269

什么是FPGA原型? FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能

2022-07-19 16:27:29 1735

1735 FPGA原型在数字芯片设计中非常重要,因为相比用仿真器,或者加速器等来跑仿真,FPGA的运行速度,更接近真实芯片,可以配合软件开发者来进行底层软件的开发。这一流片前的软硬件的协同开发,是其最不可替代的地方。

2023-05-10 10:44:00 4791

4791

国微思尔芯发布3亿门原型验证系统,采用业界最高容量的 Intel® Stratix® 10 GX 10M FPGAs。

2020-09-08 10:56:20 883

883 与Virtex-6 FPGA相比,Virtex-7系列的系统性能翻了一番、功耗降低一半、速度提升30%、其重点在于容量扩大2.5倍、多达200万个逻辑单元、串行宽带达1.9Tbps、线速高达28Gbps、其

2012-09-21 13:46:16

原型验证---用软件的方法来发现硬件的问题 在芯片tap-out之前,通常都会计算一下风险,例如存在一些的严重错误可能性。通常要某个人签字来确认是否去生产。这是一个艰难的决定。ASIC的产品NRE

2019-07-11 08:19:24

` 本帖最后由 wangjiamin2014 于 2014-7-24 11:21 编辑

事实上,工业市场是一个庞大的市场,任何一款主控芯片都无法完全将其覆盖。就工业应用领域而言,FPGA凭借

2014-07-24 11:18:05

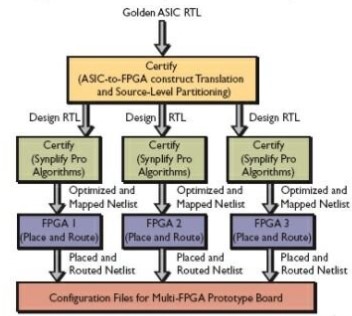

原型验证过程中的ASIC到FPGA的代码是怎样进行转换的?

2021-05-08 09:16:18

。 ASIC在离开生产线后再也无法改变。这就是为什么设计师在大规模量产之前需要完全确保设计正确无误。工程师可以利用FPGA的可重配置这一优势,进行ASIC的原型验证,以便在将设计发送到代工厂之前,可以在

2020-12-01 17:41:49

...................................................493.1 Vertex-7 FPGA 资源与架构

2015-09-18 15:26:25

ASIC设计-FPGA原型验证

2020-03-19 16:15:49

的设计流程(数字芯片)包括:功能描述、模块划分、模块编码输入、模块级仿真验证、系统集成和系统仿真验证、综合、STA(静态时序分析)、形式验证。(FPGA 和 ASIC 设计流程)插一句,在 ASIC

2020-09-25 11:34:41

、系统集成和系统仿真验证、综合、STA(静态时序分析)、形式验证。插一句,在ASIC 设计过程中,往往要用到FPGA 进行原型验证。FPGA 验证是进行ASIC 设计的重要环节,其后,还需要引入ASIC

2017-09-02 22:24:53

130 万,所以最大系统门数为170 万。结论:FPGA 等效门数估计方法可以是把FPGA 资源基本单元(如LUT+FF,ESB)和实现相同功能的标准门阵列相比得到FPGA 基本单元等效的门数,然后

2012-03-01 10:08:53

Tape Out并回片后都可以进行驱动和应用的开发。目前ASIC的设计变得越来越大,越来越复杂,单片FPGA已不能满足原型验证要求,多片FPGA验证应运而生。本文我就将与大家探讨FPGA原型验证的几个经典挑战性场景,(具体应对的办法,请戳原文。)容量限制和性能要求

2020-08-21 05:00:12

扩展性较好,可以通过增加芯片数量或使用更大容量的芯片来满足更高的性能需求。而ASIC的可扩展性相对较差,需要重新设计和制造。

验证和调试 :FPGA的验证和调试过程相对简单,可以在系统级进行仿真和测试。而

2024-02-22 09:54:36

for IOBs: 23,7606. 等效门数的意义(1). 等效门数是对ASIC实现的大概估计。这里包含了两个意思:一呢是对ASIC实现的估计,也就是说ASIC实现的时候是在168万门左右的数量级;二

2018-08-17 09:44:25

以上”.此话的含意是:日隈介绍“集成同等规模的电路(400万个逻辑门以及8MbitRAM)时,130nm工艺ASIC芯片与40nm工艺FPGA芯片的面积几乎相等”.如此说来,如果将FPGA微细化到

2012-11-20 20:09:57

节点以上”.此话的含意是:日隈介绍“集成同等规模的电路(400万个逻辑门以及8MbitRAM)时,130nm工艺ASIC芯片与40nm工艺FPGA芯片的面积几乎相等”.如此说来,如果将FPGA微细化到

2012-11-07 20:25:53

ASIC是一种为专门目的而设计的集成电路,是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。ASIC的特点是面向特定用户的需求,亮点在于运行速度在同等条件下比FPGA快。FPGA作为

2017-06-12 15:56:59

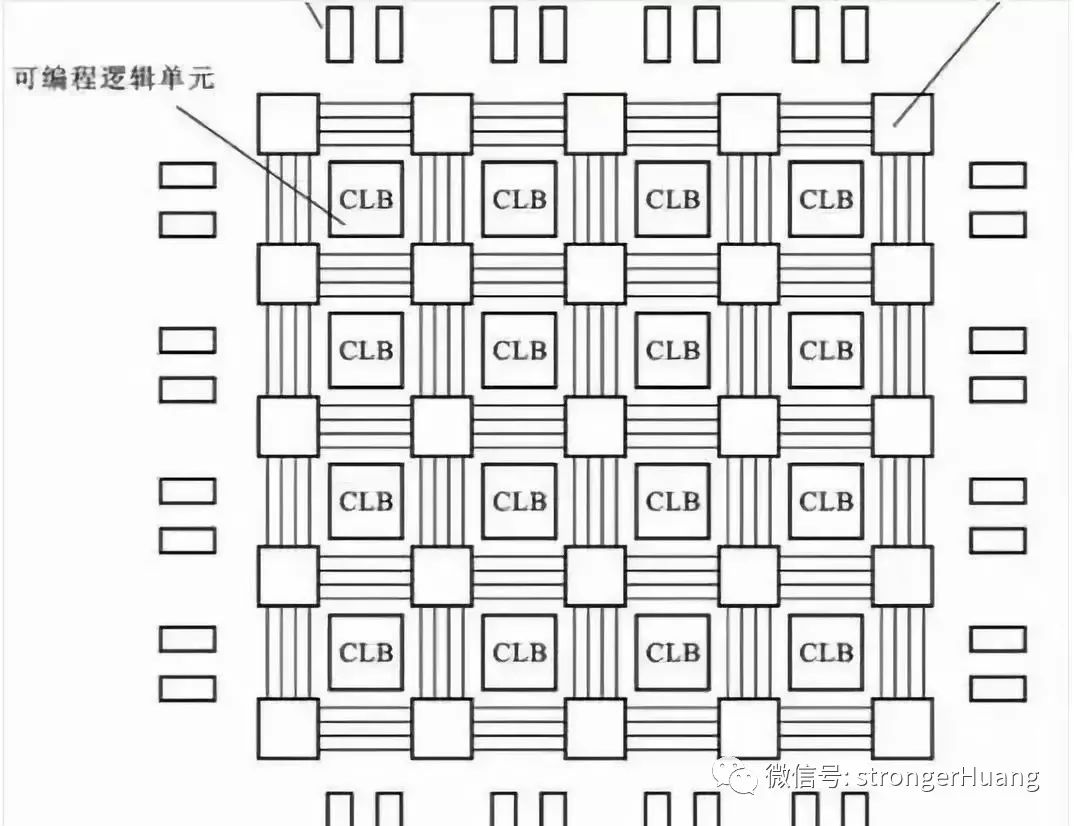

`FPGA代表现场可编程门阵列,它是一种半导体逻辑芯片,可编程成几乎任何类型的系统或数字电路,类似于PLD。PLD仅限于数百个门,但FPGA支持数千个门。FPGA架构的配置通常使用语言来指定,即

2018-12-14 17:39:44

FPGA/ASIC高性能数字系统设计 状态机与数据路径 1 有限状态机 1.1 基本概念 1.2 状态机分类 1.3 状态机描述方法 1.4 状态机的编码风格 1.5 可综合的fsm编码 1.6

2011-03-02 09:35:30

FPGA原型板提供Altera Cyclone 5CEA7 FPGA,MPS2+FPGA原型板提供Altera Cyclone 5CEA9 FPGA,速度均为C8级。

这两个主板都支持ARM

2023-08-18 07:25:28

HAPS(高性能ASIC原型设计系统)是一款基于FPGA的高性能、高容量ASIC原型设计和仿真系统。HAPS是一种模块化的系统,采用多个FPGA主板以及标准或定制子板,可以多种方式叠加。标准子板

2018-11-20 15:49:49

Virtex 7 PCIe硬IP是否意味着FPGA内部的ASIC?或者像Tandem方法一样,在第一阶段,CPLD将PCIe初始配置加载到FPGA? (http://www.em.avnet.com

2020-05-29 12:52:09

Block)和内部连线(Interconnect)三个部分。FPGA的基本特点主要有: 1)采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片。 2)FPGA可做其它全定制或半

2012-02-27 17:46:03

系统,可以用高达16个V5FPGA来进行ASIC原型校验。在其最高的配置中,它能够被用于32,000,000 ASIC门的原型设计。而这个板子的上一代DN8000K10,在ASIC校验部分使用了16片

2012-02-15 19:40:17

[导读]什么是FPGA,单片机,DSP,ASIC?你真的知道吗?ASIC原本就是专门为某一项功能开发的专用集成芯片,比如你看摄像头里面的芯片,小小的一片,集成度很低,成本很低,可是够用了。一个山寨

2021-07-16 08:13:27

高性能CPU,下至简单的74系列电路,都可以用FPGA来实现。FPGA如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由设计一个数字系统。通过软件仿真,我们可以事先

2009-10-05 16:32:12

在 FPGA、GPU 或 ASIC 控制的系统板上,仅有为数不多的几种电源管理相关的设计挑战,但是由于需要反复调试,所以这类挑战可能使系统的推出时间严重滞后。

2019-10-09 06:21:11

在 FPGA、GPU 或 ASIC 控制的系统板上,仅有为数不多的几种电源管理相关的设计挑战,但是由于需要反复调试,所以这类挑战可能使系统的推出时间严重滞后。

2019-09-30 06:59:24

从ASIC到FPGA的转换系统时钟设计方案

2011-03-02 09:37:37

最优解。这或许也是为什么深鉴在FPGA原型开发完成之后,还付出了大量努力才能完成真正ASIC设计的原因。 FPGA原型验证: 食之无味,弃之可惜? 传统意义上,FPGA出现的一个重要因素是为了给

2023-03-28 11:14:04

和图像处理、车载、航空航天和国防、ASIC原型开发、测试测量、存储、数据安全、医疗电子、高性能计算以及各种定制设计中都有涉猎。总而言之,FPGA所诞生并发展的时代是一个好时代,与身俱来的一些特性也注定了它将会在这个时代的大舞台上大放光彩。 ``

2016-07-11 06:47:38

Programmable Gate Array,现场可编程门阵列。

FPGA这些年在行业里很火,势头比ASIC还猛,甚至被人称为“万能芯片”。

其实,简单来说,FPGA就是可以重构的芯片。它可以根据

2024-01-23 19:08:55

本部门所承担的FPGA设计任务主要是两方面的作用:系统的原型实现和ASIC的原型验证。

2012-06-16 10:55:33

前言 本部门所承担的FPGA设计任务主要是两方面的作用:系统的原型实现和ASIC的原型验证。编写本流程的目的是:l在于规范整个设计流程,实现开发的合理性、一致性、高效性。l形成风格良好和完整的文档

2017-12-08 14:47:15

华为FPGA设计流程指南本部门所承担的FPGA设计任务主要是两方面的作用:系统的原型实现和ASIC的原型验证。编写本流程的目的是:l在于规范整个设计流程,实现开发的合理性、一致性、高效性。l形成

2017-12-18 10:45:03

采用基于现场可编程门阵列(FPGA)的原型的验证团队面临的最大挑战之一在于当原型系统未能发挥期望的性能时了解原型系统的内部行为。分析和调试这些设计的一个关键因素是难以观察内部信号。 目前的顶级

2019-07-12 06:38:15

吗?这就是DiNI公司的DN9000K10,这是一个USB 2.0主机逻辑原型系统,可以用高达16个V5FPGA来进行ASIC原型校验。在其最高的配置中,它能够被用于32,000,000 ASIC门

2012-10-21 22:02:22

我的设计完全在Verilog中,并且已经使用Spartan FPGA进行了测试。我将源代码提供给ASIC工厂,以实现作为ASIC使用他们(我认为)的概要工具。我的问题是,有没有办法使用任何

2019-07-25 13:44:31

ASIC验证能够采用的主要技术是什么?如何利用现成FPGA开发板进行ASIC原型开发?

2021-05-08 07:51:04

你好。我是在FPGA上设计系统的初学者。我的fpga是XC7K325T -2 FFG900(knitex - 7系列)我想计算基本15位2输入加法器的逻辑延迟。如果我能检查AND门或OR门的延迟等

2020-05-25 07:28:24

FPGA在嵌入式系统中的优势有哪些?如何通过LabVIEW FPGA加速嵌入式系统原型化?

2021-05-06 07:42:56

的设计和验证的复杂性需求。随着原型技术在设计分割以及多 FPGA 联 合调试领域的进步,基于FPGA 的原型系统不仅可以满足百万门级的设计需求,还可以实现设计规模高达15 亿门。基 于FPGA

2018-08-07 09:41:23

嗨,我找不到每个顶点-5系列FPGA支持多少个门。你能告诉我如何计算吗?因为对于我的应用程序,我需要选择支持150000门的设备。如何在Vertex-5系列中选择合适的FPGARegardsNanda Kumar M.

2020-06-15 08:49:47

用基于现场可编程门阵列(FPGA)的原型的验证团队面临的最大挑战之一在于当原型系统未能发挥期望的性能时了解原型系统的内部行为。分析和调试这些设计的一个关键因素是难以观察内部信号。 目前的顶级

2020-07-07 09:08:34

扩大软件使用这一趋势对ASIC与SoC原型设计技术和总设计过程有何影响呢?

2021-04-08 06:14:35

扩展了旗下 16 纳米 (nm)Virtex® UltraScale+™ 产品系列。VU19P拥有 350 亿个晶体管,有史以来单颗芯片最高逻辑密度和最大I/O 数量,用以支持未来最先进 ASIC 和 SoC 技术的仿真与原型设计,同时,也将广泛支持测试测量、计算、网络、航空航天和国防等相关应用。

2020-11-02 08:34:50

FPGA、ASIC、GPU 和微处理器以及采用这些及其他数字组件的系统之要求。利用经过验证的电源管理解决方案设计电源管理电路,将确保项目从一开始就很有把握。这是让设计方案从原型阶段快速进入生产阶段的关键

2018-10-15 10:30:31

失败的原因不是时序或者功率的问题,而是逻辑或功能错误。为此,功能验证已经成为ASIC开发周期中一个最关键的环节,通常最耗费时间。越来越多的ASIC设计人员发现通过采用FPGA进行功能原型设计能够最好

2019-07-15 07:00:39

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法。本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。1、RFID芯片的FPGA

2019-05-29 08:03:31

描述XC7A50T-1FGG484C基于最先进的、高性能、低功耗(HPL)、28nm、高k金属门(HKMG)工艺技术,以2.9Tb/s的I/O带宽、200万个逻辑单元容量和5.3TMAC/sDSP

2022-08-03 16:23:43

Xilinx®7系列FPGA包括四个FPGA系列,可满足整个系统要求,包括低成本,小尺寸,成本敏感的大批量应用程序,可满足最苛刻的超高端连接带宽,逻辑容量和信号处理能力高性能的应用程序。7系列

2022-11-10 15:11:11

FPGA 原型设计人员艰苦努力所得的明显回报就是 ASIC* 设计可以及时而毫无问题地完成产品定案(tape-out)。不过,原型设计还有一点日益重要的优势,即 ASIC 或 SoC 中嵌入的软件在项目

2010-01-18 08:35:09 18

18 FPGA原型验证和其他验证方法是不同的,任何一种其他验证方法都是ASIC验证中的一个环节,而FPGA验证却是一个过程。由于FPGA与ASIC在结构、性能上各不相同,ASIC是基于标准单元库,FPGA用的

2010-09-10 17:22:26 989

989 HAPS-600系列以高达8100万ASIC门的容量为各种基于FPGA的更大型的原型验证项目提供高灵活性和可扩展性。

2011-03-21 10:28:38 824

824 电子系统设计人员使用FPGA来实现他们的原型开发,利用器件的可编程能力验证硬件和软件。一旦设计准备好进行量产时,设计人员寻找某类ASIC以达到功耗、性能和成本目标,特别是,

2011-03-24 10:21:48 98

98 对ASIC设计进行FPGA原型验证时,由于物理结构不同,ASIC的代码必须进行一定的转换后才能作为FPGA的输入。 现代集成电路设计中,芯片的规模和复杂度正呈指数增加。尤其在ASIC设计流程中

2011-03-25 15:16:20 108

108 S2C公司发表最大容量SoC/ASIC原型系统,Quad S4 TAI Logic Module 能够容纳高达3,280万闸的设计并且拥有 S2C 第4代原型系统的所有优点

2011-04-26 09:40:00 952

952 5月14日,泰克公司宣布,将在2013设计自动化大会上展出其最新推出的Certus 2.0 ASIC原型调试解决方案。与基于RTL嵌入式仪器一起,帮助实现完整的RTL级可视性使FPGA内部可视成原型平台。

2013-05-14 11:36:18 765

765 顾名思义,proFPGA 的 Ultra-Scale™ XCVU440 FPGA 模块基于赛灵思 Virtex® UltraScale VU440,而且该原型板的额定容量高达 3000

2017-02-08 12:12:11 343

343 加速 RTI 前的软件开发。 基于 FPGA 的原型设计,提供精确的周期、较高的执行效率和连接到外部的实际接口。 Synopsys 的混合原型解决方案将虚拟原型和基于 FPGA 的原型优势集于一身,加速了项目周期中软件开发和系统集成的进度。 借助 Synopsys 的混合原型验

2017-02-08 14:32:11 293

293 FPGA原型验证和其他验证方法是不同的,任何一种其他验证方法都是ASIC验证中的一个环节,而FPGA验证却是一个过程。

2017-02-11 12:46:11 2975

2975 ASIC设计在尺寸和复杂性上不断增加,现代FPGA的容量和性能的新进展意味着这些设计中的2/3能够使用单个FPGA进行建模。

2017-02-11 16:26:11 795

795

)440 FPGA的Quad VU440 Prodigy Logic Module。Quad VU440 Prodigy LM是由单板组成的全用途FPGA原型系统,同时Quad VU440 LM的大量的物理互连线以及超大的逻辑容量特别适合超大规模设计,进而减轻了设计分割的负担。

2018-06-29 08:09:00 4932

4932 电子系统设计人员使用FPGA来实现他们的原型开发,利用器件的可编程能力验证硬件和软件。一旦设计准备好进行量产时,设计人员寻找某类ASIC以达到功耗、性能和成本目标,特别是,能够提供硬件平台和工具包的ASIC,支持目前采用了FPGA的设计

2017-10-14 10:18:11 4

4 门阵列(FPGA)做为安谋国际核心测试芯片,进而建构SoC原型制作平台。 验证SoC设计 FPGA原型最稳当 FPGA原型制作是在FPGA上实作SoC或特定应用集成电路(ASIC)设计的方法,并进行硬件验证和早期软件开发。

2018-05-11 09:07:00 2405

2405

ASIC设计在尺寸和复杂性上不断增加,现代FPGA的容量和性能的新进展意味着这些设计中的2/3能够使用单个FPGA进行建模。然而,这些设计中仍然保留有1/3(那就是说,所有ASIC

2017-11-25 09:05:02 924

924 新思科技(Synopsys, Inc.,纳斯达克股票市场代码:SNPS)日前宣布:推出全新HAPS-80基于FPGA的原型系统,该系统为Synopsys的端到端原型解决方案的一部分。HAPS-80

2018-07-10 10:42:00 2067

2067 近年来,ASIC设计规模的增大带来了前所未有的芯片原型验证问题,单颗大容量的FPGA通常已不足以容下千万门级、甚至上亿门级的逻辑设计。现今,将整个验证设计分割到多个采用最新工艺大容量FPGA中,FPGA通过高速总线互联,成为大规模ASIC或SOC原型验证的极佳选择。

2018-07-02 08:20:00 1695

1695 FPGA 原型设计人员艰苦努力所得的明显回报就是 ASIC 设计可以及时而毫无问题地完成产品定案(tape-out)。

2018-07-19 11:33:00 2150

2150 在不太遥远的过去,对ASIC设计团队而言,在这类情况下主要的解决方案就是在内部建立他们自己的定制多个FPGA的原型开发板。然而,今天,使用现成的多个FPGA原型开发板——例如,由Synplicity

2019-05-16 08:07:00 2742

2742

采用fpga原型技术验证asic设计,首先需要把asic设计转化为fpga设计。但asic是基于标准单元库,fpga则是基于查找表,asic和fpga物理结构上的不同,决定了asic代码需要一定

2019-07-23 08:07:00 1923

1923

FPGA是可编程ASIC。 ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

2018-12-15 09:58:46 5195

5195 ASIC芯片一旦流片功能就无法改变,基本专片专用。而FPGA可配置特性就可以应用在功能会改变的场合,例如,原型验证,ASIC设计过程中会使用到FPGA来进行原型验证;功能升级,在产品中采用FPGA实现一些业内暂时还没成熟的解决方案,可以在后续功能变动时方便升级。

2019-08-25 10:40:01 10934

10934

GX 10M FPGA的可插拔FPGA模块,其每个FPGA模块基于单颗FPGA,均拥有6000万个ASIC门的原型设计能力,使得四模块原型设计系统的仿真容量达到2.4 亿个ASIC门。多达九个这样

2019-12-06 15:09:14 2144

2144 FPGA vs. ASIC 你看好谁?

2020-01-15 16:10:22 4104

4104 以及ZYNQ 7020模组。XCVU13P主器件具有极其丰富的FPGA可编程逻辑资源,提供了强悍的算法原型验证能力。同时平台板载的ZYNQ 7020器件可用于系统管理并增强系统的灵活性。该平台提供有

2020-05-19 10:50:05 2521

2521 Virtex UltraScale+ VU19P是赛灵思密度最高的FPGA,是ASIC和SOC原型验证的最佳选择。

2020-10-22 14:23:13 1385

1385 从系统的特性上看,FPGA 原型系统支持多FPGA、自动分割;性能较高的情况下运行系统软件;仿真加速器的超大容量可以放全芯片的设计,进行全芯片的系统功能/性能/功耗验证。

2022-05-25 09:35:13 7629

7629 FPGA要取代ASIC了,这是FPGA厂商喊了十多年的口号。可是,FPGA地盘占了不少,ASIC也依旧玩得愉快。那么,这两位仁兄到底有啥不一样呢?

2023-03-31 14:41:41 1138

1138

FPGA原型验证在数字SoC系统项目当中已经非常普遍且非常重要,但对于一个SoC的项目而言,选择合适的FPGA原型验证系统显的格外重要

2023-04-03 09:46:45 928

928 FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 多片FPGA原型验证系统的拓扑连接方式各不相同,理想的多片FPGA原型验证系统应该可以灵活配置,可以使用其相应的EDA工具

2023-05-08 11:51:40 326

326

多片FPGA的原型验证系统的性能和容量通常受到FPGA间连接的限制。FPGA中有大量的资源,但IO引脚的数量受封装技术的限制,通常只有1000个左右的用户IO引脚。

2023-05-23 17:12:35 1149

1149

ASIC设计在尺寸和复杂性上不断增加,现代FPGA的容量和性能的新进展意味着这些设计中的2/3能够使用单个FPGA进行建模。然而,这些设计中仍然保留有1/3(那就是说,所有ASIC

2023-06-04 16:50:01 699

699 FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2024-01-12 16:13:01 220

220

正在加载...

电子发烧友App

电子发烧友App

硬声App

硬声App

5382

5382 1269

1269

1735

1735 4791

4791

883

883

评论